(54) ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ СБРОСА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство приведения триггера в исходное состояние | 1983 |

|

SU1091345A1 |

| Формирователь импульсов сброса | 1986 |

|

SU1359903A1 |

| Формирователь импульсов сброса | 1978 |

|

SU739739A1 |

| ИСТОЧНИК ПИТАНИЯ НЕЛИНЕЙНОЙ ИЛИ ЛИНЕЙНОЙ НАГРУЗКИ | 2021 |

|

RU2768272C1 |

| Высоковольтный транзисторный переключатель | 1988 |

|

SU1637018A1 |

| Высоковольтный транзисторный переключатель | 1990 |

|

SU1734203A1 |

| Стабилизатор постоянного напряжения | 1977 |

|

SU741252A2 |

| Формирователь высоковольтных прямоугольных импульсов | 1982 |

|

SU1075390A1 |

| Стабилизированный инвертор | 1981 |

|

SU964908A1 |

| РЕЛЕ ВРЕМЕНИ (С ВЫХОДОМ НА СИМИСТОРЕ) | 1992 |

|

RU2130213C1 |

Изобретение относится к импульсной технике и может быть использовано в цифровой аппаратуре, в которой недопустима неправильная работа из-за помех по цепи питания н предпочтительно повторение рабочего цикла с исходного состЬяння.

Известен формирователь импульсов сброса при- вкдюченни источников питания, содержащий входной элемент И-НЕ, один вход которого соединен со входом устройства, а другой через параллельно включенные резистор и конденсатор с общей шиной. Выход входного элемента И--НЕ через резистор соединен с запускающим конденсатором и одним из входов выходного элемента И- НЕ, другой вход которого подключен ко входу устройства. Выход выходного элемента соединен с выходом устройства н через конденсатор с резистором и входом элемента И-НЕ обратной связи, выход которого через диод подключен ко входу выходного элемента И-НЕ, соединённого с запускающим конденсатором I.

Недостаток данного устройства состоит в том, что при кратковременном провале напряжения пнтання ниже допустимого уровня устройство не формнрует импульса

сброса, что сужает функциональные возможности.

Наиболее близким к изобретению по технической сущности является формирователь импульсов сброса, содержащий времязадающнй конденсатор, подключенный одним выводом к общей шине, и ключевой транзистор, включенный по схеме с общнм эмиттером, коллектор которого подключен через инвертор к щине выходных сигналов, а база подсбединена через резнстор к эмиттеру и через последовательно соединенные ста10билитрон н резистор, к шине питания 2.

Недостатком известного устройстпа является то, что при кратковременном провале напряжения питания ниже допустимого уровня устройство не формирует .импульса сброса.

15

Цель изобретения - формирование нмпульса сброса полноценной длительиостн при кратковременных провалах напряжения питания.

Для достижения цели в формирователь импульсов сброса, содержащий времяза30дающий конденсатор, подключенный одним выводом к общей шине, н ключевой транзистор, включенный по схеме с общим эмнттером, коллектор которого подключен через инвертор к шине выходных сигналов, а база подсоединена через резистор к эмиттеру и через последовательно соединенные стабилитрон и резистор к шине питания, введены три дополнительных транзистора, диод и резисторы, при этом второй вывод время задаюш.его конденсатора подключен к эмиттеру первого дополнительного транзистора, соединенного коллектором с катодом стабилитрона, а базой подключенн.ого через резистор к шине питания и непосредственно к коллектору второго дополнительного транзистора, и через резистор к коллектору третьего дополнительного транзистора, причем выход инвертора подключен через последовательно соединенные диод и резйстивные делители к базам второго и третьего дополнительных транзисторов, эмиттеры которых подключены к обш,ей шине.

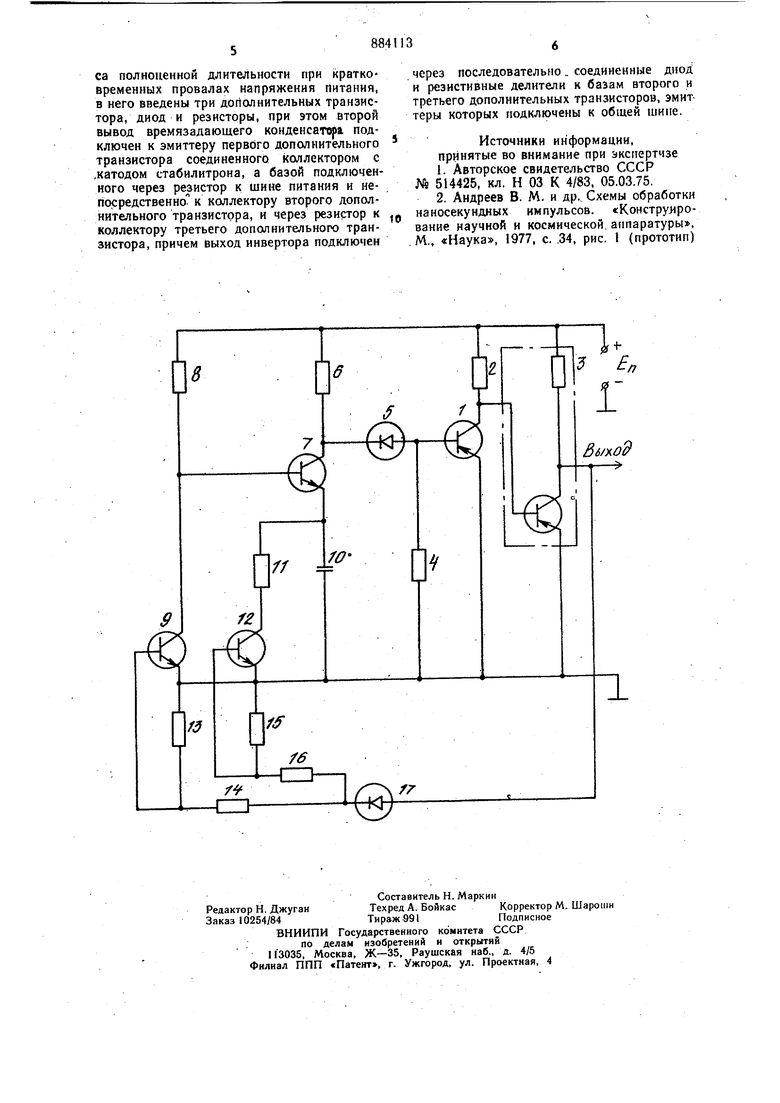

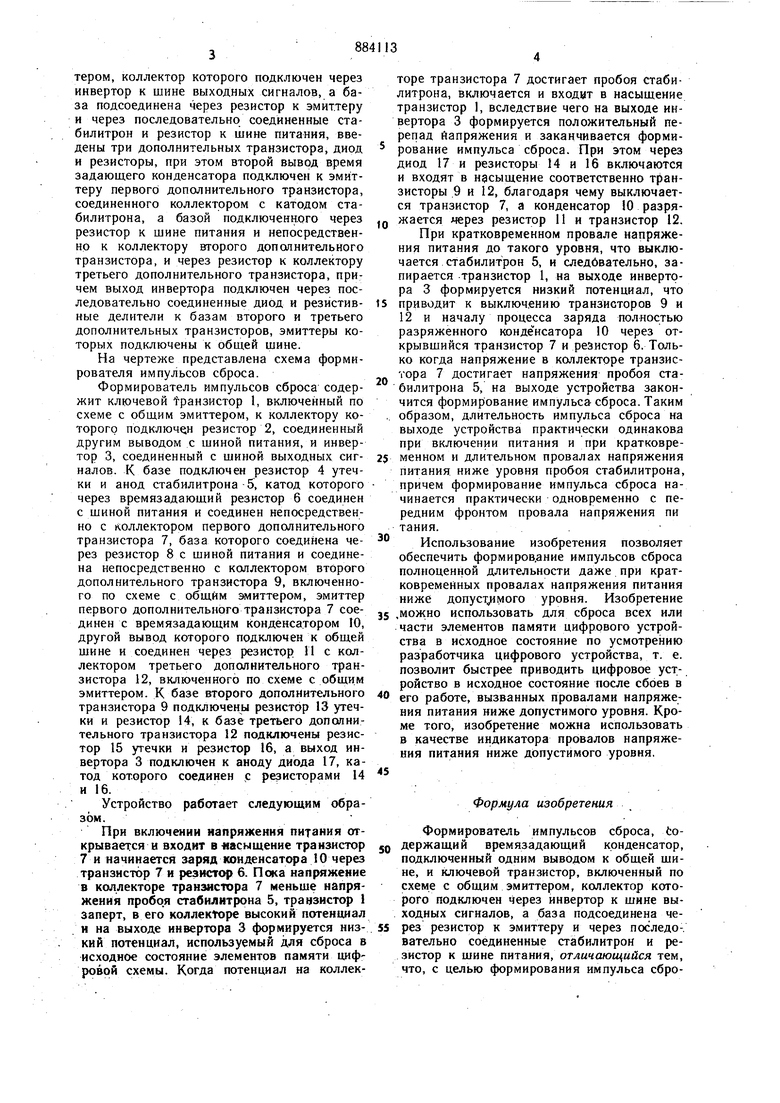

На чертеже представлена схема формирователя импульсов сброса.

Формирователь импульсов сброса содержит ключевой tpaH3HCTOp 1, включенный по схеме с общим эмиттером, к коллектору которого подключен резистор 2, соединенный другим выводом с шиной питания, и инвертор 3, соединенный с шиной выходных сигналов. К базе подключен резистор 4 утечки и анод стабилитрона 5, катод которого через времязадаюший резистор б соединен с шиной питания и соединен непосредственно с коллектором первого дополнительного транзистора 7, база которого соединена через резистор 8 с шиной питания и соединена непосредственно с коллектором второго дополнительного транзистора 9, включенного по схеме с общим эмиттером, эмиттер первого дополнительного транзистора 7 соединен с времязадающим конденсатором 10, другой вывод которого подключен к общей шине и соединен через резистор И с коллектором третьего дополнительного транзистора 12, включенного по схеме с общим эмиттером. К базе второго дополнительного транзистора 9 подключены резистор 13 утечки и резистор 14, к базё третьего дополнительного транзистора 12 подключены резистор 15 утечки и резистор 16, а выход инвертора 3 подключен к аноду диода 17, катод которого соединен ; резисторами 14 и 16.

Устройство работает следующим образом.

При включении напряжения питания открывается и входит в насыщение транзистор 7 и начинается заряд «онденсатора 10 через транзистор 7 и резистор 6. Пока напряжение в коллекторе транзистора 7 меньше напряжения пробоя стабилитрона 5, транзистор 1 заперт, в его коллекторе высокий потенциал н на выходе инвертора 3 формируется низкий потенциал, используемый для сброса в исходное состояние элементов памяти цифровой схемы. Когда потенциал на коллекторе транзнстора 7 достигает пробоя стабилитрона, включается и входит в насыщение транзистор 1, вследствие чего на выходе инвертора 3 формируется положительный перепад йапряжения и заканчивается формирование импульса сброса. При этом через диод 17 и резисторы 14 и 16 включаются и входят в насыщение соответственно транзисторы 9 и 12, благодаря чему выключается транзистор 7, а конденсатор 10 разряжается через резистор II и транзистор 12. При кратковременном провале напряжения питания до такого уровня, что выключается стабилитрон 5, и следбвательно, запирается транзистор 1, на выходе инвертора 3 формируется низкий потенциал, что

приводит к выключению транзисторов 9 и 12 и началу процесса заряда полностью разряженного конденсатора 10 через открывшийся транзистор 7 и резистор 6. Только когда напряжение в коллекторе транзистора 7 достигает напряжения пробоя стабилитрона 5, на выходе устройства закончится формирование импульса сброса. Таким ,. образом, длительность импульса сброса на выходе устройства практически одинакова при включении питания и при кратковременном и длительном провалах напряжения питания ниже уровня пробоя стабилитрона, причем формирование импульса сброса начинается практически одновременно с передним фронтом провала напряжения пи тания..

Использование изобретения позволяет обеспечить формиров.ание импульсов сброса полноценной длительности даже при кратковременных провалах напряжения питания ниже допуст 1мого уровня. Изобретение

его работе, вызванных провалами напряжения питания ниже допустимого уровня. Кроме того, изобретение можна использовать в качестве индикатора провалов напряжения питания ниже допустимого уровня.

Формула изобретения

Формирователь импульсов сброса, to0 держащий времязадающий конденсатор, подключенный одним выводом к общей щине, и ключевой транзистор, включенный по схеме с общим эмиттером, коллектор которого подключен Через инвертор к шине выходных сигналов, а база подсоединена через резистор к эмиттеру и через последо-. вательно соединенные стабилитрон и ре.эистор к шине плтанкя, отличающийся тем, что, с целью формирования импульса сброса полноценной длительности при кратковременных провалах напряжения питання, в него введены три дополнительных транзистора, диод и резисторы, при этом второй вывод времязадающего конденса-пюа подключен к эмиттеру первого дополнительного транзистора соединенного коллектором с .катодом стабилитрона, а базой подключенного через резистор к шине питання и непосредственно к коллектору второго дополнительного транзистора, и через резистор к коллектору третьего допапнительного транзистора, причем выход инвертора подключен

через последовательно. соединенные диоД и резнстивные делители к базам второго и третьего дополнительных транзисторов, эмнт теры которых подключены к общей шипе.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-11-23—Публикация

1980-03-14—Подача