(54) ШИРОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Широтно-импульсное множительное устройство | 1980 |

|

SU868783A1 |

| Широтно-импульсное множительное устройство | 1980 |

|

SU934493A1 |

| Времяимпульсное множительное устройство | 1988 |

|

SU1642481A1 |

| Время-импульсное множительноеуСТРОйСТВО | 1979 |

|

SU805344A1 |

| ВРЕМЯ- ИМПУЛЬСНОЕ МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1969 |

|

SU253449A1 |

| Время-импульсное множительное устройство | 1981 |

|

SU1056215A1 |

| Электронный счетчик электроэнергии | 1979 |

|

SU866491A1 |

| Широтно-импульсное множительное устройство | 1973 |

|

SU492886A1 |

| Способ перемножения аналоговых сигналов (его варианты) | 1982 |

|

SU1116437A1 |

| Множительное устройство | 1981 |

|

SU955104A1 |

1

Изобретение относится к вычисли- : тельной технике и может быть использовано как блок перемножения.

Известны широтно-импульсные множительные устройства, в которых результат перемножения представляется в виде разности длительностей импульсов t П .

Основной недостаток указанных устройств состоит в их сложности.

Наиболее близким по технической сущности к предлагаемому является широтно-импульсное множительное устройство, которое содержит широтноимпульсный модулятор, состоящий из последовательно соединенных интегратора, ко входу которого подключен источник входного сигнала, и компаратора, ко входу которого подключен другой источник входного сигнала, второй KON napaTop, подключенный к выходу интегратора, и два ключа, управляемые выходным сигналом первого компаратора 23.

Недостатком известного устройства является невысокая точность перемножения . Погрешности в результатах перемножения сигналов в основном определяются тем, что переключение второго компаратора происходит не при переходе напряжения на выходе интегратора через ноль, так как реальные транзисторные ключи имеют остаточное напряжение.

10

Цель изобретения - повьшение точности перемножения входных сигналов.

Поставленная цель достигается тем, что в широтно-импульсиое множительное устройство, содержащее послеi«довательно соединенные интегратор и первый компаратор, выхбд которого подключен ко входу интегратора, вход интегратора является входом первого сомножителя устройства, первый вход

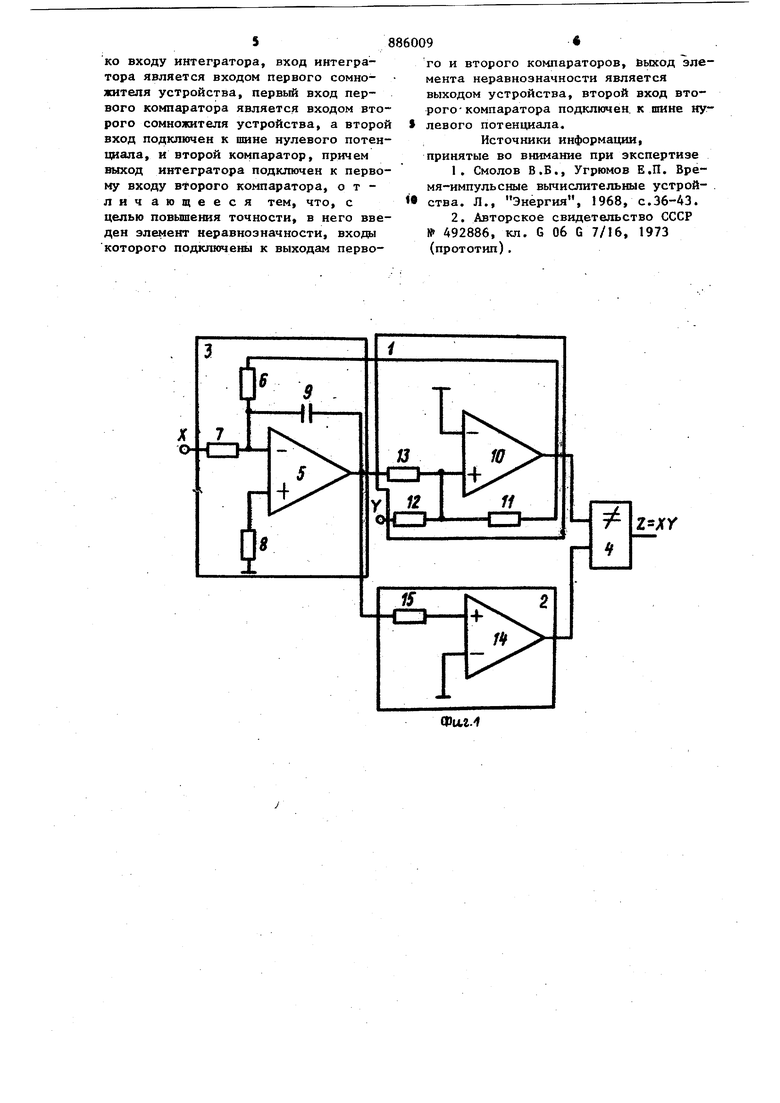

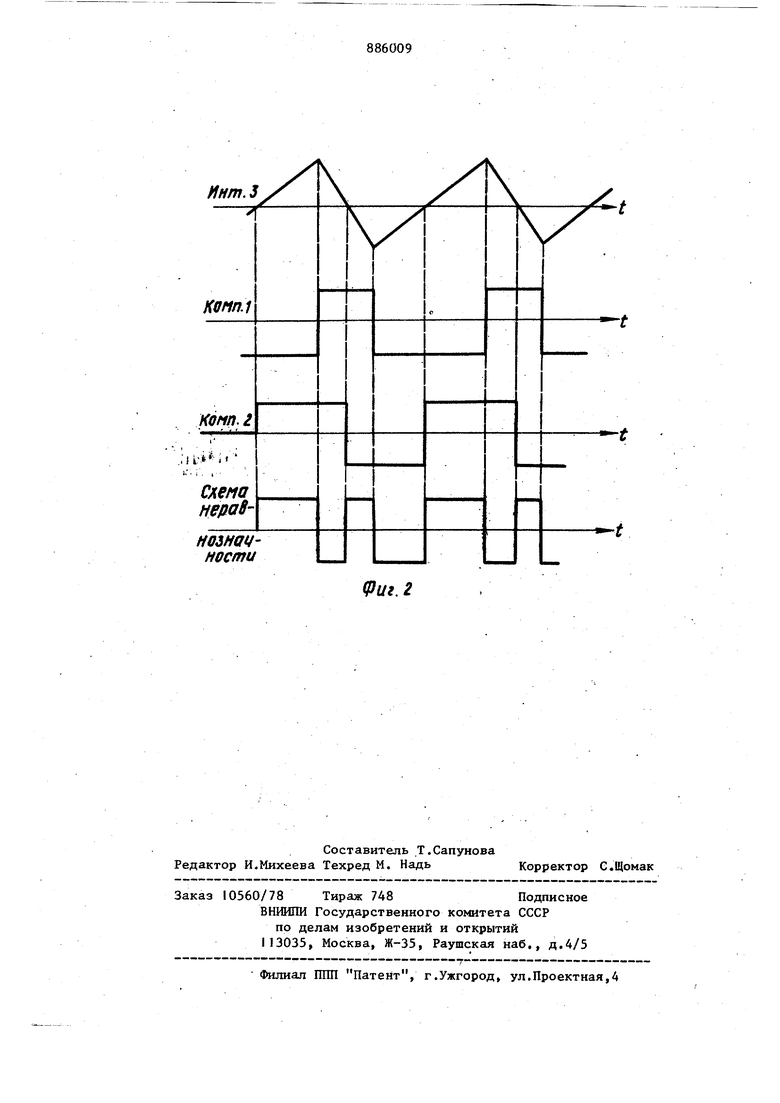

20 первого компаратора является входом второго сомножителя устройства, а второй вход подключен к шине нулевого потенциала, и второй компаратор. причем выход интегратора подключен первому входу второго компаратора, введен элемент неравнозначности,вход которого подключены к выходам первог и второго компараторов, выход элемен та неравнозначности является выходом устройства, второй вход второго компаратора подключен к шине нулевого потенциала. Элемент неравнозначности (или рав нозначности) формирует на выходе четыре разнополярных примыкающих импульса, относительная разность длительностей которых пропорциональна произведению входных сигналов, что исключает из схемы основной источник погрешностей - транзисторные ключи, На фиг,I приведена принципиальная схема широтно-импульсного множительного устройства, на фиг,2 - временные диаграммы его работы. Широтно-импульснов множительное устройство содержит компараторы 1 и интегратор 3 и элемент 4 неравнознач ности. Интегратор 3 содержит операционны усилитель 5, резисторы 6, 7 и 8 и конденсатор 9, первый компаратор содержит операционный усилитель 10 и резисторы 11, 12 и 13, второй компаратор содержит операционный усилител 14 н резистор 15. Множительное устройство работает следуняцим образом. При отсутствии входных сигналов интегратор 3 и компаратор 1 работают в автоколебательном режиме как релак са щонвый генератор. На выходе интег ратора 3 формируется симметричное пияообразное напряжение, а на выходе компаратора I - напряжение прямоугол ной формы. Компаратор 2 переключается при переходе через ноль напряжекмя на вьиоде интегратора 3, на его выходе также формируемся напряжение прямоугольной формы, Разнополярные импульсы с выходов компараторов 1 и 2 подаются на входы элемента 4 нерав нозначности, на выходе которой за период образуются две пары Чередующихся разнополярных импульсов. При отсутствии входных сигналов относительная разность длительностей импульсов на выходе элемента 4 неравнозначности равна нулю. Если на вход интегратора и компаратора подан входные сигналы X и У, то скорость :изменения напряжения на выходе иитег эра равна -:(U+x) при положительратораи -i (и-х) при отрицательном напряномжениях на выходе компаратора 1, пороги срабатывания компаратора 1 равны соответственно (Up+Y) и (Ujj-Y), где iu - напряжение на выходе компаратора 1, i и g - порог срабатывания компаратора 1, Т - постоянная времени интегратора 3. При наличии входных сигналов на выходе элемента 4 неравнозначности за период Т интегратора 3 образуются ч тыре прямоугольных импульса различной длительности. Длительности этих импульсов равны и+х fY.-f ygtY. ГУ, т- UfiiY , ч-т Определим относительную длительность положительных tC, и рицательных импульсов за период генерируемого напряжения ft W() tr,4t,4t:,4t 2yoU+2XY 2UoU-2XY Таким образом, относительная длительность разнополярных импульсов на выходе элемента 4 неравнозначности оказывается пропорциональной произведению входных сигналов. Так как погрешности прототипа в известном устройстве определяются тем, что переключения второго компаратора происходят при некотором уровне напряжения, обусловленном остаточным напряжением реальньк транзисторных ключей, а также прохохздением сигнала с выхода первого компаратора чеез управляющие входы ключей на входы торого компаратора, то исключение з схемы ключей и получение результаов- перемножения на выходе элемента еравнозначности повышает точность еремножения входных сигналов. Формула изобретения Широтно-импульсное множительное стройство, содержащее последовательо соединенные интегратор и первый омпаратор, выход которого подключен/

ко входу интегратора, вход интегратора является входом первого сомножителя устройства, первый вход первого компаратора является входом второго сомножителя устройства, а второй вход подключен к шине нулевого потенциала, и второй компаратор, причем выход интегратора подключен к первому входу второго компаратора, о т лич ающееся тем, что, с целью повышения точности, в него введен элемент неравнозначности, входы которого подключены к выходам первого и второго компараторов, &ыход элемента неравнозначности является выходом устройства, второй вход второго-компаратора подключен, к пшне нулевого потенциала.

Источники информации, принятые во внимание при экспертизе

7

l-XY

(риг. 2

Авторы

Даты

1981-11-30—Публикация

1980-02-18—Подача