Изобретение относится к аналоговой вычислительноГ технике.

Известно широтно-импульсное множительное устройство, содержащее широтно-импульсный модулятор, состоящий из последовательно соединенных интегратора и компаратора, дополнительный компаратор, выход которого является выходом устройства, ключи и источники первого и второго входных сигналов, выходцы которых соответственно подключены ко входу интегратора и к первому входу компаратора 1 .

Недостаток этого устройства низкая точность перемножения и сложность.

Наиболее близким по технической сущности к предлагаемому является множительное устройство, содержгидее источник первого входного сигнала, источник второго входного сигнала, широтно-импульсный модулятор, сое- . тоящий из последовательно соединенных интегратора и первого компаратора, выход которого подключен к первому входу интегратора, второй вход которого подключен к выходу источника первого входного сигнала че-. рез блок умножения на знак, второй

компаратор, первый вход которого подключен к выходу интегратора, а второй вход - к шине нулевого потенс циала 2.

Недостатком известного множительного устройства йвляется наличие norpemHOctH, обусловленной задержками переключения компараторов. При учете задержек переключения компараторов выражение для выходной величины множительного устройства принимает вид

Т5

JSI-

U Uo+|-((V +) TO о

где 9 - относительная разность длительностей разнополярных импульсов на выходе первого компаратора;

t - длительность отрицательного импульса; длительность положительного

импульса;

х,у - входные сигналы-сомножители;Up- порог срабатывания первого

компаратора;

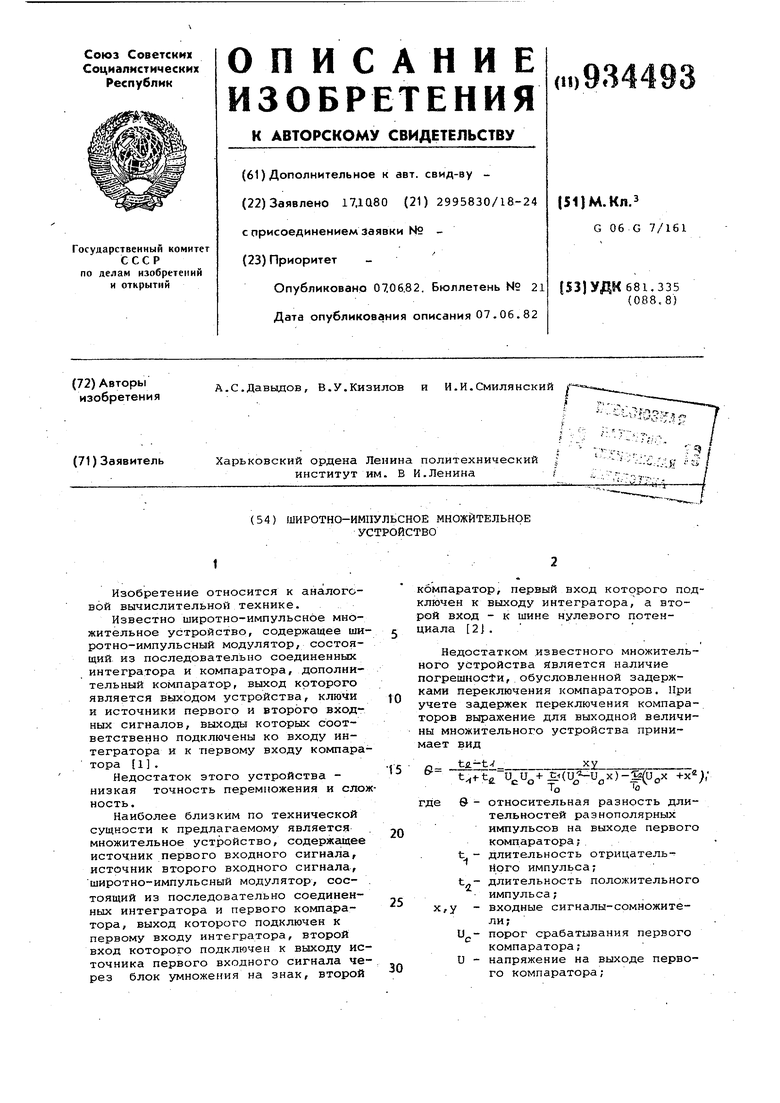

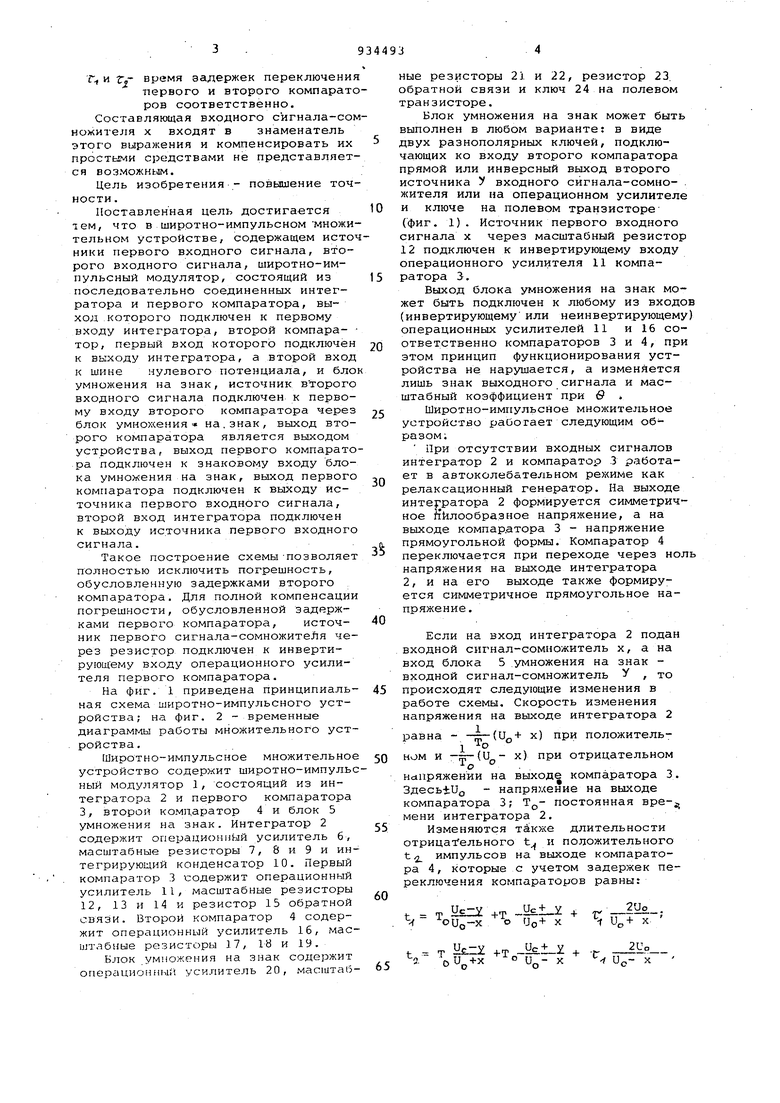

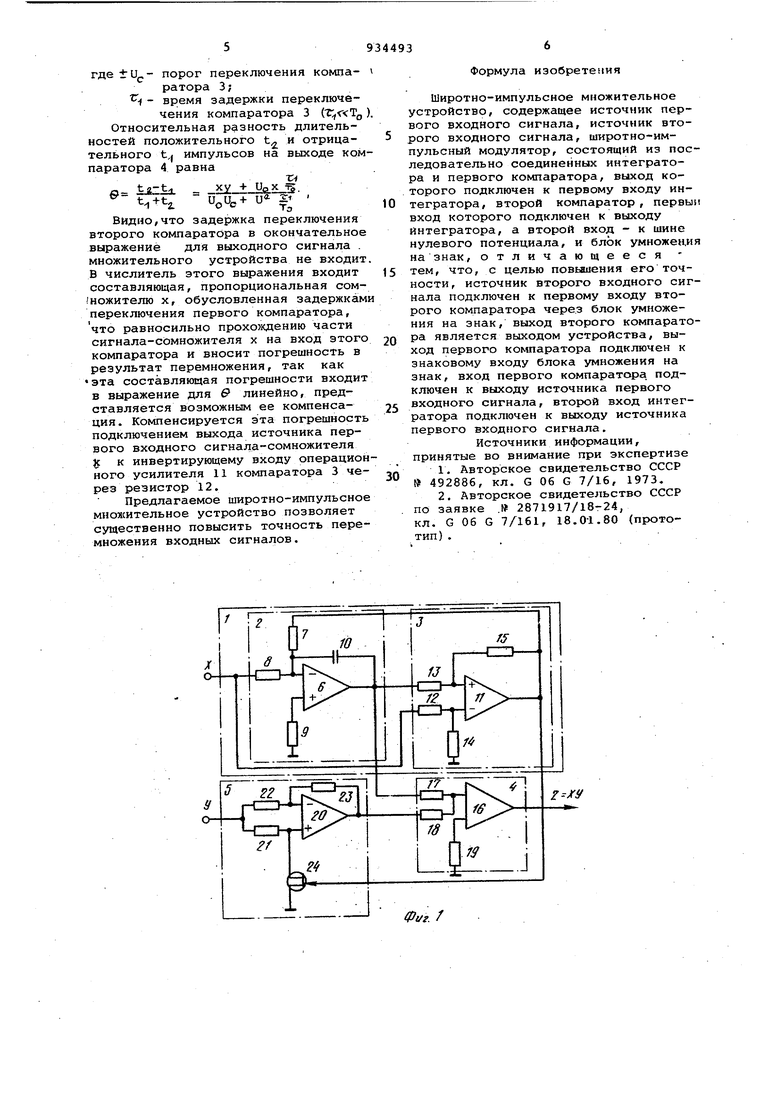

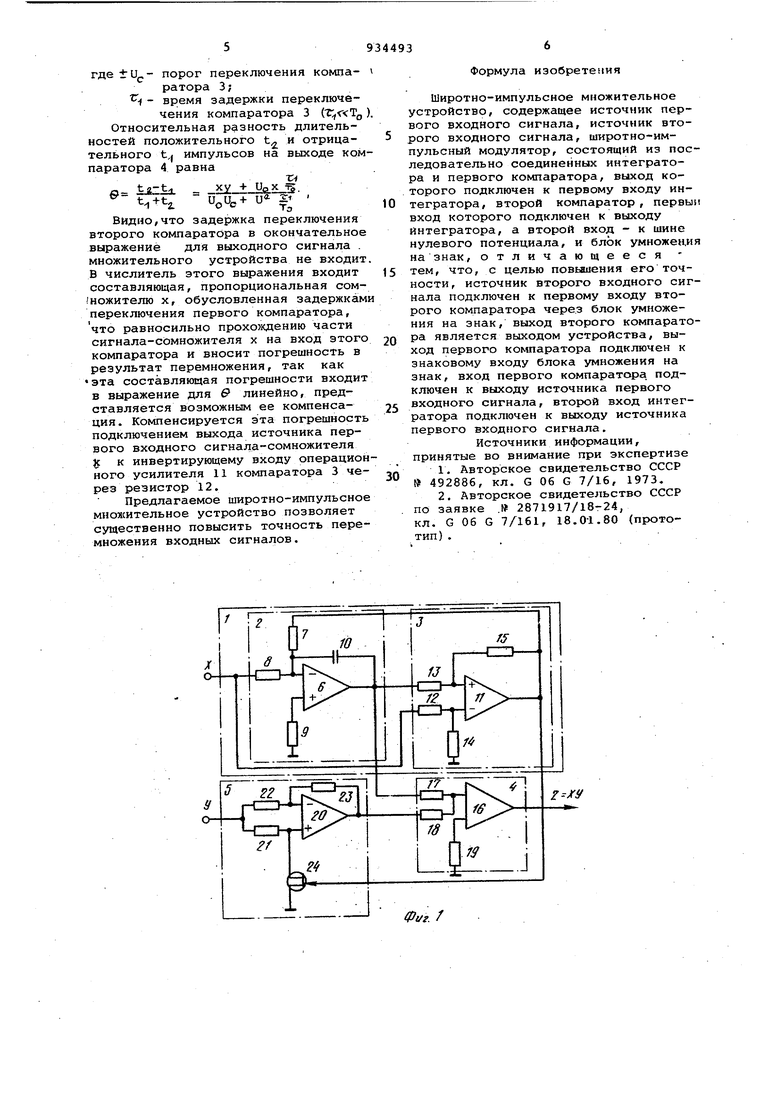

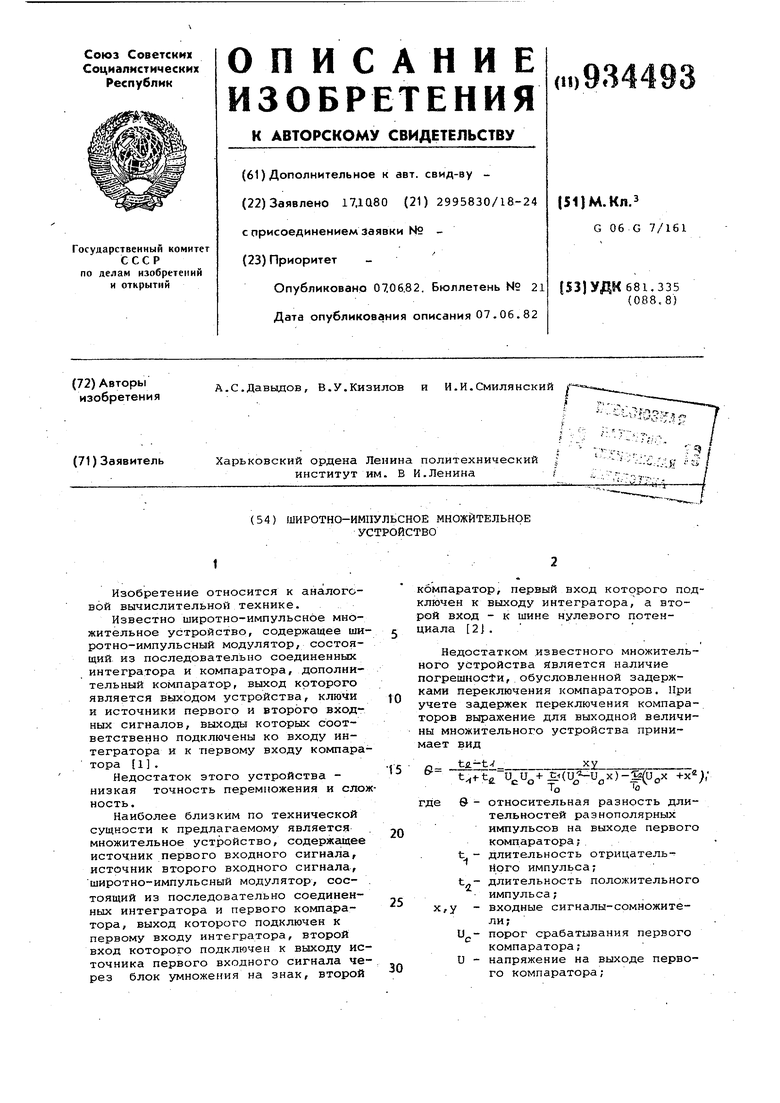

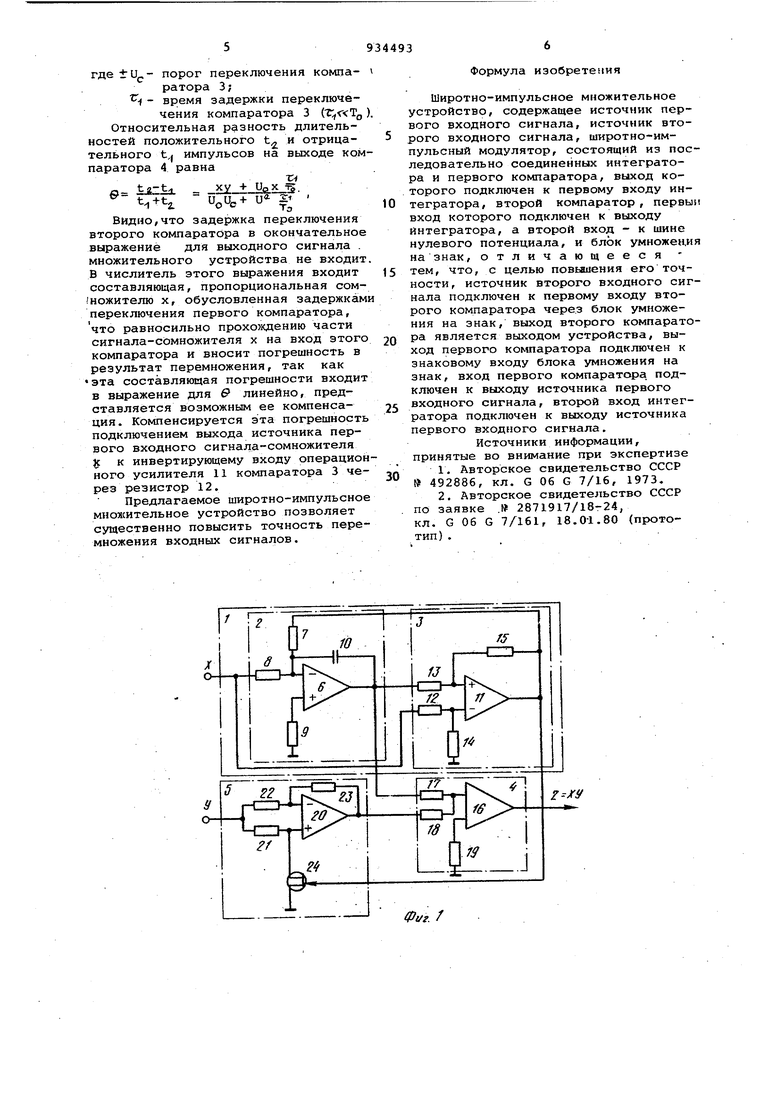

и - напряжение на выходе первого компаратора; Г и Г,- время задержек переключени первого и второго компарато ров соответственно. Составляющая входного сигнала-со ножителя X входят в знаменатель этого выражения и компенсировать их простьгии средствами не представляет ся возможньлм. Цель изобретения - повышение точ ности. Поставленная цель достигается тем, что в ширртно-импульсном множи тельном устройстве, содержащем исто ники первого входного сигнала, второго входного сигнала, широтно-импульсный модулятор, состоящий из последовательно соединенных интегратора и первого компаратора, выход которого подключен к первому входу интегратора, второй компаратор, первый вход которого подключен к выходу интегратора, а второй вход к шине нулевого потенциала, и бло умножения на знак, источник второго входного сигнала подключен к первому входу второго компаратора через блок умножения на,знак, выход второго компаратора является выходом устройства, выход первого компарато ра подключен к знаковому входу блока умножения на знак, выход первого компаратора подключен к выходу источника первого входного сигнала, второй вход интегратора подключен к выходу источника первого входного сигнала. Такое построение схемы позволяет полностью исключить погрешность, обусловленную задержками второго компаратора. Для полной компенсации погрешности, обусловленной задержками первого компаратора, источник первого сигнала-сомножитеЛя через резистор подключен к инвертирующему входу операционного усилителя первого компаратора. На фиг. 1 приведена принципиальная схема широтно-импульсного устройства; на фиг. 2 - временные диаграммы работы множительного устройства . Широтно-импульсное множительное устройство содержит широтно-импульс ный мoдyJтятop 1, состоящий из интегратора 2 и первого компаратора 3, второй комдаратор 4 и блок 5 умножения на знак. Интегратор 2 содержит операционный усилитель 6, масштабные резисторы 7, 8 и 9 и интегрирующий конденсатор 10. Первый компаратор 3 содержит операционный усилитель 11, масштабные резисторы 12, 13 и 14 и резистор 15 обратной связи. Второй компаратор 4 содержит операционный усилитель 16, масштабные резисторы 17, 1В и 19. Блок умножения на знак содержит операционпы усилитель 20, масштабные резисторы 21 и 22, резистор 23. обратной связи и ключ 24 на полевом транзисторе. Блок умножения на знак может быть выполнен в любом варианте: в виде двух разнополярных ключей, подключающих ко входу второго компаратора прямой или инверсный выход второго источника У входного сйгнала-сомно- . жителя или на операционном усилителе и ключе на полевом транзисторе (фиг. 1). Источник первого входного сигнала х через масштабный резистор 12 подключен к инвертирующему входу операционного усилителя 11 компаратора 3. Выход блока умножения на знак может быть подключен к любому из входов (инвертирующему или неинвертирующему) операционных усилителей 11 и 16 соответственно компараторов 3 и 4, при этом принцип функционирования устройства не нарушается, а изменяется лишь знак выходного сигнала и масштабный коэффициент при & . Широтно-импульсное множительное устройство работает следующим образом;При отсутствии входных сигналов интегратор 2 и компаратор 3 работает в автоколебательном режиме как релаксационный генератор. На выходе интегратора 2 формируется симметричное Нйлообразное напряжение, а на выходе компар.атора 3 - напряжение прямоугольной формы. Компаратор 4 переключается при переходе через ноль напряжения на выходе интегратора 2, и на его выходе также формируется симметричное прямоугольное напряжение. Если на вход интегратора 2 подан входной сигнал-сомножитель х, а на вход блока 5 умножения на знак входной сигнал-сомножитель У , то происходят следующие изменения в работе схемы. Скорость изменения напряжения на выходе интегратора 2 равна - (Up + х) при положитель1 .° 1 ° -;( х) при отрицательном ном и Нс1пряжении на выходе компаратора 3. Здесь±ио - напрях ение на выходе компаратора 3; постоянная вре-jj мени интегратора 2. Изменяются тйкже длительности отрицательного t и положительного 12. импульсов на выходе компаратора 4, которые с учетом задержек переключения компараторов равны: где ±Up- порог переключения компаратора 3; - время задержки переключечения компаратора 3 ( Относительная разность длительностей положительного t,, и отрицательного t,, импульсов на выходе ком паратора 4 равна ху + UpX Tg - DO ц, и видно,что задержка переключения второго компаратора в окончательное выражение для выходного сигнала . множительного устройства не входит В числитель этого выражения входит составляющая, пропорциональная сом ножителю X, обусловленная задержкам переключения первого компаратора, что равносильно прохождению части сигнала-сомножителя х на вход этого компаратора и вносит погрешность в результат перемножения, так как эта составляющая погрешности входит в выражение для & линейно, представляется возможным ее компенсация . Компенсируется эта погрешность подключением выхода источника первого входного сигнала-сомножителя Jc к инвертирующему входу операцион ного усилителя 11 компаратора 3 через резистор 12. Предлагаемое широтно-импульсное множительное устройство позволяет существенно повысить точность перемножения входных сигналов. Формула изобретения Широтно-импульсное множительное устройство, содержащее источник первого входного сигнала, источник второго входного сигнала, широтно-импульсный модулятор, состоящий из последовательно соединенных интегратора и первого компаратора, выход которого подключен к первому входу интегратора, второй компаратор , первыи вход которого подключен к выходу интегратора, а второй вход - к шине нулевого потенциала, и блок умножения на знак, отличающееся тем, что, с целью повьлиения его точности, источник второго входного сигнала подключен к первому входу второго компаратора чере.з блок умножения на знак, выход второго компаратора является выходом устройства, выход первого компаратора подключен к знаковому входу блока умножения на знак, вход первого компаратора, подключен к выходу источника первого входного сигнала, второй вход интегратора подключен к выходу источника первого входного сигнала. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР О 492886, кл. G 06 G 7/16, 1973. 2.Авторское свидетельство СССР по заявке .№ 2871917/18-24, кл. G 06 G 7/161, 18.01.80 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1981 |

|

SU1001116A1 |

| Широтно-импульсное множительное устройство | 1981 |

|

SU1015395A1 |

| Время-импульсное множительное устройство (его варианты) | 1981 |

|

SU1013977A1 |

| Широтно-импульсное множительное устройство | 1980 |

|

SU868783A1 |

| Множительно-делительное устройство | 1978 |

|

SU1005081A1 |

| Множительно-делительное устройство | 1986 |

|

SU1405077A1 |

| Широтно-импульсное множительное устройство | 1980 |

|

SU886009A1 |

| Время-импульсное множительно-делительное устройство | 1982 |

|

SU1032459A1 |

| Умножающий широтно-импульсный модулятор | 1989 |

|

SU1780090A1 |

| Время-импульсное множительное устройство | 1978 |

|

SU746574A1 |

Вых имтег/№

Вых KOftff. J

Bb/)f. f/rOKoS

перекд. /го/}лрнР

-3 У

комп

О

-у

(1ш

Su/jf ком/г.

Авторы

Даты

1982-06-07—Публикация

1980-10-17—Подача