(5) УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для ввода информации от двухпозиционных датчиков | 1979 |

|

SU877513A1 |

| Многоканальное устройство для ввода в ЭВМ информации от двухпозиционных датчиков | 1986 |

|

SU1310794A1 |

| Устройство для ввода информации | 1977 |

|

SU693361A1 |

| Устройство для считывания информации с двухпозиционных датчиков | 1977 |

|

SU656078A1 |

| Устройство для ввода информации | 1978 |

|

SU742918A1 |

| Генератор знаков | 1981 |

|

SU963074A1 |

| Матричный коммутатор | 1988 |

|

SU1596342A1 |

| Устройство для сбора данных от двухпозиционных датчиков | 1979 |

|

SU783784A1 |

| Вычислительное устройство для контроля параметров объекта | 1975 |

|

SU690498A1 |

| Устройство для ввода информации от двухпозиционных датчиков | 1985 |

|

SU1247880A1 |

I

Устройство относится к измерительной и вычисл.ительной технике и может быть применено для сбора информации от двухпозиционных датчиков и передачи ее в устройство приема и обработки информации, в частности в управляющую вычислительную машину.

Известно устройство для ввода информации, которое содержит коммутатор, блок памяти, блок определения изменения состояния датчиков, дешифраторы и регистры адреса, генератор, схемы объединения ИЛИ.

Известное устройство позволяет осуществить спорадический ввод информации от двухпозиционных датчиков в цифровую вычислительную машину. Недостатком этого устройства является отсутствие возможности осуществления ввода информации по командам из устройства обработки. Скорость сбора данных от двухпозиционных датчиков в устройстве снижается при росте количества контролируемых датчиков, что отрицательно сказывается на быстродействии устройства в целом р .

Наиболее близким решением по технической сущности является устройство для ввода информации,которое содержит коммутатор, одни входы которого соединены с одними входами устройства, другие входы - с выходами первого дешифратора, а выход 10с первым входом блока памяти и с первым входом формирователя кодов, второй вход которого подключен к выходу блока памяти, выходы первого и второго элементов ИЛИ соединены соот 5ветственно с первым и вторым выходами устройства и с входами третьего элемента ИЛИ, выход которого подключен к первому входу генератора и.первым входам первого и второго блоков

20 элементов И, вторые входы которых соединены с выходами первого и второго регистров, первый и второй выходы генератора подключены соотв 3 ственно к блоку памяти и входу второго регистра, одни входы третьего блока элементов И соединены с выходом коммутатора, другие входы - с выходами второго дешифратора, а выходы через четвертый элемент ИЛИ с первым входом элемента И, второй вход которого подключен к второму ходу генератора и к первому входу . устройства, а выход - к первому выхо ду устройства, одни входы первого блока коммутационных элементов соединены с выходами первого регистра другие входы - с соответствующими входами устройства, а выходы - с входами первого дешифратора, первые входы коммутационных элементов второ группы подключены к выходам второго регистра, вторые входы - к соответствующим входам устройства, а выходы к входам второго дешифратора j 2 J. Недостатками этого, устройства являются низкая скорость ввода -данных от двухпозиционны « датчиков, зависимость быстродействия устройства от числа групп каналов. Целью изобретения является повышение быстродействия -устройства. Поставленная цель -достигается те что в устройство, содержащее коммутатор, одни входы которого соединен с одними входами устройства, другие входы коммутатора соединены с выходами первого дешифратора, а выход с первым входом блока памяти и с первым входом формирователя кодов, второй вход которого подключен к выходу блока памяти,выходы первого второго элементов ИЛИ соединены соответственно с первым и вторым выхо дами устройства и с входами третьего элемента ИЛИ, выход которого подключен к первому входу генератор и к первым входам первого и второго блоков элементов И, вторые входы которых соединены с выходами первог и т|эетьего регистров, первый и второй выходы генератора подключены со ответственно к блоку памяти и входу второго регистра, одни входы третье блока элементов И соединены с выходом коммутатора, другие входы - с выходами второго дешифратора, а выходы через четвертый элемент ИЛИ nepsbiM входом элемента И, второй вх

которого подключен к второму входу генератора и первому входу устройства, а выход - к первому выходу уст-;

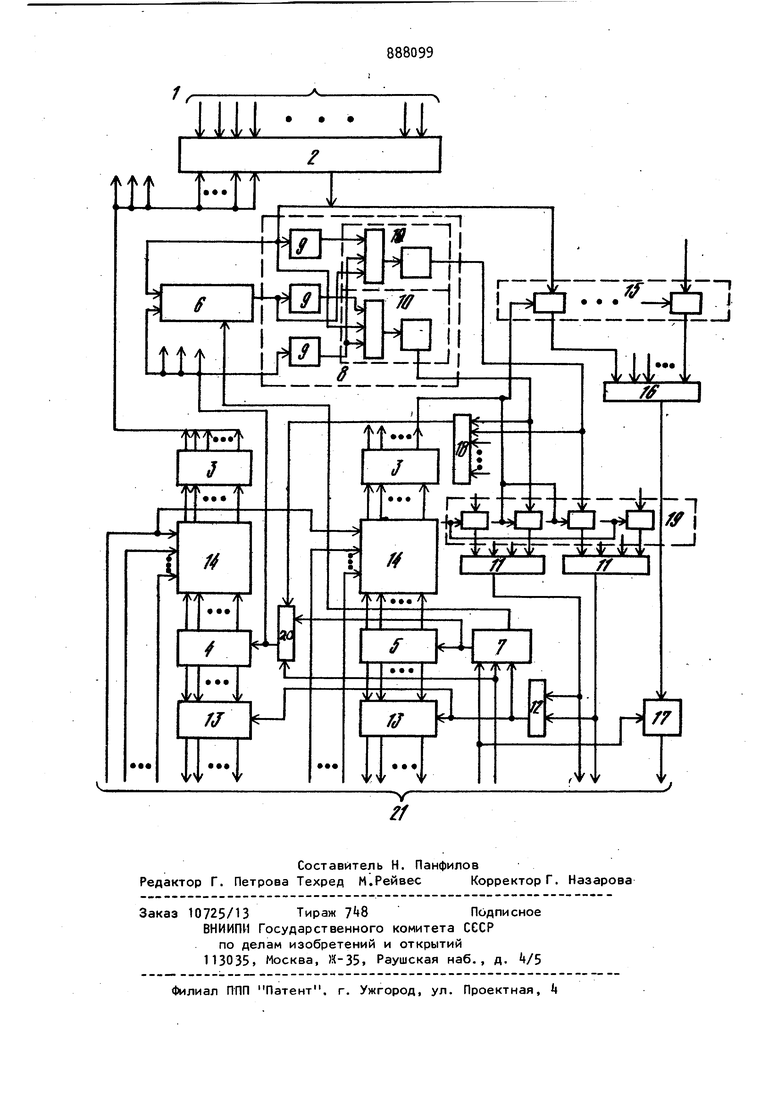

ра 2 информационные и являются входами 1 устройства. К каждому входу 1 подключен один датчик информации. Втоойства, одни входы первого блока , оммутационных элементов соединены выходами первого регистра, другие ходы - с соответствующими входами, стройства, а выходы - с входами ервого дешифратора, одни входы втоого блока коммутационных элементов одключены к выходам второго регистa, другие входы - к соответствуюим входам устройства, а выходы к входам второго дешифратора, введены четвертый блок элементов И, пятый элемент ИЛИ и формирователь импульсов, выход которого подключен к входу первого регистра, второму входу блока памяти и третьему входу формирователя кодов, причем к первому входу формирователя импульсов подключен второй выход генератора, к второму - третий вход генератора, а к третьему входу формирователя импульсов подключен выход пятого элемента ИЛИ, входы которого соединены с выходами формирователя кодов и первыми входами четвертого блока элементов И, вторые входы которых подключены к-соответствующим выходам второго дешифратора, а выходы к входам первого и второго элементов ИЛИ. На чертеже приведена блок-схема предлагаемого устройства. Устройство содержит входы 1 устройства, коммутатор 2, первый и второй дешифраторы 3, первый регистр , второй регистр 5, блок 6 памяти, генератор 7, формирователь 8 кодов, элементы НЕ 9, элементы ИЛИ-НЕ 10, первый и второй элементы ИЛИ 11, третий элемент ИЛИ 12, элементы И первого и второго блоков 13, первый и второй блоки коммутационных элементов 1, элементы И третьего блока 15, четвертый элемент ИЛИ 1б, элемент И 17, пятый элемент ИЛИ 18, элементы И четвертого блока 19, формирователь 20 импульсов, входы и выходы устройства 21. Устройство работает следующим образом. Все входы 1 устройства разбиты на каналы с равным количеством входов. В каждом канале есть свой коммутатор 2, блок 6, формирователь 8. Число Каналов равно числу выходов второго дешифратора 3- Первые входы коммутато|рые входы коммутаторов 2 стробирующие. Число информационных входов ком мутатора равно числу стробирующих входов и определяется числом выходов первого дешифратора 3 Количество выходов и позиционный код на вы ходах первого дешифратора 3 определяется разрядностью и кодом на выходах первого регистра-счетчика k адреса. Блок 6 выполнен на сдвиговом регистре с числом разрядов, равным числу входов в канале. Работа устройств с выводом информации по мере изменения состояния двухпозиционных датчиков. При подаче питания управляющий сигнал с устройства обработки информации поступает на вход устройства 21 и далее на управляющие входы первого и второго блоков коммутационных элементов 14. При этом выходы регист ров f, подключаются к соответствующим входам дешифраторов 3- Одновременно с устройства обработки информ ции поступает сигнал на вторые упра ляющие входы генератора 7 и формирователя 20. Генератор 7 начинает выдавать в регистр 5 и через формирователь 20 в регистр Ц импульсы сче та одной и той же частоты для цикли ческого опроса каналов. В соответствии с позиционными кодами на выходах первого дешифратора 3 в каждом канале выбираются входы с одинаковым номером, например первые. Информация о состоянии датчиков по первым входам каждого канала поступает на выходы соответствующих коммутаторов а с последних - на входы блока 6 соответствующих каналов и на первые управляющие входы формирователей 8. На вторые управляющие входы формирователя 8 подаются из блока 6 сигналы с информацией о состоянии каждого датчика этого же номера входа в предыдущий момент времени. На третий разрешающий-вход формирователя 8 поступают тактирующие импульсы с выход формирователя 20. В зависимости от состояния датчика в текущий и предыдущий моменты времени на выходах фор мирователя 8 формируются следующие коды: если информация на первом и втором управляющем входах блока 8 одинакова, что соответствует равенству кодов на выходах датчиков в текущий и предыдущий моменты времени, на выходах блока 8 код равен О. При О на выходе коммутатора 2 и 1 на выходе блока 6 на первом выходе блока 8 код равен 1, а на втором выходе - О. При 1 на выходе коммутатора 2 и О на выходе блока 6 код на выходе меняется на инверсный. Формирователь 8 выполняет свои функции с помощью элементов НЕ 9 и элементов ИЛИ-НЕ 10. Сигналы с выходов формирователя 8 поступают на входы пятого элемента ИЛИ 18 и на первые входы четвертого блока элементов И 19При неравенстве кодов на одних из первых и вторых управляющих входах блока 8 сигнал 1 с выхода пятого элемента ИЛИ 18 поступает на третий ьход формирователя 20 и блокирует выдачу в регистр , блок 6 и формирователь 8 импульсов циклического опроса номера датчика. Генератор 7 продолжает выдавать в регистр 5 импульсы циклического опроса номера канала. Позиционный код с выходов второго дешифратора 3 последовательно стробирует вторые входы четвертого блока элементов И 19. При совпадении кода регистра 5 с кодом номера формирователя 8, на входах которого обнаружено неравенство кодов, сигнал 1 с выходов одного из элементов ИЛИ 1I поступает на выходы устройства и на вход третьего элемента ИЛИ 12. Сигнал с выхода третьего элемента ИЛИ 12 запрещает выдачу от генератора 7 импульсов циклического опроса и разрешает выдачу через элементы И первого и второго блоков 13 на выходы устройства 21 код адреса датчика, изменившего свое состояние. После передачи этих данных по си|- налу с устройства обработки через вход устройства 21 запускается генератор 7 формирователь 20, и работа устройства возобновляется. Работа устройства с выводом информации по инициативе устройства, обработки информации. Для переключения предлагаемого устройства в указанный режим устройство обработки информации выдает управляющий сигнал на вход устройства 21. Этот сигнал поступает на управляюие входы первого и второго блоков коммутационных элементов 1А. При том выходы регистров +,5 отключатся от входов первого и второго дешифраторов 3, а на входы последнил через вторые входы первого и второго блоков коммутационных элементов 14 поступает с устройства обработки информации код адреса контролируемого датчика. Одновременно с устройства обработки информации поступает сигнал на третий управляющий вход генератора 7, по которому блокируется работа генератора и открывается элемент И 17- В соответствии с позиционными кодами на выходах первого дешифрато ра 3 в каждом канале выбираются входы 1 с заданным номером. Состояния этих входов поступают на информационные входы соответствующих элементов И третьего блока 15. В соответствии с позиционным кодом на выходах второго дешифратора 3 выбирается соответствующий элемент И третьего блока 15, с входа которого состояние выбранного датчика через четвертый элемент ИЛИ 1б и .элемент И 17 поступает на выход устройства 21.

Таким образом, устройство может работать в двух независимых режимах режим ввода информации о датчике, изменившем свое состояние по инициативе устройства и режим ввода информации о состоянии датчика по сигналу с устройства обработки информации.

Применение данного устройства позволит повысить скорость ввода данных от двухпозиционных датчиков и .обеспечит независимость быстродействия устройства от числа подключаемых каналов.

Формула изобретения

Устройство для ввода информации, содержащее коммутатор, одни входы которого соединены с одними входами устройства, другие входы коммутатора соединены с выходами первого дешифратора, а выход - с первым входом блока памяти и с первым входом формирователя кодов, второй вход которого подключен к выходу блока памяти, выходы первого и второго элементов ИЛИ соединены соответственно с первы и вторым выходами устройства и с входами третьего элемента ИЛИ, выход которого подключен к первому входу генератора и к первым входам первого и второго блоков элементов И, вторые входы которых соединены с выходами первого и второго регистров,

первый и второй выходы генератора подключены соответственно к блоку памяти и входу второго регистра, одни входы третьего блока элементов И соединены с входом коммутатора,

другие входы - с выходами второго дешифратора, а выходы через четвертый элемент ИЛИ - с первым входом элемента И, второй вход которого подключен к второму входу генератора и пер5 вому входу устройства, а выход - к первому выходу устройства, одни входы первого блока коммутационных элементов соединены с выходами первого регистра, другие входы - с соответ0 ствующими входами устройства, а выходы - с входами первого дешифратора, одни входы второго блока коммутационных элементов подключены к выходам второго регистра, другие входы5 к соответствующим входам устройства, а выходы - к входам второго дешифратора, отличающее ся тем, что, с целью повышения быстродействия устройства, в него введены четвертый

0 блок элементов И, пятый элемент ИЛИ и формирователь импульсов, выход которого подключен к входу первого регистра, второму входу блока памяти и третьему входу формирователя ко5 дов, причем к первому входу формирователя импульсов подключен второй выход генератора,к второму - третий вход генератора, а к третьему входу формирователя импульсов подQ ключен выход пятого элемента ИЛИ, входы которого соединены с выходами формирователя кодов и первыми входами четвертого блока элементов И, вторые входы которых подключены к соotвeтcтвyющим выходам второго дешифратора, а выходы - к входам первого и второго элементов ИЛИ.

Источники информации, принятые во внимание при экспертизе

кп. G 06 F 3/04, 1977 (прототип).

/.

L J/ |/ Ф

Авторы

Даты

1981-12-07—Публикация

1980-03-24—Подача