(54) УСТРОЙСТВО ДЛЯ СБОРА ДАННЫХ ОТ ДВУХПОЗИЦИОННЫХ ДАТЧИКОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сбора данных от двухпозиционных датчиков | 1978 |

|

SU746439A1 |

| Устройство для ввода информации | 1985 |

|

SU1282107A1 |

| Устройство для ввода информации | 1989 |

|

SU1644120A2 |

| Устройство для ввода измерительной информации | 1986 |

|

SU1354179A1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1987 |

|

SU1532937A1 |

| Устройство для испытаний датчиков давления | 1983 |

|

SU1129624A1 |

| Генератор сигналов сложной формы | 1980 |

|

SU983692A1 |

| Устройство для вычисления массы нефти и нефтепродуктов в резервуарах | 1983 |

|

SU1117653A1 |

| Устройство для многоточечной сигнализации | 1990 |

|

SU1795496A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

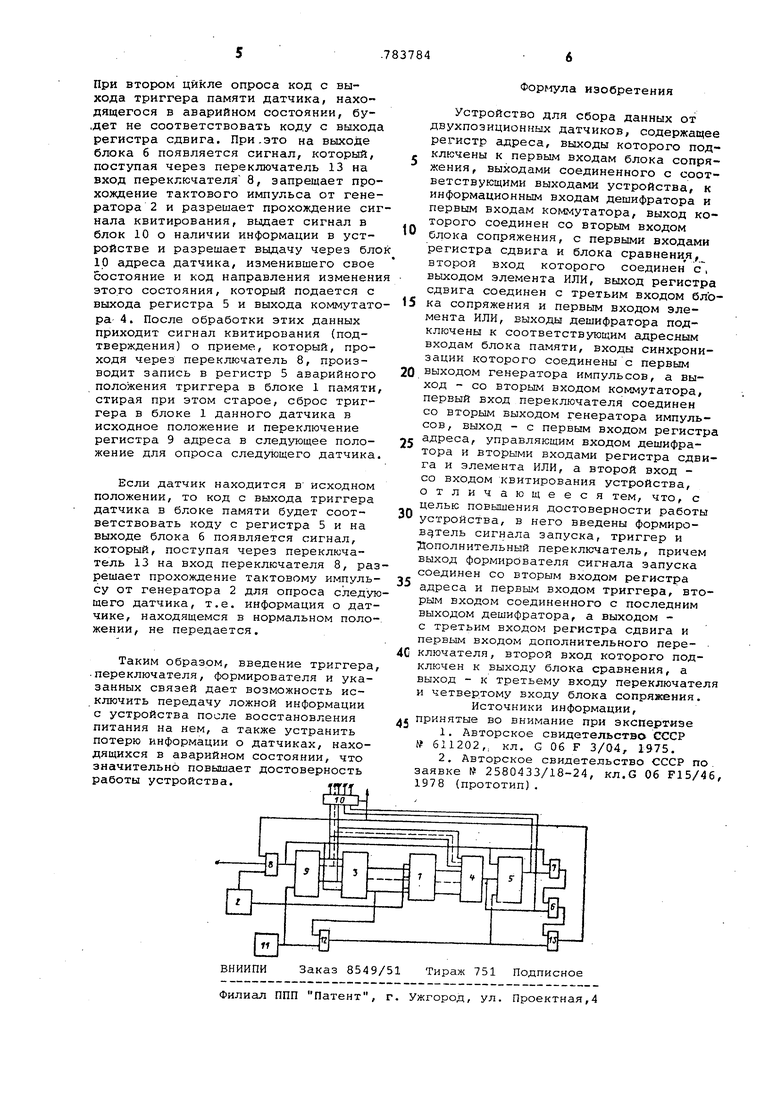

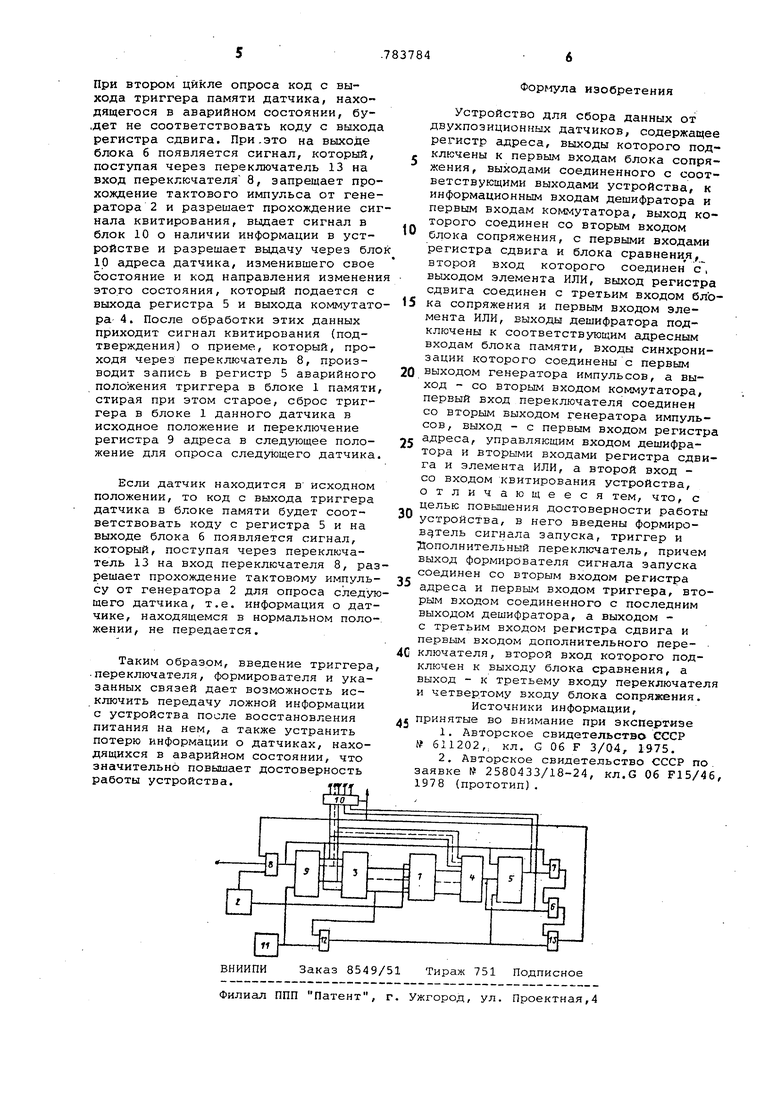

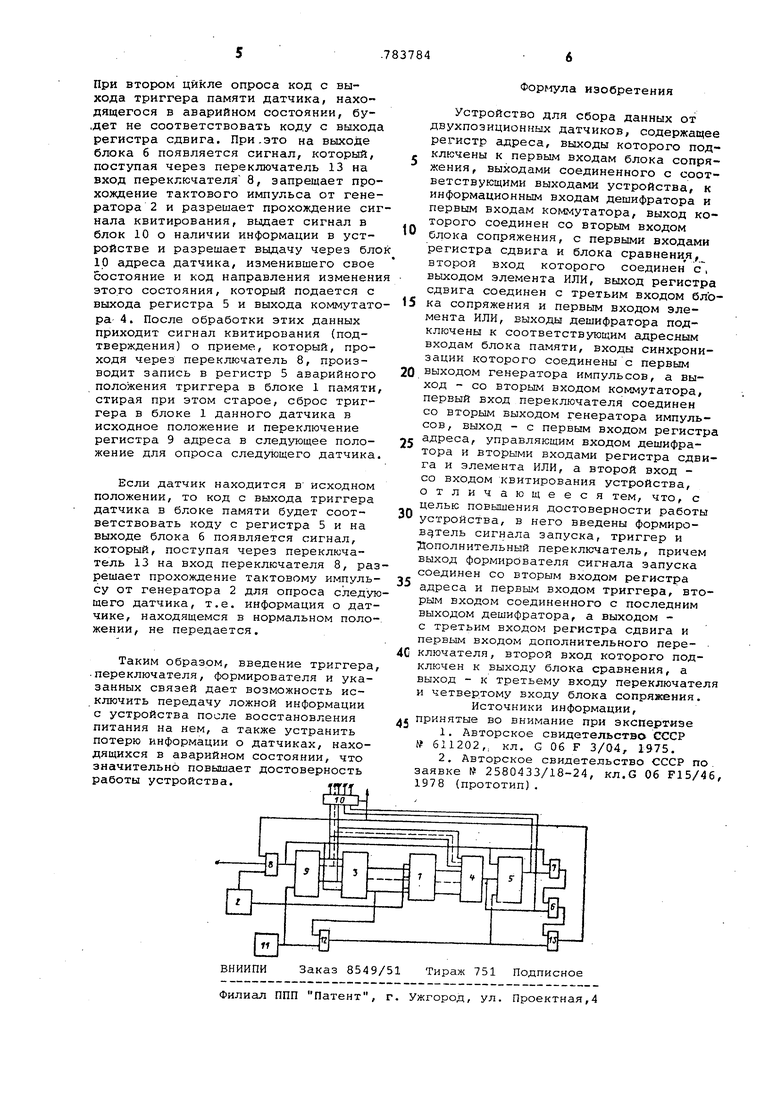

Изобретение относится к области вычислительной техники и может найти применение в автоматизированных системах управления технологическими процессами. Известны устройства для сопряжения вычислительной машины с дискретными датчиками, содержащее блок форм рования импульсов, блок буферной памяти, групповой блок кодирования, блок согласования, регистр, элемент ИЛИ и генератор тактовых импульсов ;lL Недостаток этих устройств состоит в их сложности. Наиболее близким к предлагаемому по существу технического решения является устройство для сбора данных от ДВУХПОЗИЦИОННЫХ датчиков, содержащее регистр адреса, выходы которого подключены к первым входам блока сопряжения, информационным вхо дам дешифратора и первым входам коммутатора, выход которого соединен со вторым входом блока сопряжения, с пе выми входами регистра сдвига и блока сравнения, второй вход которого подключен к выходу элемента ИЛИ,выход регистра сдвига подсоединен к треткему вхолу блоса сопряжения и к пер вому входу элемента ИЛИ, а выходы дешифратора подключены к первым входам блока памяти, вторые входы которого подсоединены к первому выходу генератора импульсов, а выходы - ко вторым внходам комл утатора. Первый вход переключателя соединен со вторым выходом генератора импульсов, а выход - с уходом регистра адреса, управлякяцим входом дешифратора, вторым входом регистра сдвига и вторым входом элемента ИЛИ. Выход блока сравнения соединен с четвертым входом блока сопряжения и вторым входом переключателя, третий вход которого является входом квитирования устройства, а выходы блока сопряясения служат соответствующими выходами устройства f2 . Недостаток этого устройства заключается в низкой достоверности работы, обусловленный тем, что после включения устройства возможна В1лдача в устройство обработки ложной информации о состоянии датчиков. Цель изобретения - повышение достоверности работы устройства. Поставленная цель достигается тем, что в устройство, содержащее регистр адреса, выходы которого подключены к первым входам блока сопряжения, выходами соединенного с соответствующими выходами устройства, к информационньам входам дешифратора и первым входам коммутатора, -выход которого соединен со вторым входом блока сопряжения, с первыми входоми регистра сдвига и блока сравнения, второй вход которого связан с выходом элемента ИЛИ, выход регистра сдвига соединен с третьим входом блока сопряжения и перйым входом элемента ИЛИ, выходы дешифратора подключены к соответ ству щим;адресным входам блока памяти входы синхронизации которого соединены с первым выходом генератора импульсов, а выход - со вторым входом KOi-iMyTaTOpa, первый вход переключателя соединен со вторым выходом генератора импульсов, выход - с первым входом регистра адреса, управляющим входом дешифратора и вторыми входа-ми регистра сдвига и элемента ИЛИ,а второй вход - со входом квитирования устройства,введены формирователь сиг нала запуска, триггер и дополнительный: переключатель. При этом выход формирователя сигнала запуска соединен; со вторым входом регистра адреса и первым входом триггера, вторым вхо дом соединенного с последним выходом дешифратора , а выходом - с третьим входом регистра сдвига и первым входом дополнительного переключателя, второй вход которого подключен к выходу блока сравнения, а выход - к третьему входупереключателя и четвертому входу блока сопряжения. На чертеже приведена схема устройства. Она содержит блок 1 памяти, генератор 2 импульсов, дешифратор 3, коммутатор 4, регистр 5 сдвига, блок 6 сравнения, элемент ИЛИ 7, переключатель 8, регистр 9 адреса, блок 10 сопряжения, формирователь 11 сигнала запуска, триггер 12 и дополнительный переключатель 13. Выходы датчиков соединены с Л-в.хо дами триггеров блока 1 памяти,число которых равно числу обслуживаемых да чиков, К-входы триггеров блока памя соединены с землей,С-входы - с генер тором 2, R-входы - с соответствующи выходами дешифратора 3, а выходы тр геров блока памяти - с соответствую щими входами коммутатора 4. Число разрядов регистра 5 равно числу дат чиков. Тактовые импульсы для циклическо опроса триггеров блока 1 памяти пос пают на один из входов переключател 8, а на два другие входа подаются сигнал квитирования от устройства обработки информации и сигнал управления от дополнительного переключателя 13. Устройство работает следующим об разом. При восстанов.пении питания на выоде формирователя 11 появляется сигал, который устананливает регистр адреса и триггер 12 в исходное поожение. Сигнал, появляющийся при. этом на ыходе триггера 12, подключает ИН ормационный вход регистра 5 сдвига входу с кодом О, вызывает на ыходе дополнительного переключателя 3 сигнал, который, поступая на вход ереключателя 8, разрешает прохождеие тактовым импульсам от генератоа 2 . Под воздействием кода, поступающего с выхода регистра 9 адреса на управляющие входы кО.мутатора 4 и дешифратора 3, выход триггера первого датчика блока 1 через коммутатор 4 подключается к входам регистра 5 сдвига 4 блока б сравнения. На другой вход блока 6 через элемент ИЛИ 7 подается сигнал с выхода регистра 5, триггеры которого могут быть установлены в любое положение. Первый тактовый импульс, поступающий с выхода переключателя 8, производит запись в регистр 5 сдвига кода О, независимо от того, в .каком положении находится триггер первого датчика в блоке 1 памяти, а также, воздействуя на вход дешифратора 3, формирует на первом выходе его сигнал сброса триггера первого датчика в блоке 1 в исходное положение, а задним фронтом переводит регистр 9 адреса в следующее положение, тем самым подключая выход триггера второго датчика. Опрос последующих триггеров блока памяти производится аналогичным образом, т.е. в регистре сдвига записывается код О ,, а триггер памяти устанавливается в исходное положение. Сигналом, который появляется на последнем выходе дешифратора 3 при опросе последнего триггера памяти, триггер 12 устанавливается в положение, при котором сигнал с его выхода подключает информационный вход регистра 5 сдвига к выходу коммутатора 4, а выход переключателя i3 - к выходу блока 6.. Если датчик в данный момент времени находится в аварийном состоянии, то на его выходе формируется Этот код от первого же синхронизирующего импульса, поступающего от генератора 2 на входы блока памяти, записывается в триггер данного датчика. Таким образом, после восстановления питания к началу второго цикла опроса все триггеры регистра 5 сдвига устанавливаются в исходное (нулевое) положение, а триггеры памяти датчиков в блоке 1 - в положение, соответствующее состоянию датчиков.

Авторы

Даты

1980-11-30—Публикация

1979-01-08—Подача