(54) ДАТЧИК СЛУЧАЙНЫХ ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля устойчивости функционирования программ | 1987 |

|

SU1437869A2 |

| Датчик случайных чисел | 1983 |

|

SU1200285A1 |

| ГЕНЕРАТОР СЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2003 |

|

RU2250489C1 |

| Датчик случайных чисел | 1977 |

|

SU641475A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 2004 |

|

RU2259017C1 |

| Генератор потоков случайных событий | 1979 |

|

SU824178A1 |

| Многоканальный генератор случайных величин | 1978 |

|

SU966691A1 |

| Устройство для моделированияэлЕКТРОННыХ CXEM | 1978 |

|

SU813440A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2000 |

|

RU2179787C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СЛУЧАЙНЫХ СИГНАЛОВ | 1990 |

|

RU2037193C1 |

I

Изобретение относится к вычислительной технике и может быть использовано при моделировании случайных процессов.

Известен датчик случайных чисел, содержащий генератор сл5гчайного напряжения и ключи. Недостатком этого датчика является невозможность получения усеченных функций распределений случайных процессов из исходных 13.

Известен также датчик случайных чисел, содержащий источник случайного сигнала, элемент И и блок сравнения. Недостатком данного устройства является искажение функций распределения tz.

Наиболее близок к предлагаемому датчик случайных чисел, содержащий первичньй источник случайных сигналов, выход которого соединен с выходами блока сравнения, первым входом первого элемента И и входом блока памяти, выходы которого через последовательно соединенные коммутатор, второй элемент И и элемент ИЛИ, второй вход которого соединен с выходом первого элемента И, соединены с выходом устройства, а управляющие входы коммутатора элементов И и блока памяти соединены с выходами блока сравнения f 3 .

Недостаток прототипа - наличие сложного многовходового коммутатора.

10

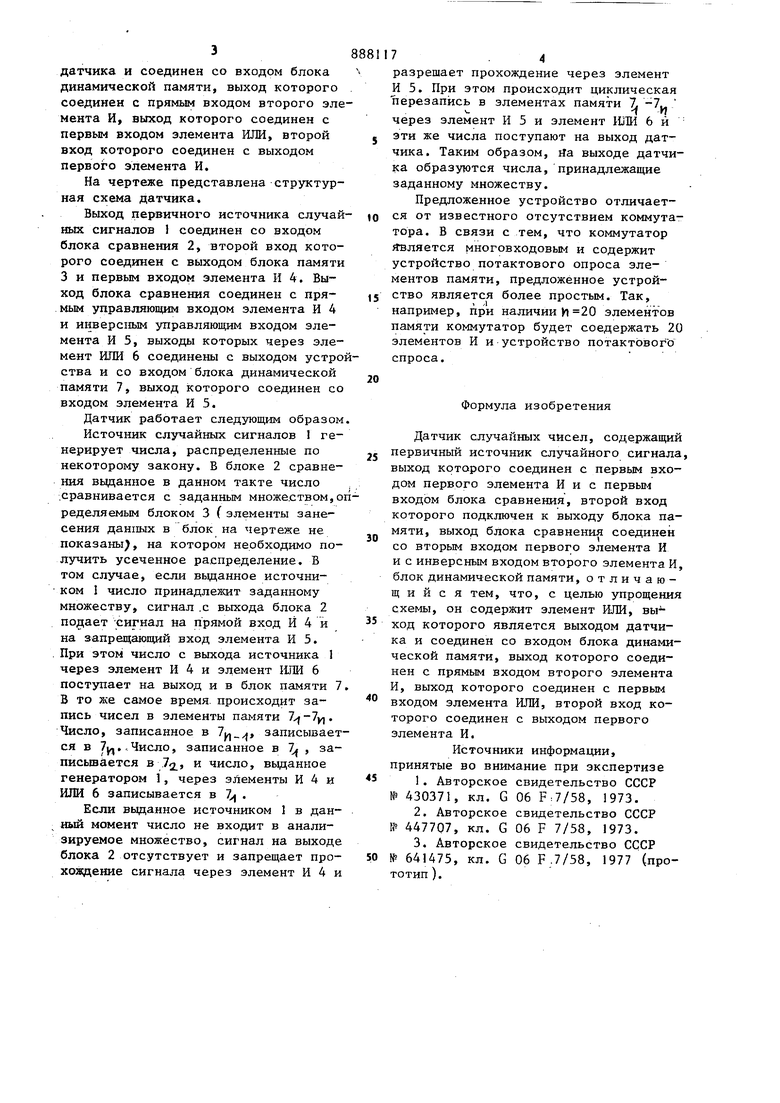

Целью изобретения является упрощение датчика. Для достижения поставленной цели в известный датчик случайных чисел, содержащий первичный источник случайного сигнала, выход которо15го соединен с первым входом первого элемента И и с первьм входом блока сравнения, второй вход которого подключен к выходу блока памяти, выход блока сравнения соединен со вторым

20 входом первого элемента И и с инверсным входом второго элемента И, блок динамической памяти, введен элемент ИЛИ, выход которого является выходом 3 датчика и соединен со входом блока динамической памяти, выход которого соединен с прямым входом второго эле мента И, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом первого элемента И. На чертеже представлена структурная схема датчика. Выход первичного источника случай иых сигналов 1 соединен со входом блока сравнения 2, второй вход которого соединен с выходом блока памяти 3 и первым входом элемента И 4. Выход блока сравнения соединен с прямым управляющим входом элемента И 4 и инверсным управляющим входом элемента И 5, выходы которых через элемент ИЛИ 6 соединены с выходом устро ства и со входом блока динамической памяти 7, выход которого соединен со входом элемента И 5. Датчик работает следующим образом Источник случайных сигналов 1 генерирует числа, распределенные по некоторому закону. В блоке 2 сравнения заданное в данном такте число .сравнивается с заданным множеством,о ределяемым блоком 3 (элементы занесения данных в блок на чертеже не показаны, на котором необходимо получить усеченное распределение. Б том случае, если вьщанное источником 1 число принадлежит заданному множеству, сигнал .с выхода блока 2 подает сигнал на прямой вход И 4 и на запрещающий вход элемента И 5. . При этом число с выхода источника 1 через элемент И 4 и элемент ИЛИ 6 поступает на выход и в блок памяти 7 В то же самое время, происходит запись чисел в элементы памяти 7 -7yj. Число, записанное в 7i, записывает ся в 7у.|., Число, записанное в , записьшается в .72,, и число, вьщанное генератором 1, через элементы И 4 и ИЛИ 6 записывается в 7 . Если выданное источником 1 в данный момент число не входит в анализируемое множество, сигнал на выходе блока 2 отсутствует и запрещает прохождение сигнала через элемент И 4 и 7. 4 разрешает прохождение через элемент И 5. При этом происходит циклическая перезапись в элементах памяти 7, 7. Uт П через элемент И 5 и элемент 1Ш1 6 и этн же числа поступают на выход датчика. Таким образом, rfa выходе датчика образуются числа, принадлежащие заданному множеству. Предложенное устройство отличается от известного отсутствием коммутатора. В связи с тем, что коммутатор является многовходовым и содержит устройство потактового опроса элементов памяти, предложенное устройство является более простым. Так, например, при наличии элементов памяти коммутатор будет соедержать 20 элементов И и устройство потактового спроса. Формула изобретения Датчик случайных чисел, содержащий первичный источник случайного сигнала, выход которого соединен с первым входом первого элемента И и с первым входом блока сравнения, второй вход которого подключен к выходу блока памяти, выход блока сравнения соединен со вторым входом первого элемента И и с инверсным входом второго элемента И, блок динамической памяти, отличающийся тем, что, с целью упрощения схемы, он содержит элемент ИЛИ, вы ход которого является выходом датчика и соединен со входом блока динамической памяти, выход которого соединен с прямым входом второго элемента И, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом первого элемента И. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 430371, кл. G 06 F:7/58, 1973. 2.Авторское свидетельство СССР № 447707, кл. G 06 F 7/58, 1973. 3.Авторское свидетельство СССР № 641475, кл. G 06 F.7/58, 1977 (прототип ).

Авторы

Даты

1981-12-07—Публикация

1980-03-14—Подача