входом элемента задержки, выход ко торого соединен с входом Пуск генератора импульсов, выход которого соединен с входом распределит ля импульсов, первый выход которого соединен с первым входом третье го элемента И блока управления, вы ход пятого элемента И блока/управления соединен с первым инверсным входом третьего элемента ИЛИ блока управления, второй инверсный вход которого подключен к выходу тестого элемента И, выход седьмого элемента -И блока управления соединен .с входом переключателя, первьй выход которогосоединен с третьим входом четвертого элемента ИЛИ блока управления, а второй выход переключателя соединен с третьим инверсным входом третьего элемента ИЛИ блока управления, четвертый инверсный вход которого подключен к выходу первого элемента И блока управления, выход восьмого элемента И блока управления соединен с первым входом пятого элемента ИЛИ блока управления, второй вход котор.ого подключен к второму выходу переключателя, а выход пятого элемента ИЛИ блока управления соединен со счетным входом счетчика и с вторым входом элемента ИЛИ-КЕ, выход -которого соединен с синхронизи рующим входом первого регистра пам ти, группа информационных входов которого соединена с группой выходов первого коммутатора соответственно, управляющий вход которого подключен к выходу первого элемента ШШ блока управления, второй Вы ход распределителя импульсов соединен с первыми входами четвертого и пятого элементов И блока управле ния, третий выход распределителя импульсов соединен с первыми входами первого, шестого, седьмого и восьмого элементов И блока управ ления, выход первого разряда регистра сдвига блока управления. соединен с вторым входом элемента ШШ и с вторыми входами пятого к третьего элементов И блока управ ления, выход второго разряда регистра сдвига блока управления сое динен с вторыми входами четвертого и шестого элементов И блока управ5ления, третий вход которого объединен с инверсньпу входом второго элемента. И блока управления и подклю- чен к выходу схемы сравнения, выход третьего разряда регистра сдвига блока управления соединен с вторым входом первого элемента И блока управления, с управлякяцим входом блока памяти и с первым управляющим входом второго коммутатора группа выходов которого соединена с первой группой входов сумматора соответственно, вторая группа входов которого соединена с группой выходов первого регистра памяти соответственно, выход четвертого разряда регистра сдвига блока управления соединен с первым входом первого элемента ИЛИ блока управления и вторым входом седьмого элемента И блока управления, выход пятого разряда регистра сдвига блока управления соединен с вторыми входами первого элемента ИЛИ и восьмого элемента И блока управления и с вторым управляющим входом второго коммутатора, первая группа информа1даонных входов которого объединена с первой группой входов схемы сравнения и подключена к группе выходов второго регистра памяти соответственно, а вторая группа информаци- . онных входов второго коммутатора объединена с второй группой входов схемы сравнения и подключена к группе выходов регистра сдвига соответственно, группа выходов схемы сравнения подключена к группе выходов регистра сдвига соответственно, группа выходов схемы сравнения подключена к первой группе информационных входов блока памяти соответственно и является первой группой выходов случайных чисел датчика, второй группой выходов случайных чисел которого является группа выходов блока памяти, группа выходов наборного поля соединена с первой группой информационных входов первого коммутатора соответственно, вторая группа информационных входов которого объединена с второй группой информационных входов блока памяти и подключена к группе выходов сумматора соответственно.

Изобретение относится к вычислительной и испытательной технике, может быть использовано для моделирования случайных процессов и полей на универсальных и специализированных вычислительных машинах, а также для формирования многопараметрических сигналов в испытательных CIHICтемах и особенно эффективно при генерировании дискретных случайных величин, представляемых двоично-кодированныш числами в форме с фиксированной либо с плаванщей точкой переменной (ординарной или двойной) точности, а также случайных величин представляемых набором параметров, например, при воспроизведении сложных функций распределения, составленных из конечного множества взвешенных по вероятности первичных распределений. .

Цель изобретения - упрощение датчика, повьш1ение его точности и расширение функциональных возможностей за счет увеличения класса воспроизводимых статистических ха-; рактеристик.

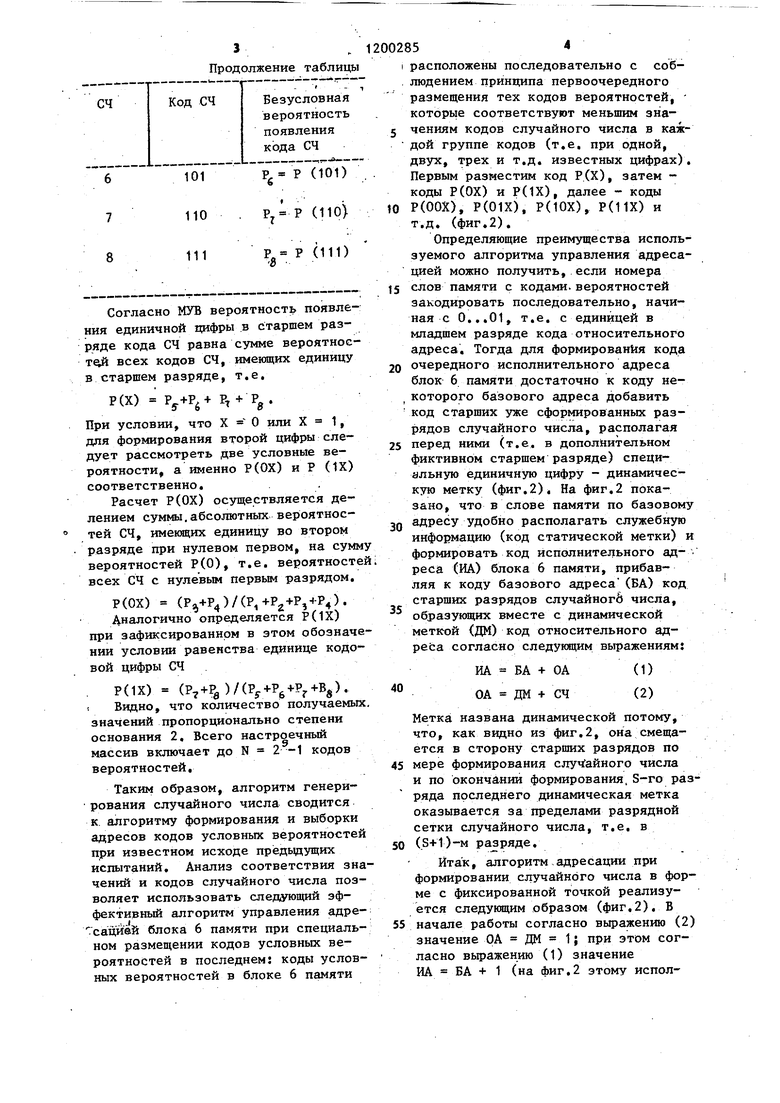

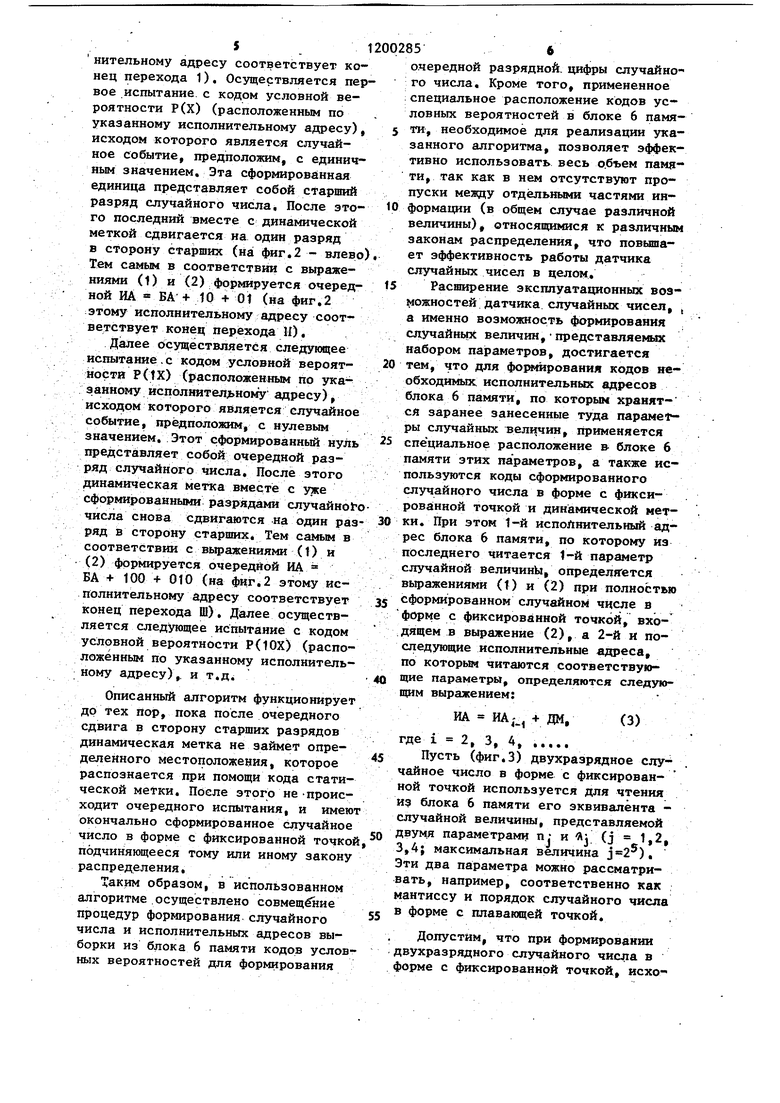

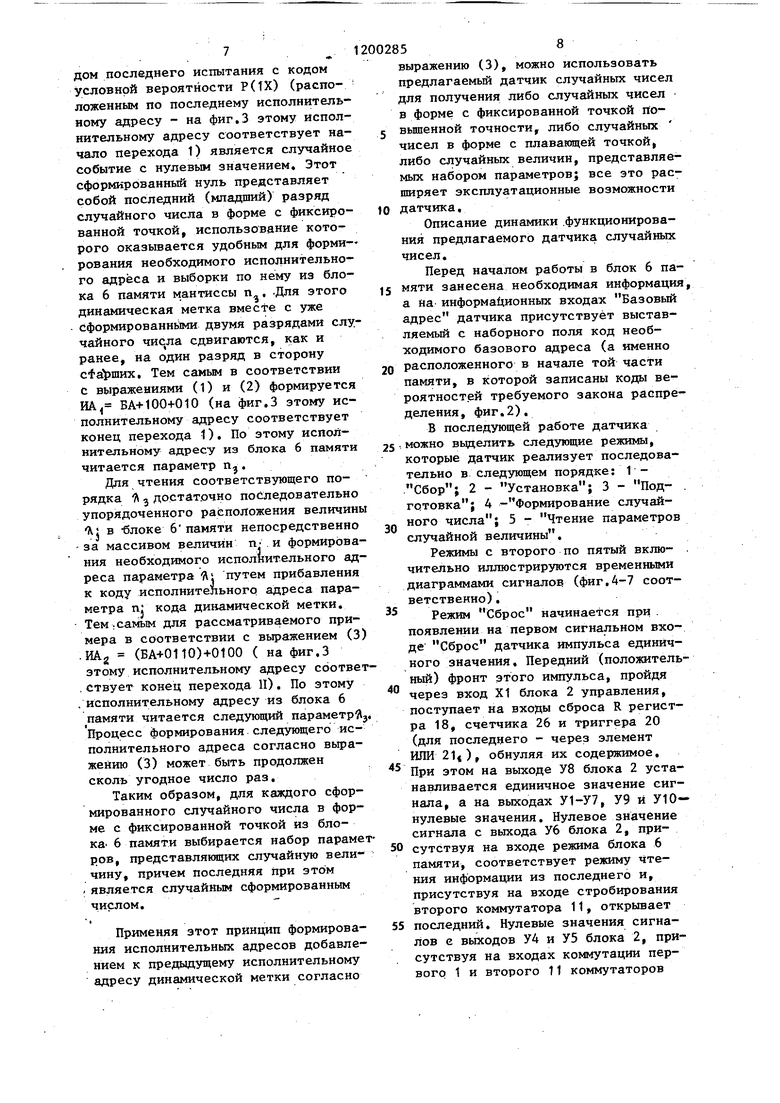

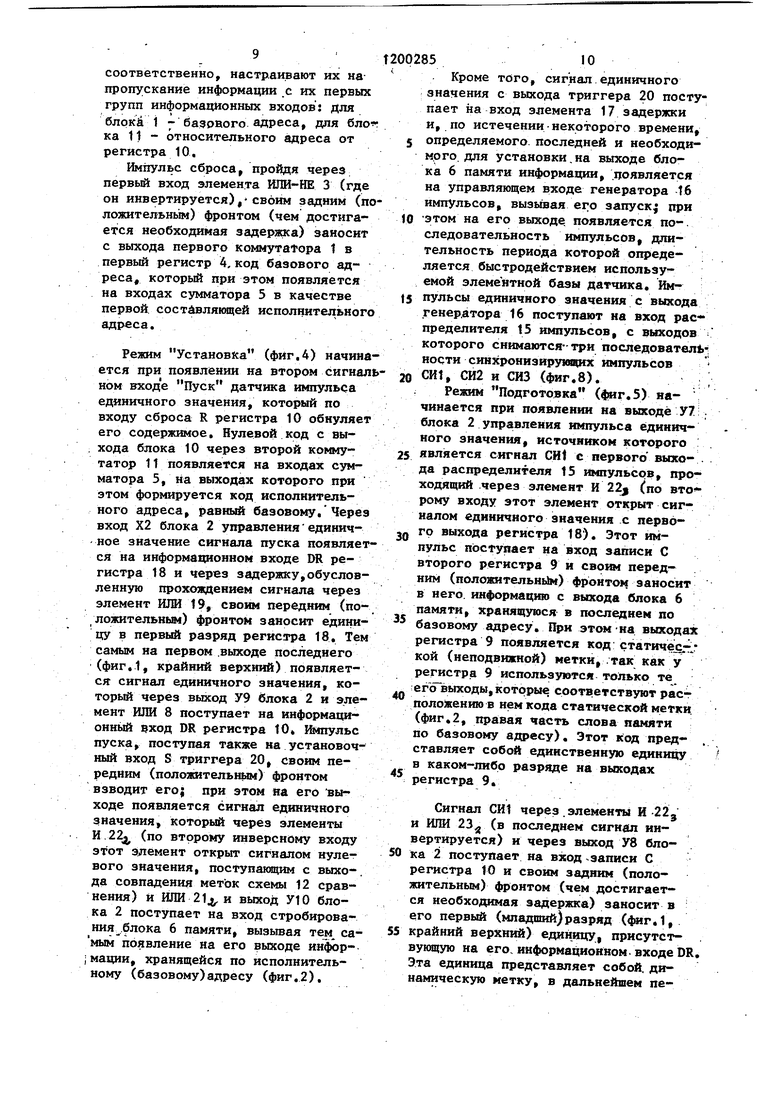

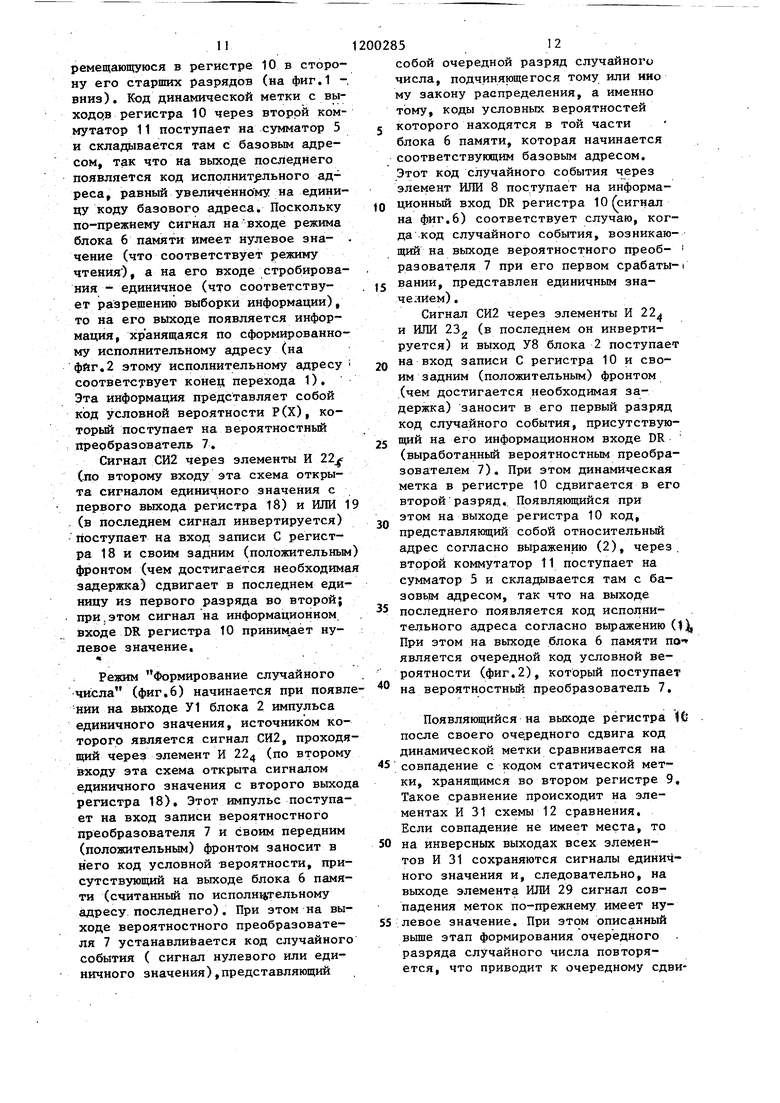

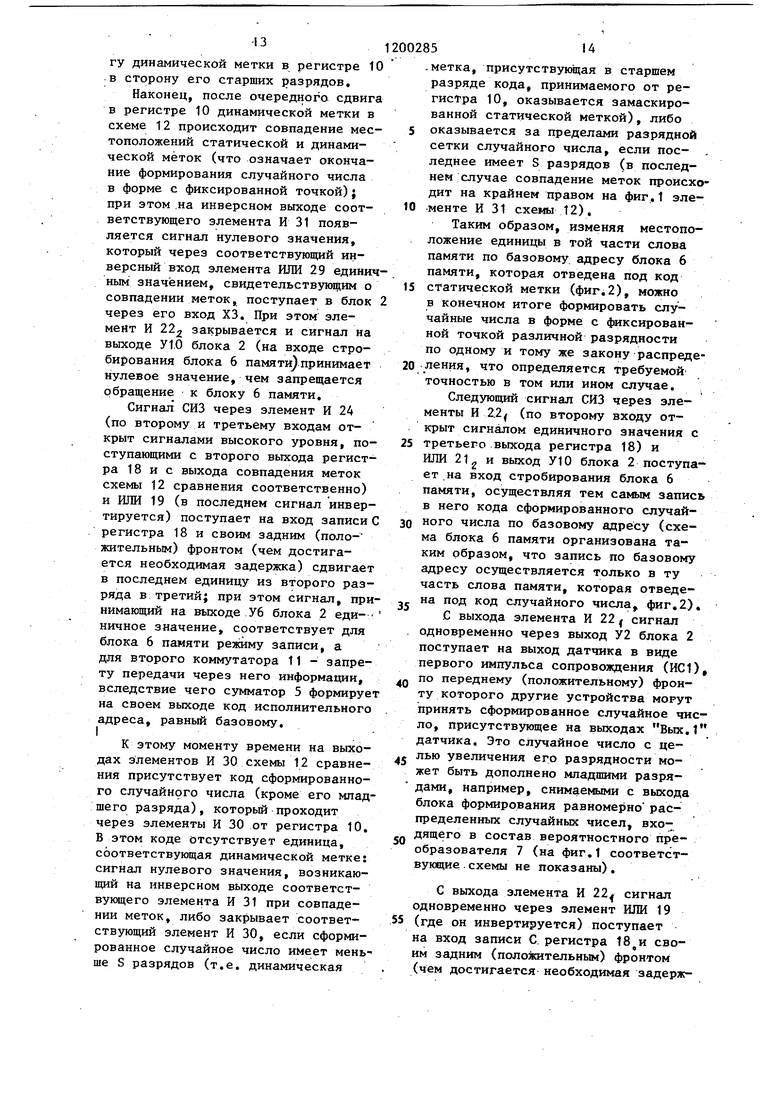

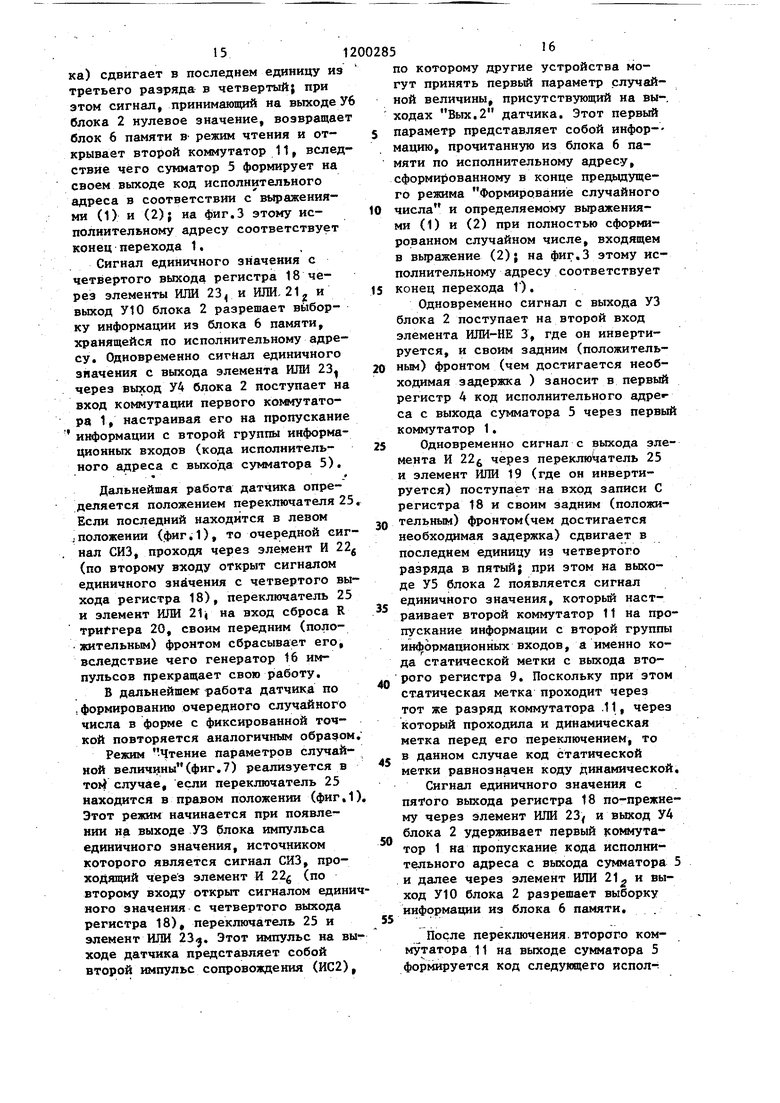

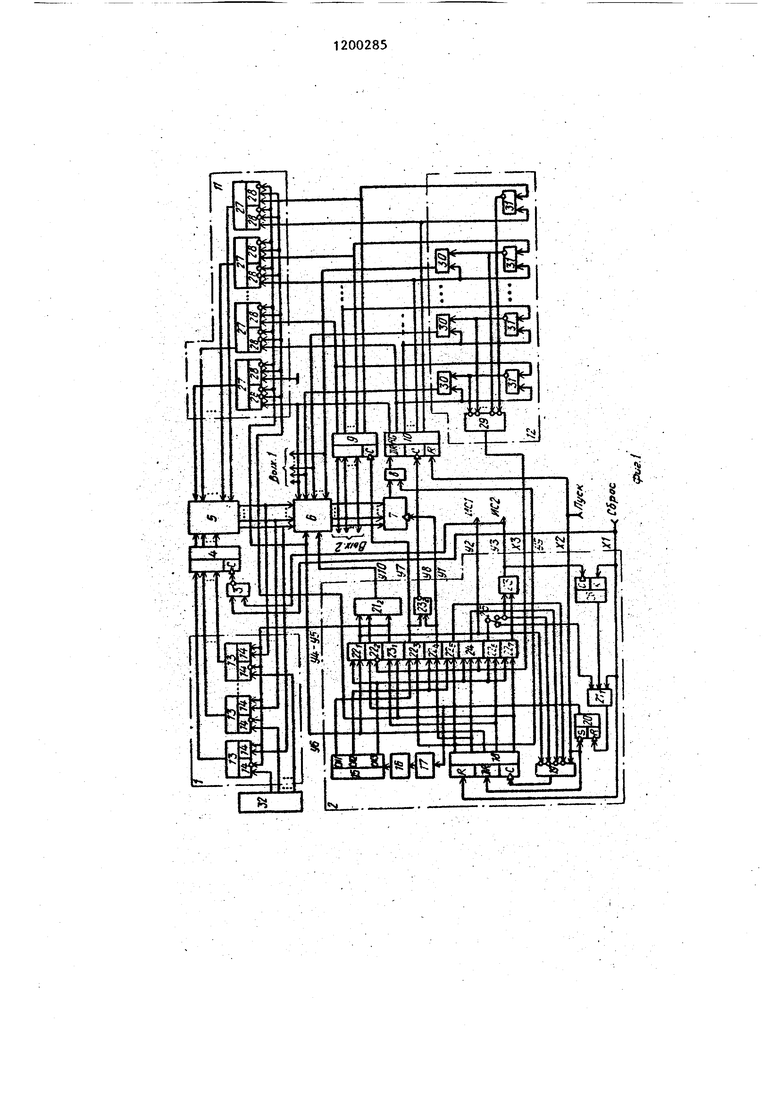

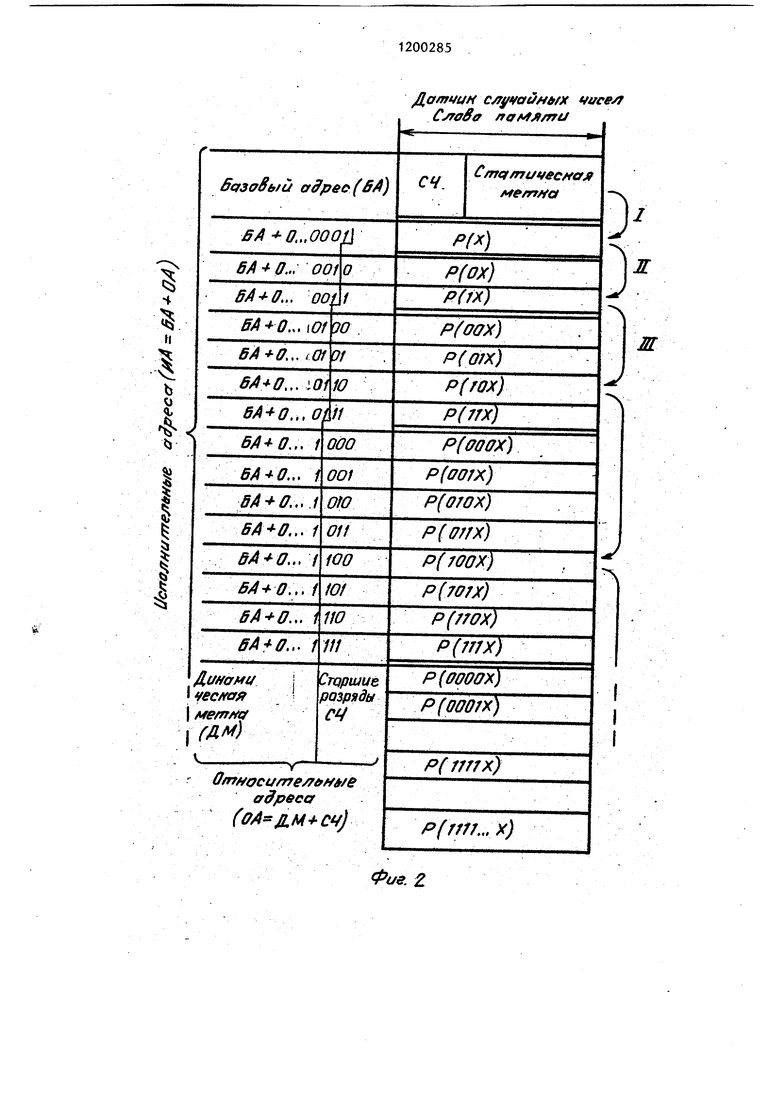

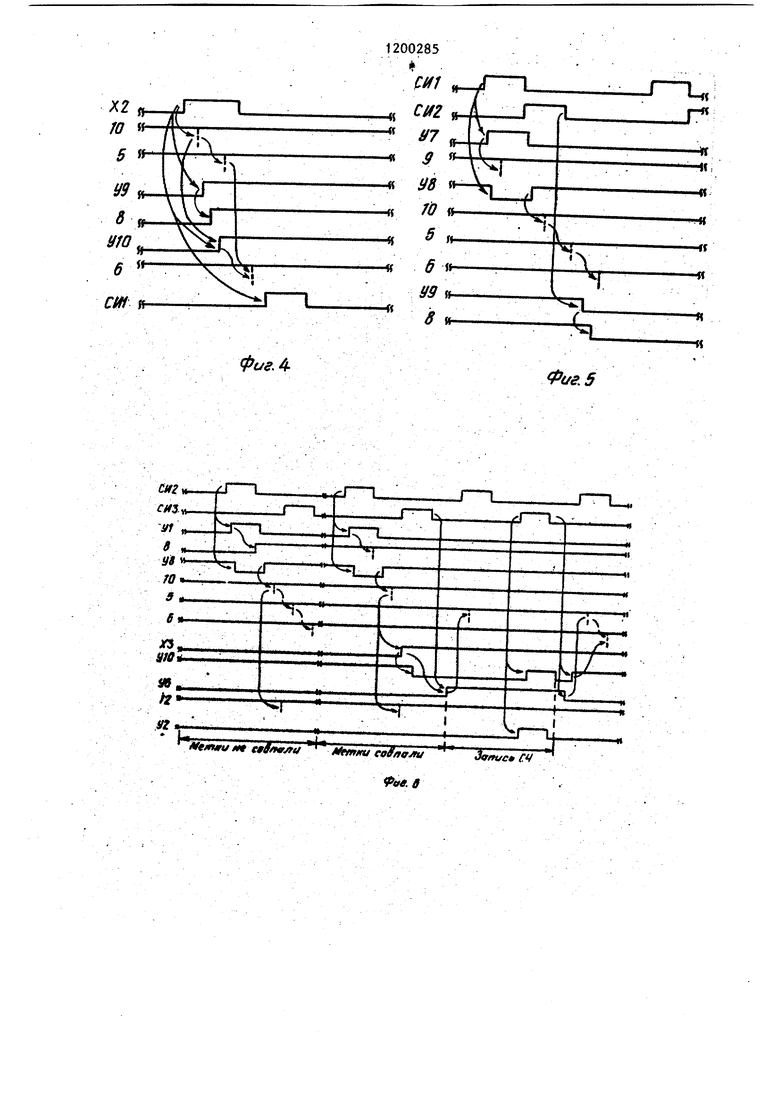

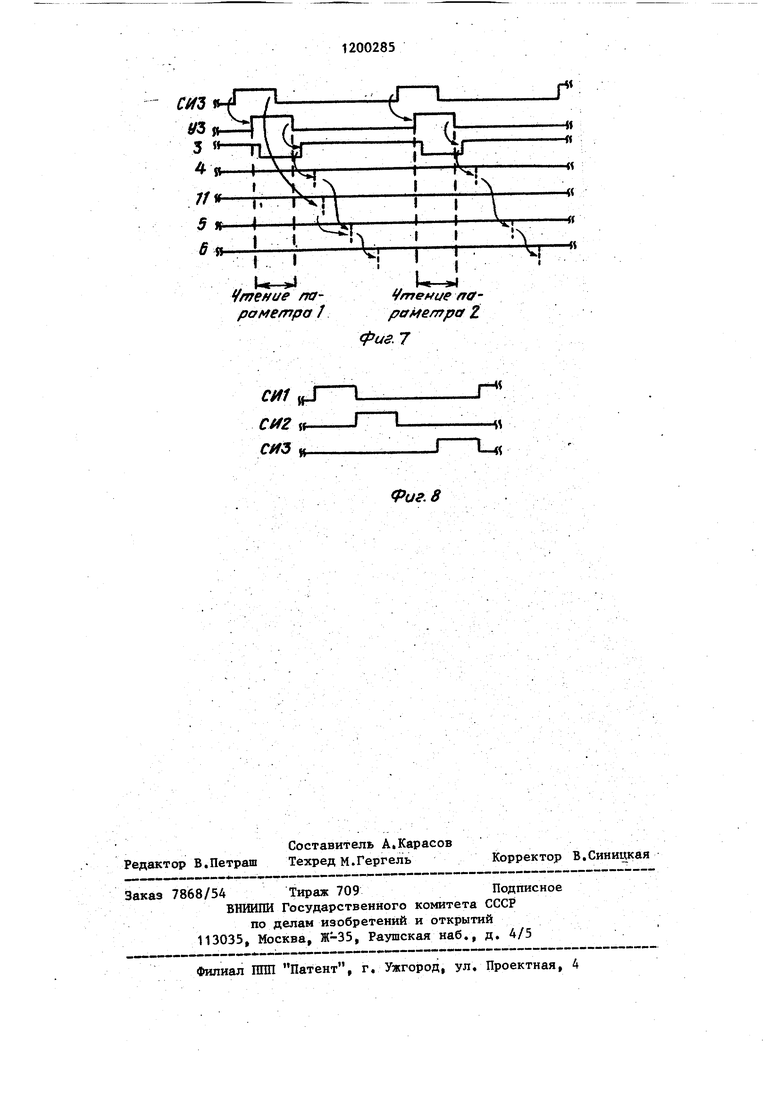

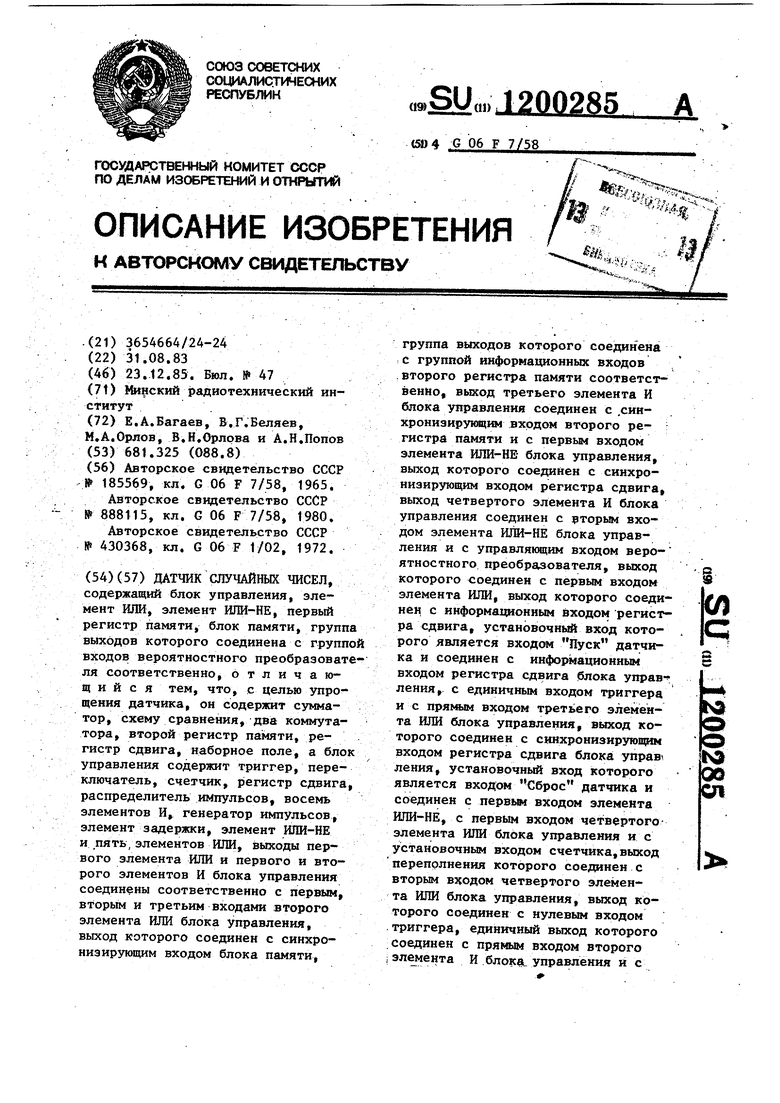

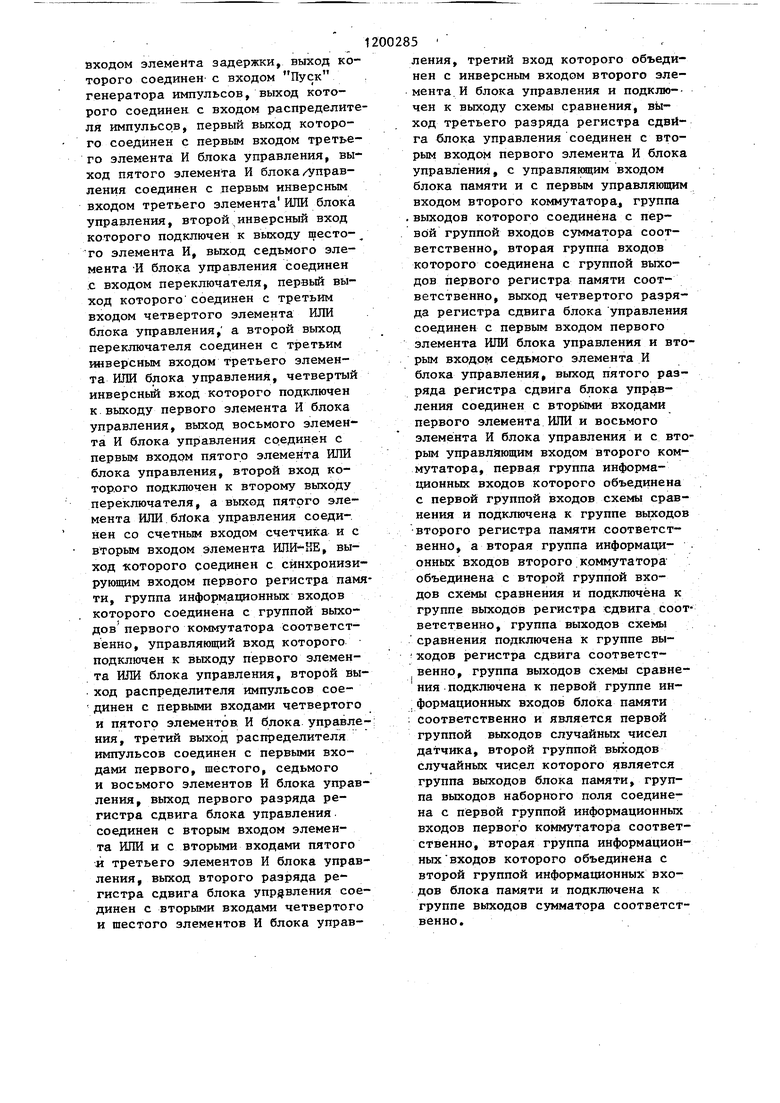

На фиг.1 представлена функциональная схема датчика случайных чисел; на фиг.2 - пример содержимого части памяти, поясняющий процесс формирования случайного числа в форме с фиксиро,18анной точкой; на фиг.З - пример содержимого части памяти, поясняющий процесс чтения из памяти параметров.случайной величины, в частности, мантиссы и порядка случайного числа в форме с плавающей точкой; на фиг.4-7 временные диаграм в 1 сигналов при работе датчика в режимах Установка, Подготовка, Формирование случайного числа и Чтение параметров случайной величины соответственно; на фИг.8 - временная диаграмма синхронизирующих импульсов, вырабатываемых распределителем импульсов блока управления.

Датчик содержит первый коммутатор 1, блок 2 управления, элемент ИЛИ-НЕ 3, первый регистр 4 памяти, сумматор 5, блок 6 памяти, вероятностный преобразователь 7, элемент ИЛИ 8, второй регистр 9 памяти, регистр.10 сдвига, второй коммутатор 11, схему 12 сравнейия.

Первый коммутатор 1 содержит элементы. Или 13 и элементы И 14.

. Блок 2 управления содержит распределитель 15 импульсов, генератор 16 импульсов, элемент 17 задеряС ки, регистр 18 сдвига,.элемент

ИЛИ 19, триггер 20, элементы ИЖ 21 и 21,, элементы И ,- элементы ИЛИ 23,-23,, элемент И 24, пё- реключатель 25, счетчик 26.

.Второй .коммутатор 11, содержит элементы ИЛИ 27 и элементы И 28,.

Схема 2-сравнения-содержит элемент ИЛИ 29 и элементы И 30 и 31. Кроме того, датчик содержит наборное поле 32. Вероятностный преобразователь 7 выполнен, как в известном устройстве.

Датчик случайных чисел работает следуницим образом. .

В основу работы датчика положен

метод условных вероятностей (МУВ), согласно которому формирование случайного числа в форме с фиксированной точкой осуществляется последовательно, разряд за разрядом, начиная со старшего. Коды условных вероятностей появления в результате работы датчика определенного значения разрядной цифры случайного числа рассчитываются по известным вероятностям появ хения всего случайного числа (СЧ) из полного их набора, подчиняющегося заданному закону распределения;; эти рассчитанные коды вероятностей заносятся в блок 6 памяти и хранятся там,

С целью пояснения метода условных вероятностей рассмотрим следующий пример. Пусть закон распределения задан таблично для восьми значений СЧ.

Безусловная

СЧ

Код СЧ вероятность появления кода СЧ

Р Р(ООО)

000

1 2 3 4 5 001

Pg« Р (001)

Р Р (010) 010

Р Р (011) 011

Pj Р (100) 100

Продолжение таблицы

Согласно МУВ вероятност| появления единичной цифры в старшем разряде кода СЧ равна сумме вероятност всех кодов СЧ, имеющих единицу в старшем разряде, т.е.

Р(Х)

, + Р, + Р,

S(,

8

При условии, что X о или X 1, для формирования второй цифры следует рассмотреть две условные вероятности, а именно Р(ОХ) и Р (IX) соответственно.

Расчет Р(ОХ) осуществляется делением суммы.абсолютных вероятностей СЧ, имекядих единицу во втором разряде при нулевом первом, на сумму вероятностей Р(0), т.е. вероятностей всех СЧ с нулевым первым разрядом.

Р(ОХ) ()/(Р,+Р2+Р,+Р).

Диалогично определяется Р(1Х) при зафиксированном в этом обозначении условии равенства единице кодовой цифры СЧ

Р(1Х) ( )/(P,..+B).

Видно, что количество получаемых, значений пропорционально степени основания 2. Всего настроечный массив включает до N 2-1 кодов вероятностей.

Таким образом, алгоритм генерирования случайного числа сводится к алгоритму формирования и выборки адресов кодов условных вероятностей при известном исходе прёдьщущих испытаний. Анализ соответствия значений и кодов случайного числа позволяет использовать следующий эффективный алгоритм управления адре сациви блока 6 памяти при специальном размещении кодов условных вероятностей в последнем: коды условных вероятностей в блоке 6 памяти

расположены последовательно с соблюдением принципа первоочередного размещения тех кодов вероятностей, которые соответствуют меньшим зна- чениям кодов случайного числа в каждои группе кодов (т.е. при одной, двух, трех и т.д. известных цифрах). Первым разместим код Р(Х), затем коды Р(ОХ) и р(1Х), далее - коды

Р(ООХ), Р(01Х), Р(10Х), Р(11Х) и т.д. (фиг.2).

Определяющие преимущества используемого алгоритма управления адресацией можно получить, если номера

слов памяти с кодами.вероятностей закодировать последовательно, начиная с 0...01, т.е. с единицей в младшем разряде кода относительного адреса. Тогда для формирования кода

очередного исполнительного адреса блок 6 памяти достаточно к коду некоторого базового адреса добавить

код старших уже сформированных разрядов случайного числа, располагая

перед ними (т.е. в дополнительном фиктивном старшем разряде) специальную единичную цифру - динамическую метку (фиг.2) На фиг.2 показано, что в слове памяти по базовому

адресу удобно располагать служебную информацию (код статической метки) и формировать код исполнительного ад- реса (ИА) блока 6 памяти, прибавляя к коду базового адреса (БД) код старших разрядов случайногб числа, образующих вместе с динамической меткой (да) код относительного адpefca согласно следующим выражениям;

(1)

ИД БД + ОД

(2)

ОА да + СЧ

Метка названа динамической потому, что, как видно из фиг.2, она смещается в сторону старших разрядов по

мере формирования случайного числа и по окончании формирования, S-ro разряда последнего динамическая метка оказывается за пределами разрядной сетки случайного числа, т.е. в

(S+1)-M разряде.

Итак, алгоритм,адресации при формировании случайного числа в форме с фиксированной точкой реализуется следующим образом (фиг.2). В

начале работы согласно выражению (2) значение ОД да 1; при этом согласно вьфажению (1) значение ИД БД + 1 (на фиг.2 этому исполнительному адресу соответствует конец перехода 1), Осуществляется пер вое испытание с кодом условной вероятности Р(Х) (расположенным по указанному исполнительному адресу), исходом которого является случайное событие, предположим, с единичным значением. Эта сформированная единица представляет собой старший разряд случайного числа. После этого последний вместе с динамической меткой сдвигается на один разряд в сторону старших (на фиг.2 - влево Тем самым в соответствии с выражениями (1) и (2) формируется очередной ИА БА + 10 +01 (на фиг.2 этому исполнительному адресу соответствует конец перехода И) . Далее осуществляется следующее испытание.с кодом условной вероятностя Р(1Х) (расположенным по указанному исполнителд но у адресу), исходом которого является случайное событие, предположим, с нулевым значением. Этот сформированный нуль представляет собой очередной разряд случайного числа. После зтого динамическая метка вместе с уже сформированными разрядами случайног числа снова сдвигаются на один раз ряд в сторону старших. Тем самым в соответствии с выражениями (1) и (2) Формируется очередной ИА БА + 100 + 010 (на фиг.2 этому исполнительному адресу соответствует конец перехода Ш). Далее осуществляется следующее испытание с кодом условной вероятности Р(10Х) (расположенным по указанному исполнительному адресу),, и т.д. Описанный алгоритм функционирует до тех пор, пока после очередного сдвига в сторону старших разрядов динамическая метка не займет определенного местоположения, которое распознается при помощи кода статической метки. После этого не-происходит очередного испытания, и имею окончально сформированное случайное число в форме с фиксированной точко подчинякицееся тому или иному закону распределения. Таким образом, в использованном алгоритме осуществлено совмещение процедур формирования случайного числа и исполнительных адресов выборки из блока 6 памяти кодов услов ных вероятностей для формирования очередной разрядной, цифры случайного числа. Кроме того, примененное специальное расположение кодов условных вероятностей в блоке 6 памяти, необходимое для реализации указанного алгоритма, позволяет эффективно использовать весь объем памяти, так как в нем отсутствуют пропуски между отдельными частями информации (в общем случае различной величины)j относящимися к различным законам распределения, что повышает эффективность работы датчика случайных чисел в целом. Расширение эксплуатационных возможностей; датчика случайных чисел, , а именно возможность формирования случайных величин,представляемых набором параметров, достигается тем, что для формирования кодов необходимых исполнительных адресов блока 6 памяти, по которым хранят- ся заранее занесенные туда парамеЧ ры случайных величин, применяется специальное расположение в- блоке 6 памяти зтих параметров, а также используются коды сформированного случайного числа в форме с фиксированной точкой и динамической метки. При этом 1-й исполнительный адрес блока 6 памяти, по которому из последнего читается 1-й параметр случайной величины, определяется выражениями (t) и (2) при полностью сформированном случайном числе в форме с фиксированной точкой, вхо,дящем в выражение (2), а 2-й и последующие исполнительные адреса, по которым читаются соответствующие параметры, определяются следую1ЦИМ выражением: ИА ИA., + ДМ, (3) где i 2, 3, 4, ..... Пусть (фиг.З) двухразрядное случайное число в форме с фиксированной точкой используется для чтения из блока 6 памяти его эквивалента случайной величины, представляемой ДВУМЯ параметрами п: и j (j 1,2, 3,А; максимальная величина ). Эти два параметра можно рассматривать, например, соответственно как мантиссу и порядок случайного числа в форме с плавающей точкой. Допустим, что при формировании двухразрядного случайного числа в форме с фиксированной точкой, исхо

ом последнего испытания с кодом условной вероятности Р(ТХ) (расположенным по последнему исполнительному адресу на фиг.З этому исполнительному адресу соответствует начало перехода 1) является случайное событие с нулевым значением. Этот сформированный нуль представляет собой последний (младший) разряд случайного числа в форме с фиксированной точкой, использование которого оказывается удобным для формирования необходимого исполнительного адреса и выборки по нему из блока 6 памяти мантиссы п . .Для этого динамическая метка вместе с уже сформированной двумя разрядами случайного сдвигаются, как и ранее, на один разряд в сторону . Тем самым в соответствии с выражениями (1) и (2) формируется ИА, БА+100+010 (на фиг.З этому исполнительному адресу соответствует конец перехода 1), По этому исполнительному адресу из блока 6 памяти читается параметр п.

Для чтения соответствующего порядка Л 3 достаточно последовательно упорядоченного расположения величины Л; в -блоке 6 памяти непосредственно за массивом величин П и формирования необходимого исполнительного адреса параметра путем прибавления к коду исполнительного адреса параметра п: кода динамической метки. Тем ; самым для рассматриваемого примера в соответствии с выражением (3) HAg (БА+0110)+0100 ( на фиг.З этому исполнительному адресу соответствует конец перехода И). По этому исполнительному адресу из блока 6 памяти читается следующий параметр,. Процесс формирования следующего исполнительного адреса согласно выражению (3) может быть продолжен сколь угодное число раз.

Таким образом, для каждого сформированного случайного числа в форме с фиксированной точкой из блока 6 памяти выбирается набор параметров, представляющих случайную величину, причем последняя При этом является случайным сформированным числом.

Применяя этот принцип формирования исполнительных адресов добавлением к предыдущему исполнительному адресу динамической метки согласно

выражению (3), можно использовать предлагаемьй датчик случайных чисел для получения либо случайных чисел в форме с фиксированной точкой Повьшенной точности, либо случайных чисел в форме с плавающей точкой, либо случайных величин, представляемых набором параметров} все это расширяет эксплуатационные возможности

датчика.

Описание динамики .функционирования предлагаемого датчика случайных чисел.

Перед началом работы в блок 6 памяти занесена необходимая информация, а на информа1;ионных входах Базовый адрес датчика присутствует выставляемый с наборного поля код необходимого базового адреса (а именно

0 расположенного в начале той части памяти, в которой записаны коды вероятностей требуемого закона распределения, фиг,2),

В последующей работе датчика

5 можно вьщелить следующие режимы, которые датчик реализует последовательно в следующем порядке: 1 . 2 - Установка ; 3 - Под- . готовка ; 4 - Формирование случайд ного числа ; 5 - Чтение параметров случайной величины.

Режимы с второго по пятый вклю- . чительно иллюстрируются временными диаграммами сигналов (фиг,4-7 соответственно) ,

Режим Сброс начинается при . появлении на первом сигнальном входе Сброс датчика импульса единичного значения. Передний (положительный) фронт этого импульса, пройдя через вход Х1 блока 2 управления, поступает на входы сброса R регистра 18, счетчика 26 и триггера 20 (для последнего - через элемент ИЛИ 21), обнуляя их содержимое,

При этом на выходе У8 блока 2 устанавливается единичное значение сигнала, а на выходах У1-У7, У9 и У10 нулевые значения. Нулевое значение сигнала с выкода У6 блока 2, присутствуя на входе режима блока 6 памяти, соответствует режиму Чтения информации из последнего и, присутствуя на входе стробирования второго коммутатора 11, открывает

5 последний. Нулевые значения сигналов с выходов У4 и У5 блока 2, присутствуя на входах коммутации первого 1 и второго 11 коммутаторов соответственно, настраивают их напропускание информации .с их первых групп информационных входов; для блоки i - базового адреса, для бло ка 11 - относительного адреса от регистра 10, Импульс сброса, пройдя через; первый вход элемента ШШ-НЕ 3 (где он инвертируется),своим задним (п ложительньм) фронтом (чем достигается необходимая задеряоса) заносит с выхода первого коммутатора 1 в первый регистр 4, код базового адреса, который при этом появляется на входах сумматора 5 в качестве первой состдвлякмцей исполнительног адреса. Режим Установка (фиг.4) начин ется при появлении на втором сигнал ном входе Пуск датчика импульса единичного значения, который по входу сброса R регистра 10 обнуляе его содержимое. Нулевой код с выхода блока 10 через второй коммутатор 11 появляется на входах сумматора 5, на выходах которого при этом формируется код исполнительного адреса, равный базовому.Чере вход Х2 блока 2 управленияединич-ное значение сигнала пуска появляе ся на информационном входе DR регистра 18 и через задержку,обуслов ленную прохождением сигнала через элемент ИЛИ 19, своим передним (по ложительньм) фронтом заносит еди1ш цу в первый разряд регистра 18. Те самым на первом .выходе последнего (фиг.1, крайний верхний) появляется сигнал единичного значения, который через выход У9 блока 2 и эле мент ИЛИ 8 поступает на информационный еход DR регистра 10. Штульс пуска, поступая также на установоч ный вход S триггера 20, своим передним (положительным) фронтом взводит его{ при этом яа его выходе появляется сигнал единичного значения, который через элементы И.22 (по второму инверсному входу эТот Злемент открыт сигналом нулевого значения, поступающим с выхода совпадения меток схемы 12 сравнения) и ШШ 21 и выход УЮ блока 2 поступает на вход стробирования блока 6 памяти, вызывая тем са мым появление на его выходе информации, хранящейся по исполнительному (базовому)адресу (фиг.2). 510 Кроме того, сигнал единичного значения с выхода триггера 20 поступает на вход элемента 17 задержки и, по истечении-некоторого времени, определяемого, последней и необходимрго для установки,на выходе блока 6 памяти информации, .появляется на управляющем входе генератора 16 импульсов, вызьшая его запуск; при этом на его выходе появляется по-. следовательность импульсов длительность периода которой определяется быстродействием используемой элементной базы датчика. Импульсы единичного значения с выхода генератора 16 поступают на вход распределителя 15 импульсов, с выходов v° которого снимаются-три последовател -; ности синхронизирушцих импульсов СИ1, СИ2 и СИЗ (фиг.8)./ Ретким Подготовка (4иг.5) начинается при появлении на выходе У7:; блока 2 управления импульса единичного значения, источником которого ; . является сигнал СИ1 с первого выхо- . да распределителя 15 И14пульсов проходящий .через элемент И 22j (по ВТОрому входу этот элемент открыт сигналом единичного значения .с первого выхода регистра 18). Этот импульс поступает на вход записи С второго регистра 9 и CBOIOI передним (положительньЫ) фронтом заносит в него, информацию с выхода блока 6 базовому адресу. При этом-на выходах регистра 9 появляется код: статичеЪ.--.кой (неподвижной) метки,.так как у регистра 9 используются только те егсГвыходы, которые соответствуют расположению в нем кода статической метки. (фиг.2, правая часть слова памяти по базовому адресу). Этот код представляет собой единственную единицу в каком-либо разряде на выходах регистра 9. Сигнал СИ1 через.элементы И 22 и ИЛИ 23 (в последнем сигнал инвертируется) и через выход У8 блока 2 поступает на вход записи С регистра 10 и своим задним (положительным) фронтом (чем достигается необходимая задержка) заносит в i его первый (младший)разряд (.1, крайний верхний) единицу, присутствующую на его, информационном.входе DR, Эта единица представляет собой, динамическую метку, в дальнейшем перемещающуюся в регистре 10 в сторону его старших разрядов (на фиг. 1 вниз). Код динамической метки с выходо.в регистра 10 через второй коммутатор 11 поступает на сумматор 5 и складьшается там с базовым адресом, так что на выходе последнего появляется код исполнительного адреса, равный увеличенному на единицу коду базового адреса. Поскольку по-прежнему сигнал навходе режима блока 6 памяти имеет нулевое значение (что соответствует режиму чтения ), а на его входе стробирования - единичное (что соответствует разрешению выборки информации), то на его выходе появляется информация, хранящаяся по сформированному исполнительному адресу (на фиг,2 этому исполнительному адресу соответствует конец перехода 1). Эта информация представляет собой код условной вероятности Р(X), который поступает на вероятностньй преобразователь 7.

Сигнал СИ2 через элементы И 22 (.по второму входу эта схема открыта сигналом единичного значения с первого выхода регистра 18) и ШШ 1 . (в последнем сигнал инвертируется) поступает на вход записи С регистра 18 и своим задним (положительным фронтом (чем достигается необходима задержка) сдвигает в последнем единицу из первого разряда во второй; при,этом сигнал на информационном входе DR регистра 10 приним.ает нулевое значение,

, Режим Формирование случайного чи:сла (фиг.6) начинается при появлнии на выходе У1 блока 2 импульса единичного значения, источником которого является сигнал СИ2, проходящий через элемент И 22 (по второму входу эта схема открыта сигналом единичного значения с второго выход регистра 18), Этот импульс поступает на вход записи вероятностного преобразователя 7 и своим передним (положительным) фронтом заносит в него код условной вероятности, присутствующий на выходе блока 6 памяти (считанный по исполн14тельному адресу последнего). При этом на выходе вероятностного преобразователя 7 устанавливается код случайного события ( сигнал нулевого или единичного значения), представляющий

собой очередной разряд случайного числа, подчиняющегося тому или ино му закону распределения, а именно тому, коды условных вероятностей

которого находятся в той части блока 6 памяти, которая начинается соответствующим базовым адресом. Этот код случайного события через элемент ИЛИ 8 поступает на информаQ ционный вход DR регистра Ю игнал на фиг.6) соответствует случаю, когда код случайного события, возникающий на выходе вероятностного преобразоватрля 7 при его первом срабаты-г

5 вании, представлен единичным значелИем).

Сигнал СИ2 через элементы И 22 и ИЛИ 23 (в последнем он инвертируется) и выход УВ блока 2 поступает

Q на вход записи С регистра 10 и своим задним (положительным) фронтом .(чем достигается необходимая задержка) заносит в его первый разряд код случайного события, присутствующий на его информационном входе DR (выработанный вероятностным преобразователем 7). При этом динамическая метка в регистре 10 сдвигается в его второйразряд. Появляющийся при этом на выходе регистра 10 код, представляющий собой относительньй адрес согласно выражению (2), через, второй коммутатор 11 поступает на сумматор 5 и складывается там с базовьм адресом, так что на выходе

5 последнего появляется код исполнительного адреса согласно выражению (Ijl При этом на выходе блока 6 памяти по- является очередной код условной вероятности (фиг.2), который поступает

на вероятностньй преобразователь 7.

Появляющийся на выходе регистра 0 после своего оче.редного сдвига код динамической метки сравнивается на

5совпадение с кодом статической метки, хранящимся во втором регистре 9, Такое сравнение происходит на элементах И 31 схемы 12 сравнения. Если совпадение не имеет места, то

0 на инверсных выходах всех элементов И 31 сохраняются сигналы единичного значения и, следовательно, на выходе элемента ИЛИ 29 сигнал совпадения меток по-прежнему имеет нулевое значение. При этом описанный вьше этап формирования очередного разряда случайного числа повторяется, что приводит к очередному сдвиГУ динамической метки в регистре 10 в сторону его старших разрядов.

Наконец, после очередного сдвига в регистре 10 динамической метки в схеме 12 происходит совпадение местоположений статической и динамической меток (что означает окончание формирования случайного числа в форме с фиксированной точкой); при этом .на инверсном выходе соответствующего элемента И 31 появляется сигнал нулевого значения, который через соответствующий инверсный вход элемента ШШ 29 единичным значением, свидетельствующим о совпадении меток, поступает в блок 2 через его вход ХЗ. При этом элемент И 222 закрывается и сигнал на выходе У10 блока 2 (на входе стробирования блока 6 памяти принимает нулевое значение, чем запрещается обращение к блоку 6 памяти.

Сигнал СИЗ через элемент И 24 (по второму и третьему входам открыт сигналами высокого уровня, поступающими с второго выхода регистра 18 и с выхода совпадения меток схемы 12 сравнения соответственно) и ИЛИ 19 (в последнем сигнал инвертируется) поступает на вход записи С регистра 18 и своим задним (положительным) фронтом (чем достигается необходимая задержка) сдвигает в последнем единицу из второго разряда в третий; при этом сигнал, принимающий на выходе У6 блока 2 еди- ничное значение, соответствует для блока 6 памяти режиму записи, а для второго коммутатора 11 - запрету передачи через него информации, вследствие чего сумматор 5 формирует на своем выходе код исполнительного адреса, равный базовому, I

К этому моменту времени на выходах элементов И 30 схемы 12 сравнения присутствует код сформированного случайного числа (кроме его младшего разряда), который проходит через элементы И 30 от регистра 10, В этом коде отсутствует единица, соответствующая динамической метке: сигнал нулевого значения, возникающий на инверсном выходе соответствующего элемента И 31 при совпадении меток, либо закрывает соответствующий элемент И 30, если сформированное случайное число имеет меньше S разрядов (т,е. динамическая

.метка, присутствующая в старшем разряде кода, принимаемого от регистра 10, оказывается замаскированной статической меткой), либо

оказывается за пределами разрядной сетки случайного числа, если последнее имеет S разрядов (в последнем; случае совпадение меток происходит на крайнем правом иа фиг,1 эле-менте И 31 схемы 12),

Таким образом, изменяя местоположение единицы в той части слова памяти по базовому адресу блока 6 памяти, которая отведена под код

статической метки (фиг,2), можно в конечном итоге формировать случайные числа в форме с фиксированной точкой различной разрядности по одному и тому же закону распределения, что определяется требуемой точностью в том или ином случае.

Следующий сигнал СИЗ через элементы И 2.2 (по второму входу открыт сигналом единичного значения с

третьего выхода регистра 18) и

ИЛИ 212 и выход У10 блока 2 поступает , на вход стробирования блока 6 памяти, осуществляя тем самым запись в него кода сформированного случайного числа по базовому адресу (схема блока 6 памяти организована таким образом, что запись по базовому адресу осуществляется только в ту часть слова памяти, которая отведена под код случайного числа, фиг,2),

С выхода элемента И 22 сигнал одновременно через выход У2 блока 2 поступает на выход датчика в виде первого импульса сопровождения (ИС1),

по переднему (положительному) фронту которого другие устройства могут принять сформированное случайное число, присутствующее на выходах Вых,1 датчика. Это случайное число с целью увеличения его разрядности может быть дополнено младшими разрядами, например, снимаемыми с выхода блока формирования равномерно распределенных случайных чисел, вхо-; дящего в состав вероятностного преобразователя 7 (на фиг,1 соответствующие схемы не показаны).

С выхода элемента И 22 сигнал одновременно через элемент ИЛИ 19 55 (где он инвертируется) поступает на вход записи С. регистра своим задним (положительным) фронтом (чем достигается необходимая задержка) сдвигает в последнем единицу из третьего разряда в четвертый} при этом сигнал, принимающий на выходе блока 2 нулевое значение, возвращае блок 6 памяти В режим чтения и открывает второй коммутатор 11, вслед ствие чего сумматор 5 формирует на своем выходе код исполнительного адреса в соответствии с выражениями (1) и (2); на фиг.З этому исполнительному адресу соответствует конец перехода 1, Сигнал единичного значения с четвертого выхода регистра 18 через элементы ИЛИ 23 и ИЛИ. 21 j, и выход У10 блока 2 разрешает выборку информации из блока 6 памяти, хранящейся по исполнительному адресу. Одновременно сигнал единичного значения с выхода элемента ИЛИ 23 через выход У4 блока 2 поступает на вход коммутации первого кo в yтaтoра 1, настраивай его на пропускание информации с второй группы информационных входов (кода исполнительного адреса с выхода сумматора 5), -« Дальнейшая работа датчика определяется положением переключателя 2 Если последний находится в левом 1 положении (фиг,1), то очередной сиг , нал СИЗ, проходя через элемент И 22 (по второму входу открыт сигналом единичного значения с четвертого вы хода регистра 18), переключатель 25 и элемент ИЛИ 21, на вход сброса R триггера 20, своим передним (положительным) фронтом сбрасывает его, вследствие чего генератор 16 импульсов прекращает свою работу, В дальнейшее работа датчика по .формированию очередного случайного числа в форме с фиксированной точкой повторяется аналогичным образом Режим -Чтение параметров случайной велич1; ны(фиг.7) реализуется в то случае, если переключатель 25 находится в правом положении (фиг, Этот режим начинается при появлении на выходе УЗ блока импульса единичного значения, источником которого является сигнал СИЗ, прохоДящий через элемент И 22 (по второму входу открыт сигналом едини ного значения с четвертого выхода регистра 18), переключатель 25 и элемент ИЛИ 23. Этот импульс на вы ходе датчика представляет собой второй импульс сопровождения (ИС2) по которому другие устройства могут принять первый параметр случайной величины, присутствзгющий на вы-, ходах Вых,2 датчика. Этот первый параметр представляет собой инфор-мацию, прочитанную из блока 6 памяти по исполнительному адресу, сформированному в конце предьщущего режима Формирование случайного числа и определяемому выражениями (1) и (2) при полностью сформированном случайном числе, входящем в вьфажение (2); на фиг.З этому исполнительному адресу соответствует конец перехода 1), Одновременно сигнал с выхода УЗ блока 2 поступает на второй вход элемента Ш1И-НЕ 3, где он инвертируется, и своим задним (положительным) фронтом (чем достигается необходимая задержка ) заносит в первый регистр 4 код исполнительного с выхода сумматора 5 через первый коммутатор 1, Одновременно сигнал с выхода элемента И 22 через переклю тель 25 и элемент ИЛИ 19 (где он инвертируется) поступает на вход записи С регистра 18 и своим задним (положительным) фронтом(чем достигается необходимая задержка) сдвигает в последнем единицу из четвертого разряда в пятый; при этом на выходе У5 блока 2 появляется сигнал единичного значения, которьй настраивает второй коммутатор 11 на пропускание информации с второй группы ин ормационньпс входов, а именно кода статической метки с выхода второго регистра 9, Поскольку при этом статическая метка проходит через тот же разряд коммутатора .11, через который проходила и динамическая метка перед его переключением, то в данном случае код статической метки равнозначен коду динамической. Сигнал единичного значения с пятого выхода регистра 18 по-прежнему через элемент ИЛИ 23 и выход У4 блока 2 удерживает первый соммутатор 1 на пропускание кода исполнительного адреса с выхода сумматора 5 и далее через элемент ИЛИ 21 и выход У10 блока 2 разрешает выборку информации из блока б памяти. После переключения, второго коммутатора 11 на выходе сумматора 5 формируется код следующего испол-т

нительного адреса (в данном случае ИА,) согласно вьфажению (3); на выходе блока 6 памяти появляется следующий, в данном случае второй, параметр случайной, величины, расположенньй по этому исполнительному адресу ( последнему соответствует конец перевода II).

На выходе УЗ блока 2 вновь появляется импульс единичного значения, источником которого является следующий сигнал СИЗ, проходящий через элементы И 22 (по второму входу этот элемент открыт сигналом единичного значения с пятого выхода ре гистра 18) и ЩШ 23. Этот импульс является очередным сигналом ИС2, по которому другие устройства могут принять второй параметр случайной величины, присутствзпощий на выходах Вых,2 датчика. Одновременно сигнал с выхода УЗ блока 2 вновь заносит в первьй регистр 4 код исполнительного адреса с выхода сумматора 5j при этом на выходе последнего формируется код очередного исполнительного адреса согласно выражению (3), по которому из блока 6 памяти вновь читается очередной параметр случайной величины и т.д.

С выхода элемента. ИЛИ 23 сигналы одновременно поступают на счетный вход С счетчика 26 и своим зад-i ,ннм (отрицательным) фронтом (че достигается.необходимая задержка) прибавляет в него единицу.

Описанный процесс чтения пари- метров, случайной величины из блока 6 памяти.повторяется аналогичным образом до тех пор, пока счетчик 26 не переполнится .и не вцдаст сигнала ; . положительного перепада, который ; через элемент ШШ 2If своим положительным фронтом сбросит триггер 20, вследствие чего генератор 16 импульсов прекращает свою работу.

В дальнейшем работа датчика повторяется аналогичным образом.

c/Tjfvat/нл/х vace/f

C ffSff

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор случайных процессов | 1984 |

|

SU1309021A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| Вероятностное устройство для решения краевых задач | 1982 |

|

SU1101838A1 |

| Генератор случайных процессов | 1981 |

|

SU985786A1 |

| Генератор случайных чисел | 1987 |

|

SU1495788A1 |

| Генератор многомерных случайных величин | 1982 |

|

SU1084791A1 |

| Устройство для моделирования алгоритма деятельности человека-оператора | 1989 |

|

SU1621042A1 |

| Генератор случайных чисел | 1980 |

|

SU922738A1 |

| Программируемый контроллер | 1988 |

|

SU1642446A1 |

| Устройство управления взаимным доступом процессора многопроцессорной системы | 1989 |

|

SU1631548A1 |

ДАТЧИК СЛУЧАЙНЫХ ЧИСЕЛ, содержащий блок управления, элемент ИЛИ, элемент ИПИ-НЕ, первый регистр памяти, блок памяти, группа выходов которого соединена с группой входов вероятностного преобразователя соответственно, о т л и ч а root и и с я тем, что, с целью упрощения датчика, он содержит сумматор, схему сравнения, два коммутатора, второй регистр памяти, регистр сдвига, наборное поле, а блок управления содержит триггер, переключатель, счетчик, регистр сдвига, распределитель импульсов, восемь элементов И, генератор импульсов, элемент задержки, элемент ИЛИ-НЕ ,элементов ИЛИ, выходы первого элемента ИЛИ и первого и второго элементов И блока управления соединены соответственно с первым, вторым и третьим входами второго элемента ИЛИ блока управления, выход которого соединен с синхронизирующим входом блока памяти. группа выходов которого соединена с группой информационных входов ,второго регистра памяти соответственно, выход третьего элемента И блока управления соединен с ,синХРОНИЗИРУКЩШ4 входом второго ре- : гистра памяти и с первым входом элемента ИЛИ-НЕ- блока управления, выход которого соединен с синхронизирующим входом регистра сдвига, выход четвертого элемента И блока управления соединен с торым входом элемента ИЛИ-НЕ блока управления и с управляющим входом вероятностного преобразователя, выход I которого соединен с первым входом элемента ИЛИ, выход которого соеди(Л нен с информационным входо14 регистС ра сдвига, установочный вход которого является входом Пуск датчика и соединен с информационным входом регистра сдвига блока управ- ления, с единичным входом триггера и с прямым входом третьего элемента ИЛИ блока управления, выход которого соединен с синхронизирующим входом регистра сдвига блока; управ ления, установочный вход которого является входом Сброс датчика и соединен с первым входом элемента ИЛИ-НЕ, с первым входом четвертогоэлемента ИЛИ блока управления и с установочным входом счетчика,выход переполнения которого соединен с вторым входом четвертого элемента ИЛИ блока управления, выход которого соединен с нулевым входом триггера, единичный выход которого соединен с прямым входом второго iэлемента И блока управления и с

ч

§

и

Ъ

Фив. 2

лг.

h

Memru Mt tfffHtJta

3«rmic (TV

Метки fofatrJra Фав.д

fj jj

Чтение па-Vmet uf параметра Jранет pa 2.

с/ г; г Urt

Физ. 7

с/г

| ПАТЕНТНО- ^ft '^ Т[.ХпИЧ!:ГиЛЙ ^^ш.голизидйБИБЛИОТЕКА | 0 |

|

SU185569A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Датчик случайных чисел | 1980 |

|

SU888115A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| УСТРОЙСТВО ДЛЯ ГЕНЕРИРОВАНИЯ СЛУЧАЙНЫХ ЧИСЕЛ С ЗАДАН'НЫМИ ЗАКОНАМИ РАСПРЕДЕЛЕНИЯ | 1972 |

|

SU430368A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-12-23—Публикация

1983-08-31—Подача