(54) ВЕРОЯТНОСТНОЕ УСТРОЙСТВО ДЛЯ РЕШЕНИЯ КОНЕЧНО-РАЗНОСТНЫХ УРАВНЕНИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Вероятностное устройство для решения конечно-разностных уравнений | 1981 |

|

SU1051539A1 |

| Вероятностное устройство для решения конечно-разностных уравнений | 1981 |

|

SU1160434A1 |

| Вероятностное устройство для решения уравнения Лапласа | 1981 |

|

SU1057956A1 |

| Вероятностное устройство для решения конечно-разностных уравнений | 1981 |

|

SU1095190A1 |

| Вероятностное устройство для решения уравнения Лапласа | 1983 |

|

SU1091172A1 |

| Вероятностное устройство для решения конечно-разностных уравнений | 1981 |

|

SU1149278A1 |

| Вероятностное устройство для решения конечно-разностных уравнений | 1972 |

|

SU477418A1 |

| Устройство для обхода сеточной области | 1982 |

|

SU1084806A1 |

| Устройство для моделирования случайных процессов | 1984 |

|

SU1223227A1 |

| Устройство для стохастических вычислений | 1977 |

|

SU744527A2 |

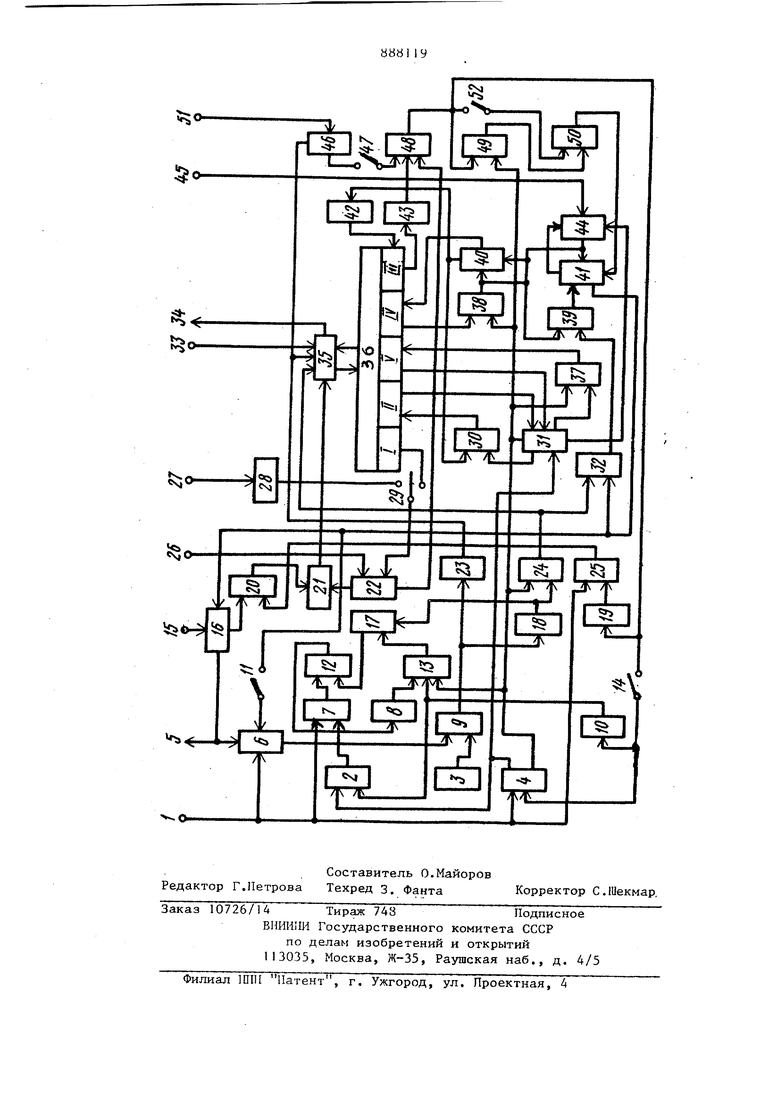

Изобретение относится к вьгчислительной технике и может быть исполь зовано для решения дифференциальных уравнений в частных производных, аппроксимированных конечно-разностными уравнениями. Известны вероятностные устройства для решения конечно-разностных уравнений .1} и С2Э, которые содержат лини задержки, логические схемы, блок оперативной памяти, соединенный с ре гистром числа, подключенным выходами значений функций к входу накапливающего сумматора, блок вероятностного блузчдания, выходы которого соед нены с выходами регистра блулдания, счетчик числа испытаний, блок анализа, входы которого соединены с выходами признака регистра числа, счетчик поиска и хранения внутренних узлов сеточной области. Недостатком этих устройств является невысокое быстродействие. Наиболее близким решением по технической сущности к изобретению является вероятностное устройство для решения конечно-разностных уравнений З, содержащее линию задержки, выход которой подключен через первую схему ИЛИ к второму входу первой схемы И, триггер начала - останова работы, вход которого соединен с вьиодом регистра стартового адреса, другой выход которого соединен с первым входом первой схемы И, выход последней подключен к первому входу регистра блуждания, второй вход которого подключен к .первому выходу управляемого вероятностного (1-М)-11ОЛ1осника, а выход - к оперативному запоминающему устройству, первый вход управляемого вероятностного (1-П)-полюсника соединен с вторым переключателем, второй выход подключен к первому входу второй схемы ИЛИ, первый вход второй схемы И подключен к триггеру начала 3останова работы, второй вход - к генератору тактовых импульсов, регистр числа, выходы которого зон вероятностей перехода, начальных и граничных условий, признаков узла и всего регистра числа в целом подключены соответственно к второму переключателю, первому входу суммирующего и усредняющего блока, к блоку анализа признаков узла и к оперативному запоминающему устройству, а выходы зон начальных и граничных условий, признаков узла и всего регистра в целом соединены соответственно с выходом третьей схемы И, выходом блока изменения признака узла и оперативным запоминающим устройством, суммируюгшй и усредняю1чий блок, первый и второй выходы которого подклю чены соответственно к первому входу третьей схемы И и первому входу про цессора, второй вход которого соеди нен с первым выходом первого управл емого счетчика - делителя, первый вход которого подключен к выходу пр цессора, а второй выход через первы переключатель - к триггеру начала останова, а также к входу регистра стартового адреса, постоянное запоминающее устройство, выход которого подключен к второму переключателю, второй управляющий счетчик - делитель, выход которого через третий переключатель подключен к третьему входу второй схемы ИЛИ, второй вход которой подключен к выходу блока анализа признаков узла, В известном устройстве для решения указанных задач моделируются случайные блуждания до попадания на границу исследуемой области. При этом за один просчет получается при ближенное решение только для одной точки, что существенно увеличивает объем вычислений для получения приближенного решения по всей области и снижает быстродействие устройства Целью изобретения является повышение быстродействия. Поставленная цель достигается . тем, что вероятностное устройство для решения конечно-разностных урав нений, содержащее блок оперативной памяти, первый вход которого является информационным входом, а первы выход - информационным выходом устройства, регистр информации, вход и выход общей информации которого соединены соответственно с вторыми 4 выходом и входом блока оперативной памяти, блок постоянной памяти, вход которого является входом задания закона распределения устройства, процессор, первый вход которого является входом установки степени точности устройства,.первьй триггер, единичный вход которого является пусковым входом устройства, генератор тактовых импульсов, первый элемент И, перBbrfi вход которого соединен с единич ным выходом первого триггера, а второй вход - с выходом генератора тактовых импульсов, счетный регистр, первый вход которого является входом начального адреса устройства, а первьй выход является выходом окончания счета устройства и соединен с нулевым входом первого триггера, первый переключатель, выход которого соединен с входом сброса первого триггера, а вход - с вторым входом счетного регистра, второй элемент И, первьй вход которого соединен с вторым выходом счетного регистра, первый элемент ИЛИ, выход которого соединен с вторым входом второго элемента И, а первьй вход - с единичным входом первого триггера, первьй элемент задержки, выход которого соединен с вторым входом первого элемента ИЛИ, первый регистр, первьй вход которого соединен с выходом второго элемента И, а выход с третьим входом блока оперативной памяти, управляемый вероятностньй (1-И)-полюсник, первьй вход задания размерности которого является входом размерности исследуемой области устройства, аадресньй выход соединен с вторым ВХОДОМ первого регистра, второй переключатель, первьй вход которого соединен с выходом блока постоянной памяти, второй входс выходом информации вероятностей перехода регистра информации, а выход - с входом задания закона распределения управляемого вероятностного ()-полюсника, третий элемент И, выход которого соединен с входом информации начальных и граничных условий регистра информации, блок усреднения, выход текущей суммы которого соединен с первым входом третьего элемента И, первьй информационный вход - с выходом информации начальных и граничных условий регистра информации, а общий информационный выход - с вторым входом S процессора, первый управляющий счетчик, первый выход которого соединен с третьим входом процессора, а первый управляющий вход - с выходом про цессора, второй управляемый счетчик управляющий вход которого является входом установки числа шагов устройства, третий переключатель, вход которого соединен с выходом второго управляемого счетчика, шифратор, выход которого соединен с входом информации положения узла регистра информации, дешифратор, вход которого соединен с выходом информации положения узла регистра информации, второй элемент ИЛИ, первыйВход которого соединен с выходом третьего переключателя, второй вход - с выходом дешифратора, а третий вход с сигнальным выходом управляемого вероятностного (1-И)-полюсника, гене ратор псевдослучайных чисел,второй регистр, формирователь импульсов чтения, формирователь импульсов записи, третий управляемьп счетчик, второй и третий триггеры, четвертый и пятый переключатели, четвертый, пя тый, шестой, седьмой, восьмой, девя тый, десятый и одиннадцатый элементы И, третий и четвертьй элементы ИЛИ И второй элемент задержки, причем единичный вход второго триггера подключен к пусковому входу устройства и соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом четвертого элемен та И, а выход - с первым входом пятого элемента И, выход пятого элемен И соединен с входом второго регистра, выход которого соединен с первым входом шестого элемента И, выход шестого элемента И соединен с первым входом генератора псевдослучайньпс чисел, первьй выход которого соедине с вероятностным входом управляемого вероятностного (1-ц)-полюсника, а вт рой выход - с вторым входом пятого :Элемента И, единичньй выход второго триггера соединен с первым входом че вертого элемента И и с первым управл ющим входом блока усреднения, выход накопленной суммы которого соединен с первым входом седьмого элемента И, нулевой выход второго триггера соединен с вторым управляющим входом блока усреднения, с вторыми входами шестого и седьмого элементов И и с первыми входами восьмого, девятого и десятого элементов И, выход первого 96 элемента И соединен с входами формирователя импульсов записи и формирователя импульсов чтения, выход формирователя импульсов записи соединен с вторым входом генератора псевдослучайных чисел и вторым входом восьмого элемента И, выход которого соединен с четвертым входом блока оперативной памяти и единичным входом третьего триггера, нулевой выход третьего триггера соединен с первым входом одиннадцатого элемента И, выход которого соединен с вторым управлякщим входом первого управляемого счетчика, второй выход первого управляемого счетчика соединен с нулевым входом третьего триггера и вторым входом счетного регистра, выход формирователя импульсов чтения соединен с пятым входом блока оперативной памяти и счетным входом второго управляемого счетчика, выход второго элемента ИЛИ соединен с вторым входом десятого элемента И, с входом первого элемента ;эадержки и с входами четвертого и пятого переключателей, выход четвертого переключателя соединен с нулевым входом второго триггера и с входом второго элемента задержки, выход которого соединен с вторым входом четвертого элемента И и с третьим входом шестого элемента И, выход пятого переключателя соединен с первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом десятого элемента И, а выход - со счетным входом первого управляемого счетчика, выход информации количества траекторий регистра информации соединен с вторым входом девятого элемента И, выход которого соединен с вторым входом одиннадцатого элемента И и первым управляшцш входом третьего управляемого счетчика, второй управлякядий вход третьего управляемого счетчика соединен с выходом процессора, первый выход - с входом информации качества траекторий регистра информации, а второй выход - с входом шифратора и вторым входом третьего эле- мента И, выход информации накопленной суммы весов регистра информации соединен с вторым информационным входом блока усреднения, а вход информации накопленной суммы весов регистра информации - с выходом седьмого элемента И. Блок-схема устройства приведена на чертеже. 7 Устройство имеет пусковой вход 1, четвертый элемент И 2, генератор 3 тактовых импульсов, второй триггер А, выход 5 окончания счета, первый триггер 6, третий элемент ИШ 7, вто рой регистр 8, первый элемент И 9, .второй .элемент 10 задержки, первый переключатель 11, пятый элемент И 12 шестой элемент И 13, четвертый переключатель 14, вход 15 начального адреса, счетный регистр 16, генератор 17 псевдослучайных чисел, формирователь 18 импульсов записи, первый элемент 19 задержки, второй элемент И 20, первьй регистр 21, управляемый вероятностный (1-)1)-полюсник 22, формирователь 23 импульсов чтения, восьмой элемент И 24j первый элемент ЮШ 25, вход 26 размерности исследуемой области, вход 27 задания закона .распределения, блок 28 постоянной памяти, второй переключатель 29, тре тий элемент И 30, блок 3 усреднения, третий триггер 32 информационньй вход 33, информационный выход 34, блок 35 оперативной памяти, регистр 36 информации, элемент И 37, девятый элемент И 38 одиннадцатый элемент И 39, третий управляемый счетчик 40, первый управляемый счетчик 41 , шифратор 42, дешифратор 43, процессор 44, вход 5 установки степени точности, второй управляемый счетчик 46, третий переключатель 47 5 второй э лемент ИЛИ 8, десятый элемент И 49, четвертый элемент ИЛИ 50, вход 51 установки числа шагов, пятый переключатель 52. Первый вход блока 35 подключен к информационному входу 33, а первьй выход - к информационному выходу 34 вторые вход и выход блока 35 соединены соответственно с выходом и входом регистра 36. Вход блока 28 под ключен к входу 27. Первый вход процессора 44 подключен к входу 45. Еди ничные входы триггеров 6 и 4 подключены к входу 1, Единичньй выход триггера 6 соединен с первым входом элемента И 9, второй вход которого соединен с выходом генератора 3. Первый вход регистра 16 подключен к входу 15, а первый вьсход - к выходу 5 и соединен с нулевым входом триггера 6. Выход переключателя 11 соединен с вторым входом сброса триггера 6. Второ выход регистра 16 соединен с первым вхо дом элемента И 20. Выход элемента ИЛИ 2 соединен с вторым входом элемента 8 И 20, а первый вход - с единичным входом триггера 6. Выход элемента I9 соединен с вторым входом элемента ИЛИ 25, Выход регистра 21 соединен с третьим входом блока 35, а первый вход - с выходом элемента И 20. Вход задания размерности управляемого вероятностного ()-пол1осника 22 подключен к входу 26, а адресный выход соединен с вторым входом регистра 21. Первый вход переключателя 29 соединен с выходом блока 28, второй вход - с выходом информации вероятностей перехода регистра 36, а выход - с входом задания закона распределения управляемого вероятностного (1-п)-полюсника 22. Выход элемента 30 соединен с входом информации начальных и граничных условий регистра 36. Выход текущей суммы блока 31 соединен с первым входом элемента И 30, первый информационный вход - с выходом информации начальных и граничных условий регистра 36, общий информационный выход - с вторым входом процессора 44. Первый выход счетчика 4I соединен с третьим входом процессора 44, а первый управляю1ЧИЙ вход - с выходом процессора 44, управляющий вход счетчика 46 подключен к входу 51, а выход соединен с входом переключателя 47, выход которого соединен с первым входом элемента ИЛИ 48е Выход шифратора 42 соединен с входом информации положения узла регистра36, Выход информации положения узла регистра 36 соединен с входом дешифратора 43, выход которого соединен с вторым входом элемента ИЛИ 48, третий вход элемента ИЛИ 48 соединен с сигнальным выходом управляемого вероятностного (1-и)полюсника 22. Единичный вход триггера 4 соединен с -первым входом элемента ИЛИ 7, второй вход которого соединен с выходом элемента И 2, а выход - с первым входом элемента И 12; выход элемента И I2 соединен с входом petHCTpa 8, выход которого соединен с первым входом элемента И 13, выход элемента И 13 соединен с первым входом генератора 17, первьй выход которого соединен с вероятностным входом управляемого вероятностного (тИ)-полюсника 22, а второй выход - с вторьм входом элемента И 12, Единичный выход триггера 4 соединен с первым входом элемента

и 2 и с первым управляющим входом блока 31, выход накопленной суммы к торого соединен с первым входом элемента И 37. Нулевой выход триггера 4 соединен с вторым управляющим входом блока 31, с вторым входами элементов И 13 и 37 и с первыми входами элементов И 24, 38.и 48. Выход элемента И 9 соединен с входами формирователей 18 и 23; выход формирователя 18 соединен с вторым входом генератора 17 и вторым входом элемента И 24, выход которого соединен с четвертым входом блока 35 и единичным входом триггера 32J нулевой выход триггера 32 соединен с первым входом элемента И 39, выход которого соединен с вторым управляющим входом счетчика 41, второй выход которого соединен с нулевым входом триггера 32. и вторым входом регистра 16. Выход формирователя 23 соединен с пятым входом блока 35 и счетным входом счетчика 46. Выход элемента ИЛИ 48 соединен с вторым входом элемента И 49, с входом элемента 19 и с входами переключателей 14 и 52, выход переключателя 14 соединен с нулевым входом триггера 4 и с входом элемента 10, выход которого соединен с вторым входом элемента И 2 и с третьим входом элемента И 13J выход переключателя 52 соединен с первым входом элемента ИЛИ 50, второй вход которого соединен с выходом элемента И 49, а выход - со счетным входом счетчика 4I. Выход информации количества траекторий регистра 36 соединен с вторым входом элемента И 38, выход которого соединен с вторым входом элемента И 39 и первым управляющим входом счетчика 40; второй управлякмций вход счетчика 40 соединен с вькодом процессора 44 первый выход - с входом информации количества траекторий регистра 36, а второй выход - с входом шифратора 42 и вторым входом элемента И 30. Выход информации накопленной суммы весов регистра 36 соединен с вторым информационным входом блока 31, а вход информации накопленной суммы всов регистра 36 - с выходом элемента И 37.

Назначение элементов устройства следующее: на пусковой вход 1 подается сигнал Начало счета, генератор 3 задает временную сетку работы

; устройства; триггер 4 управляет режимами первого.и второго проходов траектории блуждания, с выхода 5 поступает сигнал Окончание счета, с 5 помощью триггера 6 Осуществляется пуск и останов устройства, регистр 8 предназначен для запоминания исходного состояния генератора 17 перед началом первого прохода траектории

О блуждания, переключатель 14 используется в двухпроходном режиме при решении задач эллиптического типа на вход 15 поступает сигнал выборки начального адреса, регистр 16 фиксирует адрес исследуемого узла области, формирователь 18 служит для тактирования работы генератора 17, переноса информации из регистра 36 числа в блок 35 и сброса триггеЮ ра 32, регистр 21 состоит из реверсивных счетчиков координат и обеспечивает возможность решения задач в одно-, двух- и трехмерных областях, управляемый вероятностный (Hbi)2$ полюсник 22 предназначен для вероятностного преобразования информации и реализации с помощью псевдослучайных чисел закона блуждания частицы по узлам сеточной области ,

Q формирователь 23 служит для тактирования выборки информации из блока 35 в регистр числа 36; на вход 26 подается сигнал установки размерности исследуемой области путем переключения выходов управляемого

35 вероятностного (If и)-полюсника 22, на вход 27 подается сигнал задания закона распределения блуждания частицы по узлам сеточной области,

,« в блоке 28 хранятся значения вероятностей переходов из исследуемого узла в соседние узлы, блок 31 предназначен для получения среднего арифметического веса по траекториям, начинакяцимся с узла, для ко45торого находится решение, триггер 32 управляет коррекцией числа испытаний для каждой новой стартовой точки, кроме первойJ на информационный вход 33 поступают сигна50лы значений законов вероятностных переходов, начальных и граничных условий, признаков граничных и внутренних узлов; с информационного выхода 34 выдаются результаты реше55ния, регистр 36 предназначен для

организации обмена анализируемой и результирующей информации, по виду информа1.у1и, заносимой в регистр числа, все его разряды можно разде лить на пять зон: содержимое перво узоны определяет вероятности переходов из данного узла в соседние, содержимое второй зоны определяет начальные и граничные условия, содержимое третьей зоны определяет принадлежность данного узла к внут ренней части области границы или внешней части области, содержимое четвертой зоны формируется во время повторного прохода и определяет количество траекторий, прошедших через данный узел, содержимое пятой зоны формируется и используется при повторном проходе траектории и определяет накопленную сумму весов по всем траекториям, прошедшим через данный узел; третий управляемьй счетчик предназначен Для подсчета числа траекторий, прошедших через данный узел, и для обеспечения точно испытаний для исследуемого узла,- cчeтчик 41 обеспечивает построение точно траекторий из данного узла, шифратор 42 предназначен для выработки кода 1 1 , соответствующего признаку граничного узла и маркировки этим кодом узлов, для которых найдено решение; дешифратор 43 осуществляет дешифрированиесодержимого йоследних двух разрядов третьей зоны регистра 36 с целью фиксирования окончания построения одной тра ектории, когда последняя попадает на границу; процессор 44 осуществляет вычисление дисперсии веса и определение требуемого числа испытаний N значение которого заносится в счетчики 40 и 42, на вход 45 подается сигнал для установки необходимой точности решения (f с заданной надежностью вычислений (Ь , переключатель 47 вклю чается при решении параболических управлений, на вход 51 подается си нал для установки числа К шагов путем изменения коэффициента деления счетчика 46 при решении парабо лических уравнений, с помощью пере ключателя 52 осуществляется перево устройства в режим одного прохода траектории. Предлагаемое устройство обеспечивает возможность решения краевых задач, аппроксимированных конечноразностными уравнениями, в режимах одного и двойного проходов траек 12тории блуждания, причем блуждание осуществляется с помощью псевдослучайных чисел. В режиме одного прохода траектории решаются задачи параболического типа и могут решаться задачи эллиптического -типа. Режим двойного прохода траектории реализует ускоренный метод решения задач эллиптического типа, когда каждая траектория случайного блуждания используется для получения оценки решения в различных точках одновременно. При этом возникает необходимость воспроизведения траектории блуждания с тем, чтобы присвоить полученный по данной траектории вес не только стартовому узлу, но и всем промежуточным узлам траектории. Использование генератора псевдослучайных чисел (ГПСЧ делает возможным воспроизведение любой траектории блуждания. Для этого достаточно восстановить состояние ГПСЧ,- соответствующее началу данной траектории. Работа устройства в режиме двойного прохода траектории блувдания, реализующего ускоренный вариант решения задач эллиптического типа методом последовательного сокращения размерности системы для случая плоской задачи, происходит следующим образом. После ввода исходных данных в блок 35 по информационному входу 33, установки стартового адреса (х ут) в счетном регистре 16 по входу 15 и переключения устройства в режим двойного прохода траектории (переключатель 14 замкнут переключатель 52 - разомкнут) на пусковой вход 1 устройства подается сигнал Начало счета, который переводит триггер 6 в единичное состояние, осуществляет с помощью элементов ИЛИ 7 и И 8 запись исходного числа из генератора 17 в регистр 8, устанавливает триггер 4 в единичное состояние, определяиэдее первый проход траектории, и осуществляет с помощью элементов ИЛИ 25 и И 20 перенос координат начального узла Р(, из регистра 16 в регистр 21. После этого тактовые импульсы от генератора 3 начинают поступать через элемент И 9 на формирователь 23, формирующий импульсы чтения от переднего фронта тактовых импульсов, и на формирователь 18, формирующий импульсы записи от заднего фронта 13 тактовых импульсов, Координаты стартового узла из регистра 21 пос пают в блок 35, где возбуждают соответствующую ячейку. По импульс чтения из блока 35 считывается инф мация, относящаяся к данному узлу р(х-, у-) в соответствующие зоны регистра 36. При этом из второй зо ны регистра 36 в блок 31 поступает начальное значение функции в данно узле сеточной области. Одновременн из первой зоны регистра 36 через переключатель 29 в управляемый вероятностный (Н и)-полюсник 22 счит ваются значения верЪятностей: перехода из узла Р(, у-) в соседние узлы. В соответствии с этими вероятностями начинается построение тра ектории блуждания; по импульсу записи, поступающего с выхода формирователя 18 в ГСС4 17, последний формирует псевдослучайное число, в соответствии с которым на одном из выходов управляемого вероятност ного (1-тИ)-полюсника появляется си нал, определяющий направление пере мещения траектории. В результате в следующем такте в регистре 21 будет новый адрес - адрес узла, соседнего со стартовым. Далее процес построения траектории блудцания повторяется аналогично описанному. Блуждание по траектории заканчивается, если дешифратор 43 зафиксирует признак граничного узла (код 11 Траектория может закончиться не тол ко на границе, но и в том случае, если она попала в условное поглощающее состояние непосредственно с внутреннего узла. Во всех этих случаях сигнал Конец траектории с выхода элемента ИЛИ 48 подается через переключатель 14 на нулевой вход триггера 4, последний устанавливается в нулевое состояние, опред ляющее второй проход траектории. Накопленная к концу первого прохода в блоке 31 сумма является весом данной траектории для стартовой точки. Для всех промежуточных узлов траектории вес определяется в процессе повторного прохода этой траектории. Второй проход начинается с занесения координат стартово го узла из регистра 16 через элемент И 20 в регистр 21 по сигналу Конец траектории, задержанному элементом 10, и передачи содержимого регистра 8 в ГПСЧ 17 по этому же 914 сигналу. Содержимое пятой зоны регистра 36 поступает в блок 31, где увеличивается на величину веса данной траектории. Полученная сумма через элемент 37 заносится в пятую зону регистра 36, после чего происходит уменьшение веса траектории на величину содержимого второй зоны регистра 36, подготавливая этим вес для следующего узла данной траектории. Одновременно содержимое четвертой зоны регистра 36, определяющее число траекторий, прошедших через данный узел, пересыпается через элемент И 38 в счетчик 40, где увеличивается на единицу и полученное значение заносится в четвертую зону регистра 36. На этом формирование числовых данных для текущего уэла заканчивается и содержимое регистра 36 по импульсу записи записывается в ячейку блока 35 по адресу данного узла. Выбор следующего узла траектории происходит но схеме, данной при описании первого прохода. Для этого узла выполняются все действия, которые были рассмотрены для предыдущего узла. Затем переходят к следующему узлу и т.д. После окончания второго прохода каждой.траектории происходит, увеличение содержимого счетчика 41 на единицу по сигналу Конец траектории, прошедшему через элементы И 49 и ИЛИ 50, и установление второго триггера 4 в единичное состояние. Далее моделируется новая траектория из стартовой точки Р (v,yv ), осуществляется ее повторный проход и т.д. После первыхN иcпытaниa процессор 44 вычисляет в соответствии с полученными оценками М (и), iD() и значениями ji , rf или Д- требуемое число испытаний N . Это значение поступает в блок 31 и счетчики 40 и 41- После переполнения счетчика 40 вычисление функции для стартового узла заканчивается. Накопленный при этом п6 14 траекториям вес из пятой зоны регистра 36 передается в блок 31, где происходит определение среднего ари етического веса по VJ траекториям, полученное значение функции через элемент И 30 переписывается во вторую зону регистра 36, одновременно шифратор 42 изменяет содержимое третьей зоны регистра 36, определяя узел Р(х, у) как граничный, затем возбуждается адрес блока 35 к числовая информация из регистра 15 36 переписывается по указанному адресу. В дальнейших вычислениях узел Р(х, у-) будет выступать в качестве граничного. После переполнения счетчика 41, последний формирует сигнал Конец испытаний,переводящий триггер 32 в нулевое состояние и увеличивающий на единицу содержимое регистра 16. Таким образом, после окончания второго прохода в N ом испытании для стартового узла Р(х-, У ) в регистр 16 поступят координаты новой стартовой точки р (х. . у. ) по сигналу Конец траектории, задержанному элементом 19. При первом испытании во втором проходе траектории из нового стартового узла в счетчик 41 перепишется значение числа испытаний, накопленное в четвертой зоне регистра 36 по адресу данного узла за время предыдущих испытаний. Если этот узел окажется граничным или вне сеточной области, что будет сразу зафиксировано дешифратором 43, соетояние регистра 16 будет изменяться до тех пор, пока поиск не приведет снова к внутреннему узлу области. После этого, как решение будет найдено для всех внутренних узлов области, информащ5я выдается на информационный выход 34. Работа устройства в релсиме одного прохода тра ектории блуждания,аналогична работ устройства в первом проходе режима двойного прохода. Это достигается отключением цепи повторного прохода(переключатель 14 разомкнут, переключатель 52 замкнут). В режиме одного прохода траекто рии возможно решение задач парабол ческого типа(переключатель 47 замкнут) . При этом траектория может з кончиться после К шагов еще до попадания на границу. Если решение отыскивается не для всех узлов, а только для части их или для каждого узла в отдельности, то на тригг 6 подается сигнал Останов, с регистра 16 или по цепи обратной свя через переключатель 1 1. Управляемы вероятностный (17У1)-полюсник 22 мо управляться по входу 27 с помощью блока 28, в котором записываются п стоянные для всей области вероятно сти переходов из данного узла в с седние узлы или же с помощью блока 35 через первую зону регистра 36 10 (режим управления задается переключателем 29) . Режим двойного прохода траекторий, реализующий марковское свойство блуждания приводит к тому, что в информационных ячейках,соответствующих узлам сеточной области, по мере прохода через них траекторий, происходят подсчет числа траекторий и накопление суммарного веса по этим траекториям. Поэтому при выборе промежуточных узлов в качестве стартовых значительно сокращается время моделирования за счет имеющегося в этих узлах задела по траекториям. При рассмотрении всей области это дает значительное сокращение объема вычислительных затрат по сравнению с методом последовательного сокращения размерности системы, выполняемым в один п роход траек тории. / Формула изобретения Вероятностное устройство для решения конечно-разностных уравнений, содержащее блок оперативной памяти, первый вход которого является информационным входом, а первый выход информационным выходом устройства, регистр информации, вход и выход общей информации которого соединены соответственно с вторыми выходом и входом блока оперативной памяти, блок постоянной памяти, вход которого является входом задания закона распределения устройства, процессор, первый вход которого является входом установки степени точности устройства, первый триггер, единичный вход которого является пусковым входом устройства, генератор тактовых импульсов, первый элемент И, первый вход которого соединен с единичным выходом, первого триггера, а второй вход - с выходом генератора тактовых импульсов, счетный регистр, первый вход которого является входом начального адреса устройства, а первый выход является выходом окончания счета устройства и соединен с нулевым входом первого триггера, первый переключатель, выход которого соединен с входом сброса первого триггера, а вход - с вторым входом счетного регистра, второй элемент И, первый вход которого соединен с вторым выходом счетного ре17гистра, первый элемент ИЛИ, выход которого соединен с вторым входом второго элемента И, а первый вход с единичным входом первого триггера первый элемент задержки, выход которого соединен с вторым входом пер вого элемента ИЛИ, первый регистр/ первый вход которого соединен с вых дом второго элемента И, а выход - с третьим входом блока оперативной памяти, управляемый вероятностный (17У))-полюсник, первьш вход задания размерности которого является входом размерности исследуемой области устройства, а адресный выход соединен с вторым входом первог регистра, второй переключатель первый вход которого соединен с выходом блока постоянной памяти, второй вход - с выходом информации верояткостей перехода регистра информации, а выход - с входом задания закона распределения управляемого вероятностного (1тИ)-полюсника, трети элемент И, выход которого соединен с входом информации начальных и гра ничн1 1х условий регистра информации, блок усреднения, выход текущей сумм которого соединен с первым входом третьего элемента И, первый информа ционный вход - с выходом информации начальных и граничных условий регистра информации, общий информацио ный выход - с вторым входом процессора, первый управляемый счетчик, первый выход которого соединен с третьим входом процессора, а первы управляющий вход - с выходом процессора, второй управляемый счетчик управляющий вход которого является входом установки числа шагов устрой ства, третий переключатель, вход которого соединен с выходом второго управляемого счетчика, шифратор, выход которого соединен с входом информации положения узла регистра информации, дешифратор, вход которо го соединен с выходом информации по ложения узла регистра информации, второй элемент ИЛИ, первый вход которого соединен с выходом третьего переключателя, второй вход - с выходом дешифратора, а третий вход с сигнальным выходом управляемого вероятностного (1-: У)-полюсника, о т личающееся тем, что, с це лью повышения быстродействия, оно содержит дополнительно генератор псевдослучайных чисел, второй ре918гистр, формирователь импульсов чтения, формирователь импульсов записи, третий управляемый счетчик, второй и третий триггеры, четвертый и пятый переключатели, четвертый, пятый, шестой, седьмой, восьмой, девятый десятый и одиннадцатый элементы И, третий и четвертый элементы ИЛИ и второй элемент задержки, причем единичный вход второго триггера подключен к пусковому входу устройства и соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента И, а выход - с первым входом пятого элемента И, выход пятого элемента И соединен с входом второго регистра, выход которого соединен с первым входом шестого элемента И,, выход шестого элемента И соединен с первым входом генератора псевдослучайных чисел, первый выход которого соединен с вероятностным входом управляемого вероятностного (1 тУ1)-полюсника, а второй выход - с вторым входом пятого элемента И, единичный выход второго триггера соединен с первым входом четвертого элемента И и с первым управляющим входом блока усреднения, выход накопленной суммы которого соединен с первым входом седьмого элемента И, нулевой выход второго триггера соединен с вторым управляющим входом блока усреднения, с вторыми входами шестого и седьмого элементов И и с первыми входами восьмого, девятого и десятого элементов И, выход первого элемента Н соединен с входами формирователя импульсов записи и формирователя импульсов чтения, выход формирователя импульсов записи соединен с вторым входом генератора псевдослучайных чисел и вторым входом восьмого элемента И, выход которого соединен с четвертым входом блока оперативной памяти и единичным вводом третьего триггера, нулевой выход третьего триггера соединен с первым входом одиннадцатого элемента И, выход которого соединен с вторым управляющим входом первого управляемого счетчика, второй выход первого управляемого счетчика соединен с нулевым входом третьего триггера и вторым входом счетного регистра, выход формирователя импульсов чтения соединен с пятым входом блока оперативной памяти и счетным входом вто- рого управляемого счетчика, выход второго элемента ИЛИ соединен с вторым входом десятого элемента И, с входом первого элемента задержки и с входами четвертого и пятого переключателей, выход четвертого переключателя соединен с нулевым входом второго триггера и с входом второго элемента задержки, выход которого соединен с вторым входом четвертого элемента И и с третьим входом шестого элемента И, выход пятого переключателя соединен с первым входом четвертого элемента ИЛИ, второй вход кото рого соединен с выходом десятого элемента И, а выход - со счетным входом первого управляемого счетчика, выход информации количества тр.аекторий регистра информации сЪединен свторым входом девятого элемента И, выход которого соединен с вторым входом одиннадцатого элемента И и-первым управля ющим входом третьего управляемого 920 счетчика, второй управляющий вход третьего управляемого счетчика соединен с выходом процессора, первый выход с входом информации количества траекторий регистра информах ии, а второй выход - с входом шифратЯора и вторым входом третьего элемента И, выход информации накопленной суммы весов регистра информации соединен с вторым информационным входом блока усреднения, а вход информшдаи накопленной суммы весов регистра информации - с выходом седьмого элемента И. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 328475, кл. G 06 G 7/40, 1973. 2.Авторское свидетельство СССР № 369580, кл. G 06 G 7/48, 1974. 3.Авторское свидетельство СССР IP 477418, кл. G 06 F 15/32, 1976 (лрототип).

Авторы

Даты

1981-12-07—Публикация

1980-03-04—Подача