которого Соединен с первым выходом управляемого вероятностного (1-И)-полюсника, второй вход соединен с выходом первого дешифратора, третий вход соединен с выходом третьего переключателя, а выход соединен со счетным входом первого управляемого счетчика и вторым входом первого элемента ИЛИ, элемент задержки, вход которого соединен с входом первого переключателя и вторым входом счетного регистра, а выход соединен с третьим входом первого элемента ИЛИ, третий элемент И, первый вход которого соединен с вторым выходом блока усреднения, а выход соединен с третьим входом информационного регистра, отличающееся тем что, с целью повышения быстродействия, оно дополнительно содержит третий и четвертый управляемые счетчики, второй дешифратор, второй регист второй триггер, четвертый, пятый, шестой и седьмой элементы И, третий, четвертый, пятый и шестой элементы ИЛИ, причем выход третьего управляемого счетчика соединен с нулевым BXO дом первого триггера и является выходом окончания счета устройства, управляющий вход соединен с выходом блока вычисления требуемого числа испытаний, а счетный вход соединен с вторым выходом счетного регистра и нулевым входом второго триггера, единичный вход которого соединен с первым входом шестого элемента ИЛИ и подключен к пусковому входу устройства, единичный выход второго ,триггера соединен с первым входом

шестого элемента И, а нулевой выход соединен с первыми входами четвертого и пятого элементов И, вторые

входы которых соединены соответственно с выходом второго элемента И и выходом второго дешифратора, вход второго дешифратора соединен с первым выходом четвертого управляемого счетчика, второй выход которого соединен с первыми входами четвертого и пятого элементов ИЛИ, счетный вход соединен с выходом четвертого элемента И, а управляющий вход подключен к входу размерности исследуемой области устройства, второй выход управляемого вероятностного (1-п )-полюсника соединен с вторым входом шестого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, второй вход третьего элемента ИЛИ соединен с выходом пятого элемента И а выход соединен с вторым входом первого ретистра, вход второго регистра является входом установки числа узлов исследуемой области устройства, а выход соединен с первым входом седьмого элемента И, второй вход которого соединен с выходом шестого элемента ИЛИ, а выход соединен с управляюшим входом первого управляемо,го счетчика, вторые входы четвертого, пятого и шестого элементов ИЛИ подключены к второму выход;у первого управляемого счетчика, выход пятого элемента ИЛИ соединен с вторым входом третьего элемента И, выход четвертого элемента ИЛИ соединен с вторым входом счетного регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вероятностное устройство для решения конечно-разностных уравнений | 1981 |

|

SU1160434A1 |

| Вероятностное устройство для решения конечно-разностных уравнений | 1980 |

|

SU888119A1 |

| Вероятностное устройство для решения уравнения Лапласа | 1981 |

|

SU1057956A1 |

| Вероятностное устройство для решения конечно-разностных уравнений | 1981 |

|

SU1051539A1 |

| Вероятностное устройство для решения уравнения Лапласа | 1983 |

|

SU1091172A1 |

| Устройство для обхода сеточной области | 1982 |

|

SU1084806A1 |

| Вероятностное устройство для решения конечно-разностных уравнений | 1981 |

|

SU1149278A1 |

| Вероятностное устройство для решения конечно-разностных уравнений | 1972 |

|

SU477418A1 |

| Устройство для обхода узлов сеточной области | 1981 |

|

SU955084A1 |

| Устройство для обхода сеточной области | 1983 |

|

SU1080147A1 |

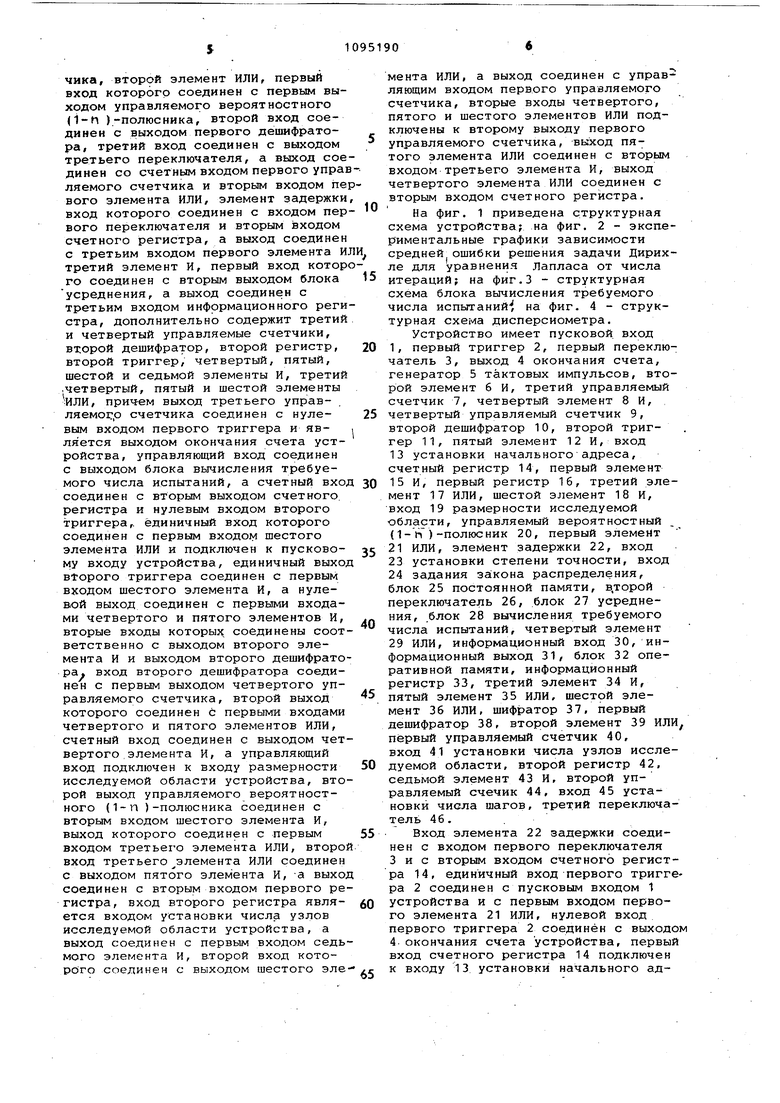

ВЕРОЯТНОСТНОЕ УСТРОЙСТВО ДЛЯ РЕШЕНИЯ КОНЕЧНО-РАЗНОСТНЫХ УРАВНЕНИЙ, содержащее блок оперативной памяти, первые вход и выход которого являются соответственно информационным входом и информационным выходом устройства, информационный регистр, первые вход и выход которого соединены соответственно с вторыми выходом и входом блока оператив ной памяти, блок постоянной памяти, вход которого является входом задания закона распределения устройства, блок усреднения вход которого соединен с вторым выходом информационного регистра, блок вычисления требуемого числа испытаний, первый вход которого является входом установки степени точностиустройства, а второй вход соединен с первым выходом блока усреднения, управляемый вероятностный

Изобретение относится к вычисли.тельной технике и может быть использовано для решения дифференциальных уравнений в частных производных, аппроксимированных конечно-раэностными уравнениями.

Известны вероятностные устройства для решения конечно-разностных уравнений, которые содержат линии задержки, логические схемы, блок оперативной памяти, соединенный с регистром числа, подключенным выходами значений функций к входу накапливаемого сумматора, блок вероят-ностного блуждания, выходы которого соединены с выходами регистра блуждания, счетчик числа испытаний, блок анализа, входы которого соединены с выходами признака регистра числа, счетчик поиска и хранения

внутренних узлов сеточной области Ul, С21 и L3T.

Недостатком этих устройств является невысокое быстродействие.

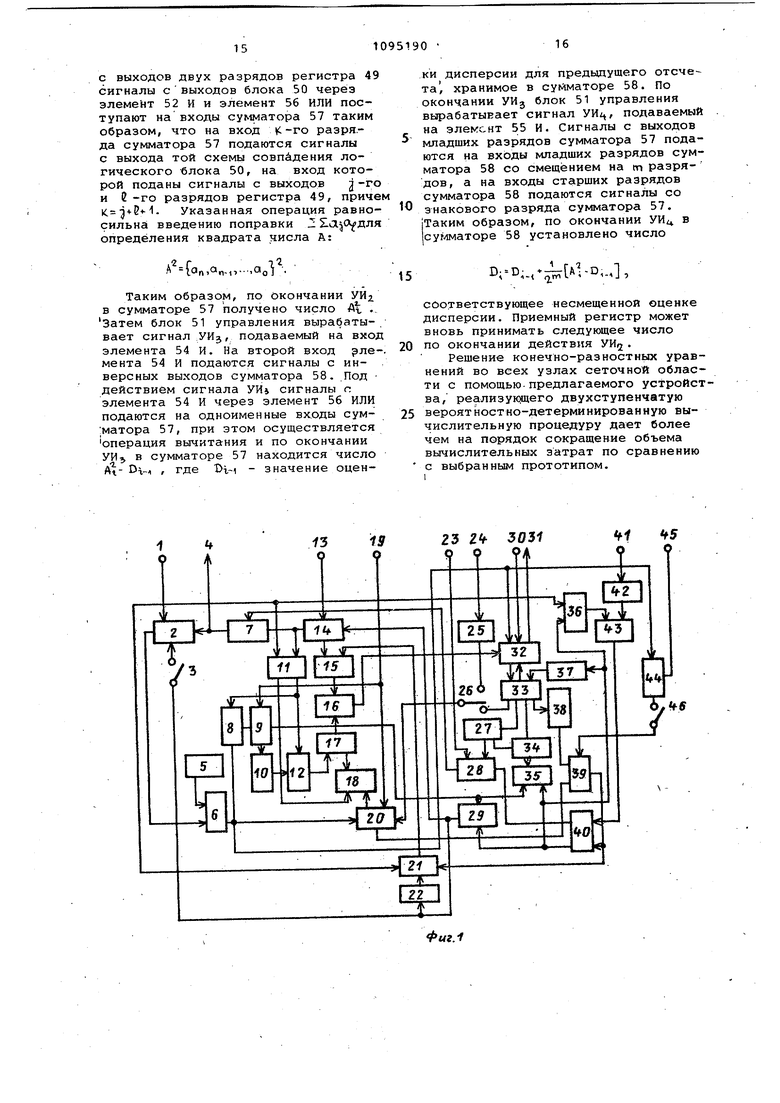

Наиболее близким к предлагаемому, по технической сущности является вероятностное устройство для решения конечно-разностных уравнений, содержащее линию задержки, выход которой подключен через первую схему ИЛИ к второму входу первой схемы И, триггер начало-останова работы, вход которого соединен с выходом регистра стартового адреса, другой выход которого соединен с первым входом первой схемы и, выход последней подключен к первому входу регистра блужданий, второй вход которого подключен к первому выходу управляемого вероятностного (1-п) полюсника, а выход - к оперативному запоминающему устройству, первый вход управляемого вероятностного (1-п )-полюсника соединен с вторым переключателем, второй выход подключен к первому входу второй схемы ИЛИ, первый вход второй схемы И подключен к триггеру начало-остано|ва работы, второй вход - к генератору тактовых импульсов, регистр числа, выходы которого с зон вероятностей перехода, начальных и граничных условий, признаков узла и всего регистра числа в целом под ключены соответственно .к второму пе реключателю, первому входу суммйрующего и усредняю цего блока к блоку анализа признаков узла и к опера тивному запоминающему устройству, а выходы зон начальных и граннчныос условий, признаков узла и всего регистра в целом соединены соответственно с выходом третьей схемы И, выходом блока изменения признака уз ла и оперативным запоминающим устройством, суммирующий и усредняющий блок, первьай и второй выходы ко торого подключены соответственно к первому входу третьей схемы И и первому входу процессора, второй вход которого соединен с первым выходом первого, управляемого счетчика делителя, первый вход которого подключен к выходу процессора, а второ выход через первый переключатель к триггеру начало-останова, а также к входу регистра стартового адреса, постоянное запоминакмцее устройство, выход которого подключен к второму переключателю, второй управляющий счетчик-делитель, выход которого через третий переключатель подключе к третьему входу второй схемы ИЛИ, второй вход которой подключен к вых ду блока анализа признаков узла Г41 Однако в известном устройстве дл решения указанных задач моделируютс случайные блуждания из стартового узла до попадания на границу сеточн области. Для. получения решения задачи по всей области с необходимой точностью ff и заданной надежностью вычисления jS проводят требуемое число испытаний .для каждого узла области (на практике ), что существенно увеличивает объем вычислений для получения приближенного решения задачи по всей области JH снижает быстродействие устройства Цель изобретения - повышение быстродействия. Поставленная цель достигается те что вероятностное устройство для ре шения конечно-разностных уравнений, содержащее блок оперативной памяти, .первые вход и выход которого являют 1ся соответственно информационным входом и информационным выходом устройства, информационный регистр, первые вход и выход которого соединены соответственно с вторыми выходом и входом блока оперативной памяти, блок постоянной памяти, вход которого является входом задания закона распределения устройства, блок усреднения, вход которого соединен с вторым выходом информационного регистра, блок вычисления требуемого числа испытаний, первый вход которого является входом установки степе;ни точности устройства, а второй вход соединен с первым выходом блока усреднения, управляемый вероятностный П-П)-полюсник, первый вход котррого яШ1Яется входом размерност.й иссле-дуемой области устройства,счетный регистр, первый вход которого является входом установки начального адреса устройства, первый элемент И, первый вход которого соединен с первым выходом счетного регистра, первый регистр, первый вход которого соединен с выходом первого элемента И, а выход соединен с третьим входом блока оперативной памяти, первый элемент ИЛИ, выход которого соединен с вторым входом первого элемента И, первый триггер, единичный вход которого соединен с первым входом первого элемента ИЛИ и является пусковым входом устройства, первый переключатель, выход которого соединен с входом сброса первого триггера, генератор тактовых импульсов, второй элемент И, первый вход которого соединен с единичным выходом первого триггера, второй соединен с выходом генератора тактовых импульсов, а выход соединен с вторым входом управляемого вероятностного (1- h)-полюсника и четвертым входом блока оперативной памяти, второй переключатель, первый вход которого соединен с выходом блока постоянной памяти, второй вход соединен с третьим выходом информационного регистра, а выход соединен с третьим входом управляемого вероятностного (1- h)-полюсника, шифратор, выход которого соединен с вторым входом инфо| мационного регистра, первый дешифратор, вход которого соединен с четвертьйл вгаходом информационного регистра, первый управляемый счетчик первый выход которого соединен с о третьим входом блока вычисления требуемого числа испытаний, а второй выход соединен с- входом шифратора, второй управляемый счетчик, управляющий вход которого является входом установки числа шагов устройства, а счетный вход соединен с выходом второго элемента И, третий переключатель, вход которого соединен с выходом второго управляемого счетчика, второй элемент ИЛИ, первый вход которого соединен с первым выходом управляемого вероятностного (1-И )-полюсника, второй вход соединен с выходом первого дешифратора, третий вход соединен с выходом третьего переключателя, а выход сое динен со счетным входом первого упра ляемого счетчика и вторым входом пе вого элемента ИЛИ, элемент задержки вход которого соединен с входом пер вого переключателя и вторым входом счетного регистра, а выход соединен с третьим входом первого элемента И третий элемент И, первый вход котор го соединен с вторым выходом блока усреднения, а выход соединен с третьим входом информационного реги стра, дополнительно содержит третий и четвертый управляемые счетчики, второй дешифратор, второй регистр, второй триггер, четвертый, пятый, шестой и седьмой элементы И, третий .четвертый, пятый и шестой элементы :ИЛИ, причем выход третьего управляемог.о счетчика соединен с нулевым входом первого триггера и является выходом окончания счета устройства, управляющий вход соединен с выходом блока вычисления требуемого числа испытаний, а счетный вхо соединен с вторым выходом счетного, регистра и нулевым входом второго триггера,, единичный вход которого соединен с первым входом шестого элемента ИЛИ и подключен к пусковому входу устройства, единичный выхо второго триггера соединен с первым входом шестого элемента И, а нулевой выход соединен с первыми входами четвертого и пятого элементов И, вторые входы которых, соединены соот ветственно с выходом второго элемента И и выходом второго дешифрато ра вход второго дешифратора соединен с первым выходом четвертого управляемого счетчика, второй выход которого соединен с первыми входами четвертого и пятого элементов ИЛИ, счетный вход соединен с выходом чет вертого элемента и, а управляющий вход подключен к входу раэмерности исследуемой области устройства, вто рой выход управляемого вероятностного (1-п )-полюсника соединен с вторым входом шестого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, второ вход третьего элемента ИЛИ соединен с выходом пятого элемента И, а выхо соединен с вторым входом первого ре гистра, вход второго регистра является входом установки числа узлов исследуемой области устройства, а выход соединен с первым входом седь мого элемента И, второй вход которого соединен с выходом шестого эле. мента ИЛИ, а выход соединен с управляющим входом первого управляемого счетчика, вторые входы четвертого, пятого и шестого элементов ИЛИ подключены к второму выходу первого управляемого счетчика, выход пятого элемента ИЛИ соединен с вторым входом третьего элемента И, выход четвертого элемента ИЛИ соединен с вторым входом счетного регистра. На фиг. 1 приведена структурная схема устройства; на фиг. 2 - экспериментальные графики зависимости средней ошибки решения задачи Дирихле для уравнения Лапласа от числа итераций; на фиг.З - структурная схема блока вычисления требуемого числа испытаний на фиг. 4 - структурная схема дисперсиометра. Устройство имеет пусковой вход 1, первый триггер 2, первый переключатель 3, выход 4 окончания счета, генератор 5 тактовых импульсов, второй элемент 6 И, третий управляемый счетчик 7, четвертый элемент 8 И, четвертый управляемый счетчик 9, второй дешифратор 10, второй триггер 11, пятый элемент 12 И, вход 13 установки начального адреса, счетный регистр 14, первый элемент 15 И, первый регистр 16, третий элемент 17 ИЛИ, шестой элемент 18 И, вход 19 раэмерности исследуемой области, управляемый вероятностный (1-h )-полюсник 20, первый элемент 21 ИЛИ, элемент задержки 22, вход 23установки степени точности, вход 24задания за1кона распределения, блок 25 постоянной памяти, в.торой переключатель 26, блок 27 усреднения, .блок 28 вычисления требуемого числа испытаний, четвертый элемент 29 ИЛИ, информационный вход 30, информационный выход 31, блок 32 оперативной памяти, информационный регистр 33, третий элемент 34 И, пятый элемент 35 ИЛИ, шестой элемент 36 ИЛИ, шифратор 37, первый дешифратор 38, второй элемент 39 ИЛИ, первый управляемый счетчик 40, вход 41 установки числа узлов исследуемой области, второй регистр 42, седьмой элемент 43 И, второй управляемый счечик 44, вход 45 установки числа шагов, третий переключатель 46. Вход элемента 22 задержки соединен с входом первого переключателя 3 и с вторым входом счетного регистра 14, единичный вход первого триггера 2 соединен с пусковым входом 1 устройства и с первым входом первого элемента 21 ИЛИ, нулевой вход первого триггера 2 соединён с выходом 4. окончания счета устройства, первый вход счетного регистра 14 подключен к входу 13 установки начального адреса устройства, а первый выход соединен с первым входом первого элемента 15 И, первый вход управляемого вероятностного (1-г )-полюсника 20 соединен с входом 19 размерности исследуемой области устройства, а второй вход соединен с выходом второго элемента 6 И, с четвертым входом блока 32 оперативной памяти и со счетным входом второго управляемого счечика 44, первый вход блока 28 вычисления требуемого числа испытаний соединен с входом 23 установки степени точности устройства, а третий вход соединен с первым выходом первого управляемого счетчика 40, вход блока 25 постоянной памяти соединен с входом 24 задания закона распределения -устройства, а выход - с первым входом второго переключателя 26, первый вход блока 32 оперативно памяти соединен с информационным входом 30 устройства, а первый выхо с информационным вцходом 31 устройства, управляющий вход второго управляемого счетчика 44 соединен с входом 45 установки числа шагов устройства, а выход соединен с входом третьего переключателя 46, единичный выход первого триггера 2 соединен с первым входом второго элемецг та 6 И, второй вход которого подключен к выходу генератора 5 тактовых импульсов, выход первого переключателя 3 соединен с входом сброса первого триггера 2, выход первого элемента 15 И соединен с первым входом первого регистра 16, д второй вход подключен к выходу Первого элемента 21 ИЛИ, выход первого регистра 16 подключен к третьему входу блока 32 оперативной памяти, вторые вход и выход которого соединены соответственно с первыми выходом , ; и входом информационного регистра 33, первый выход управляемого вероятностного {1-1Л )-полюсника 20 соединен с первым входом второго элемента 39 ИЛИ, третий вход подключен к выходу второгЬ переключателя 26, выход элемента 22 задержки соединен с третьим входом первого элемента 21 ИЛИ, второй вход которого подключен к выходу второго элемента 39 ИЛИ и к счетному входу первого управляемого счетчика 40, второй вход блока 28 соединен с первым выходом блока 27 усреднения, второй выход которого соединен с первым .входом третьего элемента 34 И, второй вход второго переключателя 26 соединен с третьим выходом информационного регистра 33, второй выход которого подключен к входу блока 27 усреднения, выход шифратора 37 подключен к второму входу информационного регистра 33, четвертый выход которого соединен с входом первого дешиф ратора 38, выход третьего элемента 34 И соединен с третьим входом информационного регистра 33, выход первого дешифратора 38 подключен к второму входу второго элемента 39 ИЛИ, третий вход которого соединен с выходом третьего переключателя 46, второй выход первого управляемого счетчика 40 соединен q входом шифратора 37, выход третьего управляемого счетчика 7 подключен к нулевому входу первого триггера 2, а управляющий вход соединен с вторым выходом счетного регистра 14 и с нулевым входом второго триггера 11, единичный вход

второго триггера 11 соединен с единичньаи входом первого триггера 2 и с первым входом шестого элементу 36 ИЛИ,.единичный выход второго триггера 11 соединен с первым входом шестого элемента 18 И, второй вход которого подключен к адресному выходу управляе№ го вероятностного (1 fl ) полюсника 20, нулевой выход второго триггера 11 соединен с перBbJM входом четвертого элемента 8 И и с первь входом пятого элемента 12 И, .вход Дешифратора 10 соединен с первьлл выходом четвертого управляемого счетчика 9, второй выход

KOTopofo подключен к первым входам 1етвертого 29 и пятого 35 элементов ИЛИ, выход четвертого элемента 8 И соединен со счетным входом четвертого управляемого счетчика 9, управляквдий вход которого подключей к первому входу управляемого вероятностного (1-и)-полюсника 20, второй вход четвертого элемента 8 И соединен с выходом второго элемента 6 И, вторые входы четвертого 29,

пятого 35 и шестого 36 элементов ИЛИ подключены к второму выходу первого управляемого счетчика 40, выход пятого элемента 35 ИЛИ соединен с {вторым входом третьего элемента 34 И,

вход второго регистра 42 соединен с входом 41 установки числа узлов исследуемой области,, а выход соединен с первым входом седьмого элемента 43 И, выход шестого элемента 36

ИЛИ соединей с- вторым входом седьмого элемента 43 И, выход которого подключен к управляющему входу первого управляемого счетчика 40.

Назначение элементов устройства следующее. На пусковой вход 1 по-а дается сигнал Начало счета, с помощью первого триггера 2 осуществляется пуск и останов устройства; первый переключатель 3 используется при решении задачи для одного узла или для нескольких узлов сеточной области, с выхода 4 окончания счета поступает сигнал Окончания счета, генератор 5 тактовых импульсов- задает временную сетку работы устройства, третий управляемый счетчик 7 осуществляет подсчет числа итераций на второй ступени вычислительной процедуры, четвертый управляемый счетчик 9 обеспечивает подсчет числа тактов обхода соседних узлов и исследуемого узла сеточной области, второй дешифратор 10 формирует сигналы изменения координат узлов области в соответствии с заданным направлением их обхода; второй триггер 11 управляет .режимами первой и второй ступени вычислительной процедуры, на вход 13 установки начального адреса поступает сигнал выборки начального адреса, счетный регистр 14 фиксирует адрес исследуемого узла области, первый регистр 16 состоит из реверсивных счетчиков координат и обеспечивает возможность решения задачи в одно-, двух- и трехмерных областях, на вход 19 размерности исследуемой области подается сигнал установки размерности исследуемой области путем п реключения выходов управляемого вероятностного (1-п)-полюсника 20 и путем изменения коэффициента деления четвертого управляемого счетчика 9, управляемый вероятностный (1-П )-полюсник 20 предназначен для вероятностного преобразования информации и реализации закона случайного блуждания частицы по узлам сеточной области, н.а вход 23 установки степени точности подается сигнал для установки необходимой точности решения fS Ciзаданной надежностью вычисленийjb, на вход 24 задания закона распределения блуждания частицы по узлам сеточной области, в блоке 25 постоянной- памяти хранятся значения вероятностей переходов из исследуемого узла в соседние узлы, блок 27 усреднения предназначен для получения первой оценки решения задачи (среднего арифметического веса по траектория начинающим с узла, для которого находится решение) на первой ступени вычислительной процедуры, второй оценки (среднего арифметического весов соседних узлов) и результат решения среднего арифметического (певой и второй оценок решения задачи) на второй ступени вычислительной процедуры, блок 28 вычисления требуемог числа испытаний осуществляет вычисление дисперсии веса, определение требуемого числа испытаний и числа итерации, значение которого заносится в третий управляемый счетчик 7, на информационный вход 30 поступают сигналы значений законов вероятноетных переходов, начальных и граничных условий, признаков граничных или внутренних узлов, с информационного выхода 31 выдаются результаты решения, информационный

регистр 33 предназначен для организации обмена анализируемой и результирующей информации; шифратор 37 предназначен для выработки кода,11 соответствующего признаку граничног узла и .маркировки этим кодом узлов, для которых найдено решение; первый дешифратор 38 осуществляет дешифрирование содержимого последних двух разрядов информационного регистра 33, фиксирует окончание построения одной траектории, когда последняя попадает на границу; первый управляемый счетчик 40 обеспечивает построение точно п траекторий из данного узла на вход 41 установки числа узлов исследуемой области п второй регистр 42 фиксирует число узлов исследуемой области; второй управляемый счетчик 44 осуществляет подсчет числа шагов траектории блуж Дания; третий переключатель включается при решении параболических уравнений; на вход 45 установки числа шагов подается сигнал для установки числа шагов (путем изменения коэффициента деления второго управляемого счетчика). I

Предлагаемое устройство обеспечивает возможность решения конечно-разностных уравнений эллиптического и параболического типов в двухступенчатом режиме вероятностно-детерминированным методом, позволяющим значительно сократить требуемое число испытаний (траекторий случайного блуждания) и, следовательно, увеличить быстродействие .устройства

Двухступенчатый вероятностно-детерминированный процесс оценки решения состоит в следующем:на первой ступени вычислительнойпроцедуры вероятностным методом находят первую приближенную оценку решения задачи во всех точках сеточной Области, далее на второй ступени вычислительной процедуры повторно применяют для всех точек области итерационный алгоритм, по которому сначала находится вторая оценка решения задачи для исследуемого узла области путем усреднения значений первых оценок решения в соседних узлах, после чего находится среднее арифметическое первой и второй оценок решения для данного узла, являющееся.результатом решения задачи в этом узле.

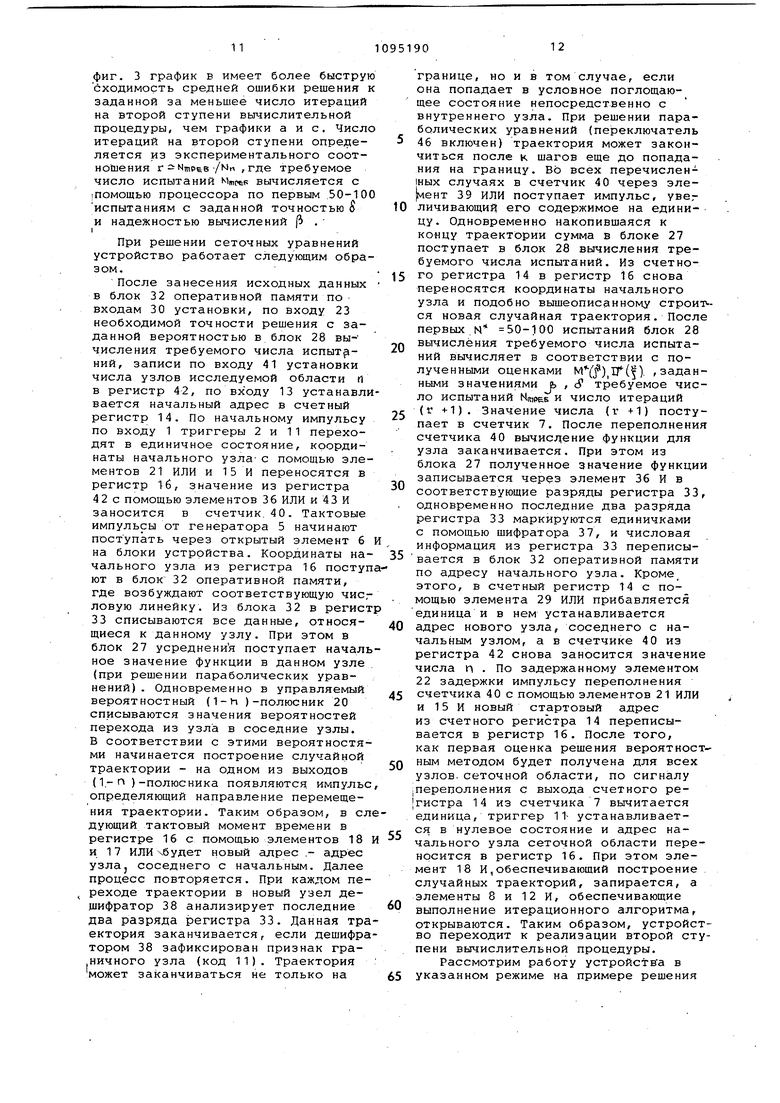

Число испытаний на первой ступени Nr определяется числом узлов исследуемой области п , что обосновывается экспериментально на примере решения задачи Дирихле для уравнения Лапласа с числом узлов прямоугольной сеточной области п 100 и различном числе испытаний (фиг.2, где для графиков а -Мп 50, в -Ы( ,-100, с - NK - 200). Как видно из

фиг. 3 график в имеет более быструю сходимость средней ошибки решения к заданной за меньшее число итераций на второй ступени вычислительной процедуры, чем графики а и с. Число итераций на второй ступени определяется из экспериментального соотношения r-NmP6B-/N , где требуемое число испытаний вычисляется с ;помощью процессора по первым 50-100 испытаниям с заданной точностью В

и надежностью вычислений fi .

I

При решении сеточных уравнений устройство работает следующим образом.

После занесения исходных данных в блок 32 оперативной памяти по входам 30 установки, по входу 23 необходимой точности решения с заданной вероятностью в блок 28 вычисления требуемого числа испытрний, записи по входу 41 установки числа узлов исследуемой области П в регистр 42, по входу 13 устанавливается начальный адрес в счетный регистр 14. По начальному импульсу по входу 1 триггеры 2 и 11 переходят в единичное состояние, координаты начального узла-с помощью элементов 21 ИЛИ и 15 И переносятся в регистр 16, значение из регистра 42с помощью элементов 36 ИЛИ и 43 И заносится в счетчик. 40. Тактовые импульсы от генератора 5 начинают поступать через открытый элемент 6 на блоки устройства. Координаты начального узла из регистра 16 поступют в блок 32 оперативной памяти, где возбуждают соответствующую чис,ловую линейку. Из блока 32 в регист 33 списываются все данные, относящиеся к данному узлу. При этом в блок 27 усреднения поступает начальное значение функции в данном узле (при решении параболических уравнений) . Одновременно в управляемый вероятностный (1-h )-полюсник 20 списываются значения вероятностей перехода из узла в соседние узлы. В соответствии с этими вероятностями начинается построение случайной траектории - на одном из выходов (1-п )-полюсника появляются импульс определяющий направление перемещения траектории. Таким образом, в слдующий тактовый момент времени в регистре 16 с помощью элементов 18 и 17 ИЛИ чбудет новый адрес .- адрес узла, соседнего с начальным. Далее процесс повторяется. При каждом переходе траектории в новый узел дешифратор 38 анализирует последние два разряда регистра 33. Данная траектория заканчивается, если дешифратором 38 зафиксирован признак граничного узла (код 11). Траектория может заканчиваться не только на

границе, но и в том случае, если она попадает в условное поглощающее состояние непосредственно с внутреннего узла. При решении параболических уравнений (переключатель 46 включен) траектория может закончиться после к шагов еще до попадания на границу. Во всех перечисленных случаях в счетчик 40 через эле{мент 39 ИЛИ поступает импульс, уве,личивающий его содержимое на единицу. Одновременно накопившаяся к концу траектории сумма в блоке 27 поступает в блок 28 вычисления требуемого числа испытаний. Из счетного регистра 14 в регистр 16 снова переносятся координаты начального узла и подобно вышеописанному строится новая случайная траектория. После первых м 50-100 испытаний блок 28 вычисления требуемого числа испытаний вычисляет в соответствии с полученными оценками М {|),(|). (Заданными значениями ь , с требуемое число испытаний МИРЕБ и число итераций (г +1). Значение числа (г +1) поступает в счетчик 7. После переполнения счетчика 40 вычисление функции для узла заканчивается. При этом из блока 27 полученное значение функции записывается через элемент 36 И в соответствующие разряды регистра 33, одновременно последние два разряда регистра 33 маркируются единичками с помощью шифратора 37, и числовая информация из регистра 33 переписывается в блок 32 оперативной памяти по адресу начального узла. Кроме этого, в счетный регистр 14 с помощью элемента 29 ИЛИ прибавляется единица и в нем устанавливается адрес нового узла, соседнего с начальным узлом, а в счетчике 40 из регистра 42 снова заносится значение числа п . По задержанному элементом 22 задержки импульсу переполнения счетчика 40 с помощью элементов 21 ИЛИ и 15 И новый стартовый адрес из счетного регистра 14 переписывается в регистр 16. После того, как первая оценка решения вероятностным методом будет получена для всех узлов, сеточной области, по сигналу ;переполнения с выхода счетного ре|гистра 14 из счетчика 7 вычитается единица, триггер 11- устанавливается в нулевое состояние и адрес начального узла сеточной области переносится в регистр 16. При этом элемент 18 И(Обеспечивающий построение случайных траекторий, запирается, а элементы 8 и 12 И, обеспечивающие выполнение итерационного алгоритма, открываются. Таким образом, устройство переходит к реализации второй ступени вычислительной процедуры.

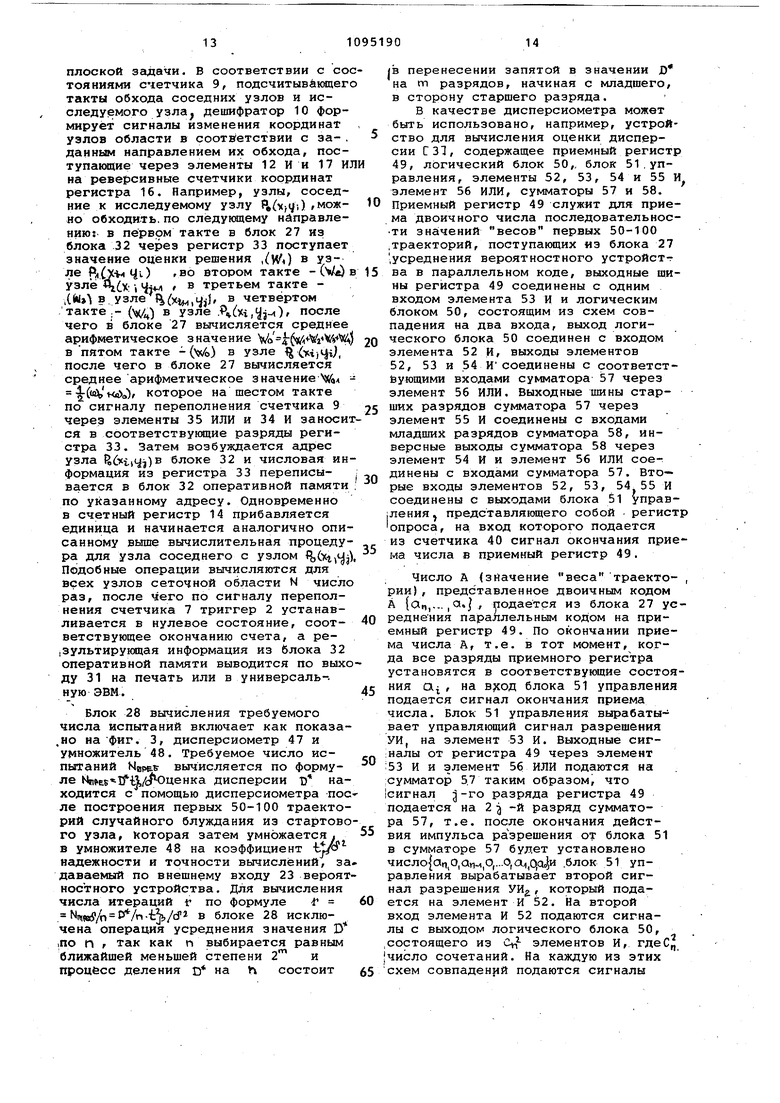

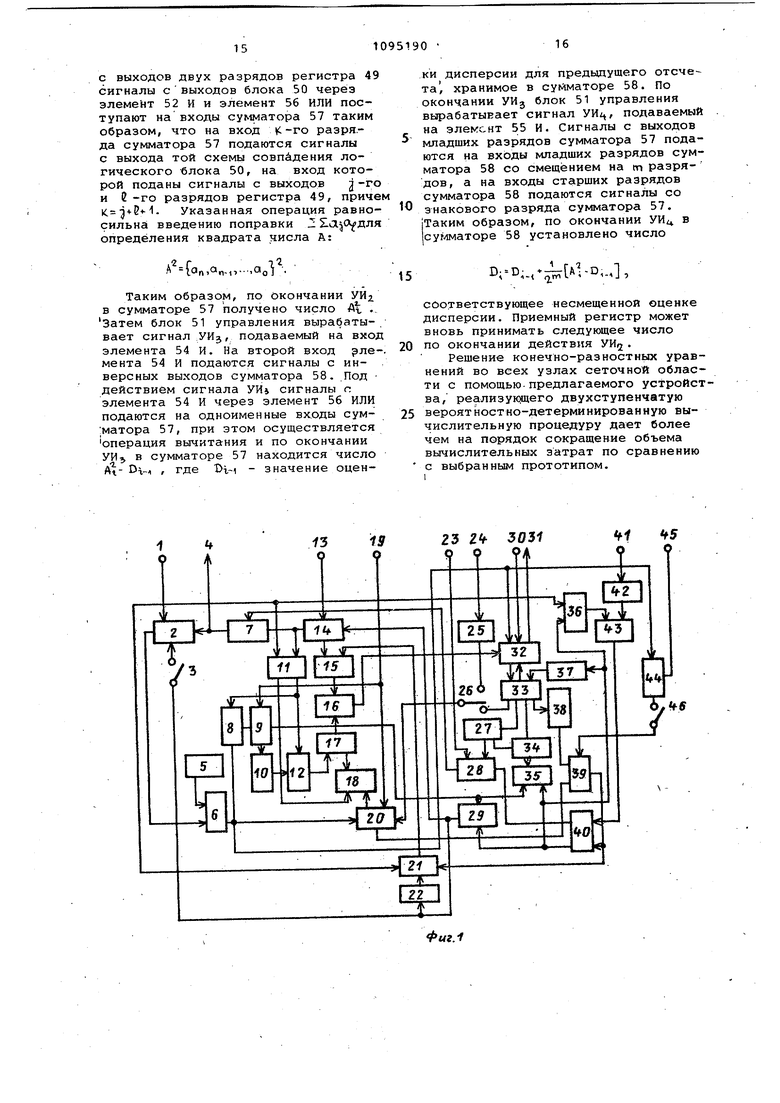

Рассмотрим работу устройстнга в указанном режиме на примере решения плоской задачи. В соответствии с со тояниями счетчика 9, подсчитывающег такты обхода соседних узлов и исследу емого узла, дешифратор 10 формирует сигналы изменения координат узлов области в соответствии с за- . данным направлением их обхода, поступакицие через элементы 12 И и 17 И на реверсивные счетчики координат регистра 16. Например, узлы, соседние к исследуемому узлу ,) ,можно обходить, по слёдунлцему направлению: в первом такте в блок 27 из блока 32 через регистр 33 поступает значение оценки решения ,( в узле P(() г во втором такте - (We) узле , (j , в третьем такте ,(М в. (;xi„,yjj, в четвёртом такте,- (х/) в узле .,yj-vi), после чего в блоке 27 вычисляется среднее арифметическое значение впятом такте -(w) в узле 1 (уч)4, после чего в блоке 27 вычисляется среднее арифметическое значение Чйд ( которое на шестом такте по сигналу переполнения счетчика 9 через элементы 35 ИЛИ и 34 И заноси ся в соответствующие разряды регистра 33. Затем возбуждается адрес узла )в блоке 32 и числовая ин формация из регистра 33 переписывается в блок 32 оперативной памяти по указанному адресу. Одновременно в счетный регистр 14 прибавляется единица и начинается аналогично описанному выше вычислительная процедура для узла соседнего с узлом Яз(хг, Подобные операции вычисляются для всех узлов сеточной области N число раз, после чего по сигналу переполнения счетчика 7 триггер 2 устанавливается в нулевое состояние, соответствующее окончанию счета, а ре|3ультирукяцая информация из блока 32 оперативной памяти выводится по выхо ду 31 на печать или в универсаль-. ную ЭВМ. Блок 28 вычисления требуемого числа испытаний включает как показа.но на фиг. 3, дисперсиометр 47 и умножитель 48. Требуемое число испытаний NBPE.K вычисляется по формуле Мп(,/с Оценка дисперсии 13 находится с помощью дисперсиометра пос ле построения первых 50-100 траекторий случайного блуждания из стартово го узла, которая затем умножается i и уола, nuivji a эахсп умнижаеп и . В умножителе 48 на коэффициент tt/ надежности и точности вычислений, за даваемый по внешнему входу 23 вероят ностного устройства. Для вычисления числа итераций г по формуле f . Nni(eJ/o P /n--t /cr в блоке 28 исключена операция усреднения значения D ,по п , так как п выбирается равным ближайшей меньшей степени 2 и процесс деления D на П состоит jB перенесении запятой в значении J3 на m разрядов, начиная с младшего, в сторону старшего разряда. В качестве дисперсиометра может быть использовано, например, устройство для вычисления оценки дисперсии С 31, содержащее приемный регистр 49, логический блок 50„ блок 51.управления, элементы 52, 53, 54 и 55 И элемент 56 ИЛИ, сумматоры 57 и 58. Приемный регистр 49 служит для приема двоичного числа последовательности значений весов первых 50-100 .траекторий, поступающих из блока 27 усреднения вероятностного устройств ва в параллельном коде, выходные шины регистра 49 соединены с одним входом элемента 53 И и логическим блоком 50, состоящим из схем совпадения на два входа, выход логического блока 50 соединен с входом элемента 52 И, выходы элементов 52, 53 и 54 Исоединены с соответствующими входами сумматора 57 через элемент 56 ИЛИ. Выходные шины старших разрядов сумматора 57 через элемент 55 И соединены с входами младших разрядов сумматора 58, инверсные выходы сумматора 58 через элемент 54 И и элемент 56 ИЛИ сое-: динены с входами сумматора 57. Вторые входы элементов 52, 53, И соединены с выходами блока 51 управ;ления представляющего собой регистр опроса, на вход которого подается из счетчика 40 сигнал окончания приема числа в приемный регистр 49. Число А (значение веса траекто- , рии), представленное двоичным кодом А {citi, подается из блока 27 усреднения параллельным кодом на приемный регистр 49. По окончании приема числа А, т.е. в тот момент, когда все разряды приемного регистра установятся в соответствукяцие состояния а , на блока 51 управления подается сигнал окончания приема числа. Блок 51 управления вырабатывает управляющий сигнал разрешения УИ, на элемент 53 И. Выходные сиг:налы от регистра 49 через элемент 53 И и элемент 56 ИЛИ подаются на :сумматор 5.7 таким образом, что 1сигнал 3-го разряда регистра 49 подается на 2 -и разряд сумматора 57, т.е. после окончания действия импульса разрешения от блока 51 в сумматоре 57 будет установлено число{ап о,ап-1,О,...о,а1,ао5и .блок 51 управления вырабатывает второй сигнал разрешения УИ, который подается на элемент И 52. На второй вход элемента И 52 подаются сигналы с выходом логического блока 50, состоящего из С элементов И, гдеС число сочетаний. На каждую из этих схем совпадений подаются сигналы

с выходов двух разрядов регистра 49 сигналы свыходов блока 50 через элемент 52 И и элемент 56 ИЛИ поступают на входы сумматора 57 таким образом, что на вход (С-го разря.да сумматора 57 подаются сигналы с выхода той Схемы совпадения логического блока 50, на вход которой поданы сигналы с выходов i-го и 8-го разрядов регистра 49, причем K.s + Pi-l. Указанная операция равносильна введению поправки JI а оудля определения квадрата числа А:

Л ап,а„.„...,ао

Таким образом, по Окончании УЙ2. в сумматоре 57 получено число А ., Затем блок 51 управления вырабатывает сигнал УИз, подаваемый на вход элемента 54 и. На второй вход рлемента 54 И подаются сигналы с инверсных выходов сумматора 58. Под действием сигнала УИ сигналы с элемента 54 И через элемент 56 ИЛИ подаются на одноименные входы сум.матора 57, при этом осуществляется операция вычитания и по окончании УИ в сумматоре 57 находится число АЛ- D, , где - значение оценки дисперсии для предьщущего отсчета, хранимое в сумматоре 58. По окончании УИд блок 51 управления вырабатывает сигнал УИ, подаваемый на элемент 5;5 И. Сигналы с выходов младших разрядов сумматора 57 подаются на входы младших разрядов сумматора 58 со смещением на tn разрядов, а на входы старших разрядов сумматора 58 подаются сигналы со 3 накового разряда сумматора 57. Таким образом, по окончании УИ в суг маторе 58 установлено число

D-D;.,,.,,

15

соответствующее несмещенной оценке дисперсии. Приемный регистр может вновь принимать следующее число

по окончании действия УИ.

Решение конечно-разностных уравнений во всех узлах сеточной области с помощью.предлагаемого устройства, реализукдаего двухступенчатую

вероятностно-детерминированную вычислительную процедуру дает более чем на порядок сокращение объема вычислительных затрат по сравнению с выбранным прототипом.

V(7

25

tS/

OtfO

О tT

27 {On,-.00} ФцгМ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО для РЕШЕНИЯ ЗАДАЧ МАТЕМАТИЧЕСКОЙ ФИЗИКИ | 0 |

|

SU328475A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| ВСЕСОЮЗНАЯ I n?Tcq7^n.Tr^:^tUif:r'g^:^' lif.«b>&ll»i-J {>&.,.-'.<si! iJ.»!!.'- ,-^ | 0 |

|

SU362304A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| , | |||

Авторы

Даты

1984-05-30—Публикация

1981-07-16—Подача