1

Tofi элемент И, выход которого соединен с входом первого генератора псев дослучайгых чисел, блок усреднения, первый вход которого соединен с единичным выходом второго триггера, второй вход соединен с нулевым выходом второго триггера, третий и четвертый входы соединены с выходами соответственно, второго и третьего регистров группы, а первый выход соединен с первым входом третьего элемента И, седьмой элемент Н, первый вход которого соединен с вторым выходом блока усреднения, второй вход подключен к нулевому выходу второго триггера, а выход соединен с входом третьего регистра группы, первый управляемый счетчик, первый управляющий вход которого является входом задания требуемого числа испытаний устройства, а выход соединен с входом первого переключателя и вторым входом счетного регистра, третий триггер, нулевой вход которого подключен к выходу первого управляемого счетчика, восьмой элемент Н, выход которого соединен с единичным входом третьего триггера и третьим входо блока оперативной памяти, третий переключатель, второй управляемый счетчик, выход которого соединен с входом третьего переключателя, девятый элемент И, первый вход которого соединен с выходом четвертого регистра группы, а второй вход подключен к.нулевому выходу второго триггера, jiecnTbm элемент И, первый вход которого подключен к выходу второго элемента ШШ, а второй вход подключен к пулевому выходу второго триггера, одиннадцатый элемент И, первый которого соединен с нулевым выходом третьего триггера, второй вход соединен с выходом девятого элемента И, а выход соединен с вторым управляющим входом первого управляемого счетчика третий управляемый счетчик

-первый управляющий вход которого подI

ключен к входу задания требуемого

Числа испытаний устройства, второй управляющий вход подключен к выходу девятого элемента Н, первый выход соединен с входом цетверто.го регистра группы, а второй выход соединен с вторым входом третьего элемента И, шифратор, вход которого подключен к второму выходу третьего управляемого счетчика, а выход соединен с вхо домгпятого регистра группы, дешифратор вход которого соединен с выходом пятого регистра группы, а выход соединен с вторым входом второго элемента ШШ, выход формирователя импульсов чтения соединен с четвертым входом блока оперативной памяти, о тл и ч а ю щ е е с я тем, что, с целью повышения быстродействия, оно дополнительно содержит второй генератор псевдослучайных чисел, третий регистр, четвертый триггер, двенадцатый, тринадцатый, четырнадцатый,. пятнадцатый, шестнадцатый, семнадцатый и восемнадцатый элементы И, пятый и шестой элементы J-ШИ, элемент НЕ, Причем вход второго регистра является входом установки числа шагов устройства, а выход соединен с первым входом пятого -элемента И„ выход которого соединен с управляюпщм входом второго управляемого счетчика, первый вход двенадцатого элемента И, вторые входы пятого элемента И и третьего элемента ИЛИ и вход элемента НЕ подключены к выходу второго элемента ШП1, Выход третьего переключателя соединен с вторым выходом четвертого элемента ИЛИ и- единичным входом четвертого триггера, нулевой вход которого соединен с выходом третьего элемента ИЛИ, а выход соединен с первым входом четвертого элемента И, выход четвертого элемента. И сое- динен с третьим входом четвертого элемента ilBi, ныход которого соединен с нулевым входом второго триггера, единичный выход второго триггера соединен с первыми входами шестого, тринадцатого и пятнадцатого элементов И, а нулевой выход соединен с первыми входами восьмого, четырнадцатого и шестнадцатого элементов И и вторым входом двенадцатого элемента И, выход формирователя импульсов записи i соединен с вторьи-ш входами четвертого, шестого и - восьмого элементов

И, выход элемента НЕ соединен с третьими входами шестого и восьмого элементов И, выход шестого элемента И соединен с счетным входом второго управляемого счетчика и первым входом семнадцатого элемента И, второй вход которого соединен с выХОДОМ первого генератора псевдослучайных чисел, а выход соединен с первым входом шестого элемента lUHi, выход второго генератора псевдослучайных чисел соединен с первым входом восемнадцатого элемента И, второй вход которого подключен

к выходу восьмого элемента И, а выход соединен с вторым входом шестого элемента ИЛИ, выход шестого элемента ИЛИ соединен с третьим входом управляемого вероя- ностного (1-п)-полюсника, второй выход управляемого вероятностного (1-п)-полюсника соединен с вторыми входами тринадцатого и четырнадцатого элементов И, выход второго элемента И соединен с первым входом третьего регистра, выходы тринадцатого и четырнадцатого элемен- , тов И соединены с вторьии входами соответственно nepBofo и третьего

539

, 10

регистров, выходы которых соединены с вторыми входами соответственно пятнадцатого и шестнгщцатого элементов И, выходы пятнадцатого и шестнадцатого элементов И соединены соответственно с первым и вторым входами пятого элемента ИЛИ, выход которого соединен с пятым входом блока оперативной памяти, выход двенадцатого элемента И соединен с входом элемента задержки, выход десятого I элемента И соединен со счетным входом первого управляемого счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вероятностное устройство для решения конечно-разностных уравнений | 1980 |

|

SU888119A1 |

| Вероятностное устройство для решения конечно-разностных уравнений | 1981 |

|

SU1095190A1 |

| Вероятностное устройство для решения уравнения Лапласа | 1981 |

|

SU1057956A1 |

| Вероятностное устройство для решения конечно-разностных уравнений | 1981 |

|

SU1160434A1 |

| Вероятностное устройство для решения уравнения Лапласа | 1983 |

|

SU1091172A1 |

| Вероятностное устройство для решения конечно-разностных уравнений | 1981 |

|

SU1149278A1 |

| Устройство для обхода сеточной области | 1982 |

|

SU1084806A1 |

| Устройство для моделирования случайных процессов | 1984 |

|

SU1223227A1 |

| Вероятностное устройство для решения конечно-разностных уравнений | 1972 |

|

SU477418A1 |

| Устройство для определения вероятностных характеристик фазы случайного сигнала | 1982 |

|

SU1112377A1 |

ВЕРОЯТНОСТНОЕ УСТРОЙСТВО ЛШ1 РКИЕНИЯ KOHE fflO-РАЗНОСТНЫХ УРАВНЕНИЙ, содержащее первый триггер, единичный вход которого является пусковым входом устройства, первый элемент И, первый вход которого соединен с единичным выходом первого триггера, генератор тактовых импульicoB, выход которого соединен с вторым входом первого элемента И, первый элемент 1ШИ, первый вход которого подключен к пусковому входу устройства, элемент задержки, выход которого соединен с вторым входом первого элемента 11ПН, счетный регистр, первый вход которого является входом установки начального адреса устройства, а первый выход соединен с нулевым входом первого триггера и является выходом окончания счета устройст ва, второй элемент И, первый вход которого соединен с вторым выходом счетного регистра, а второй вход соединен с выходом первого элемента ШШ, первый регистр, первый вход которого соединен с выходом второго элемента И, второй регистр, управляемый вероятностный

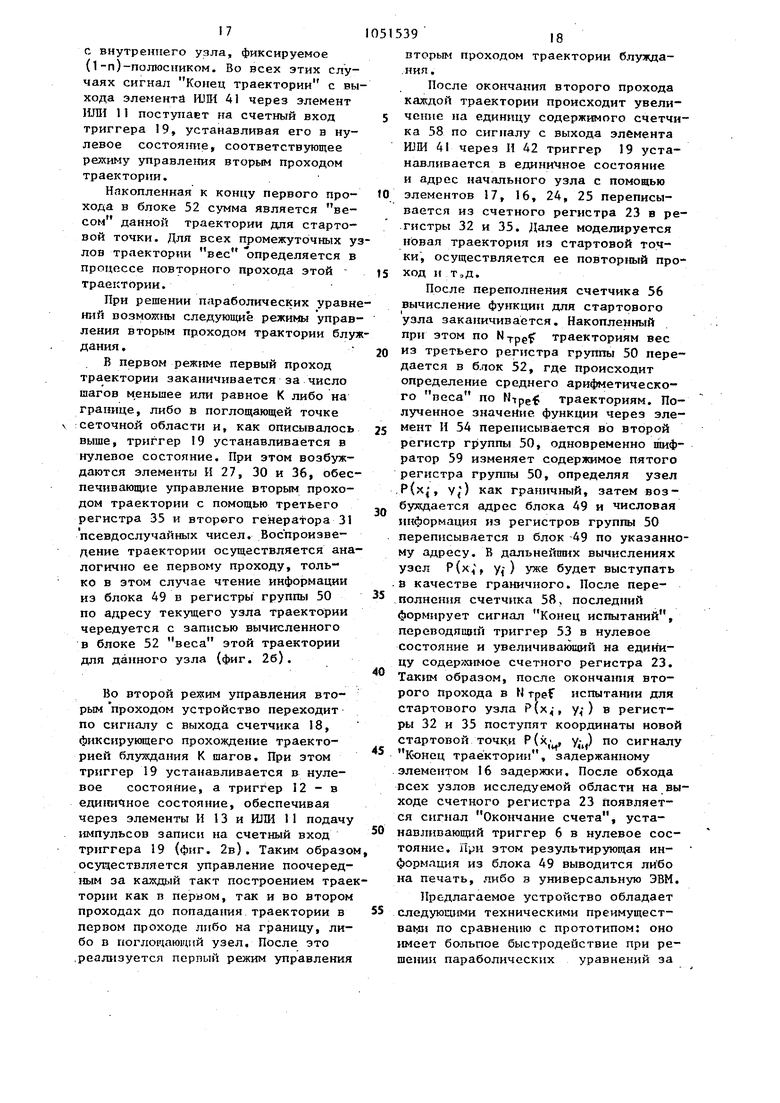

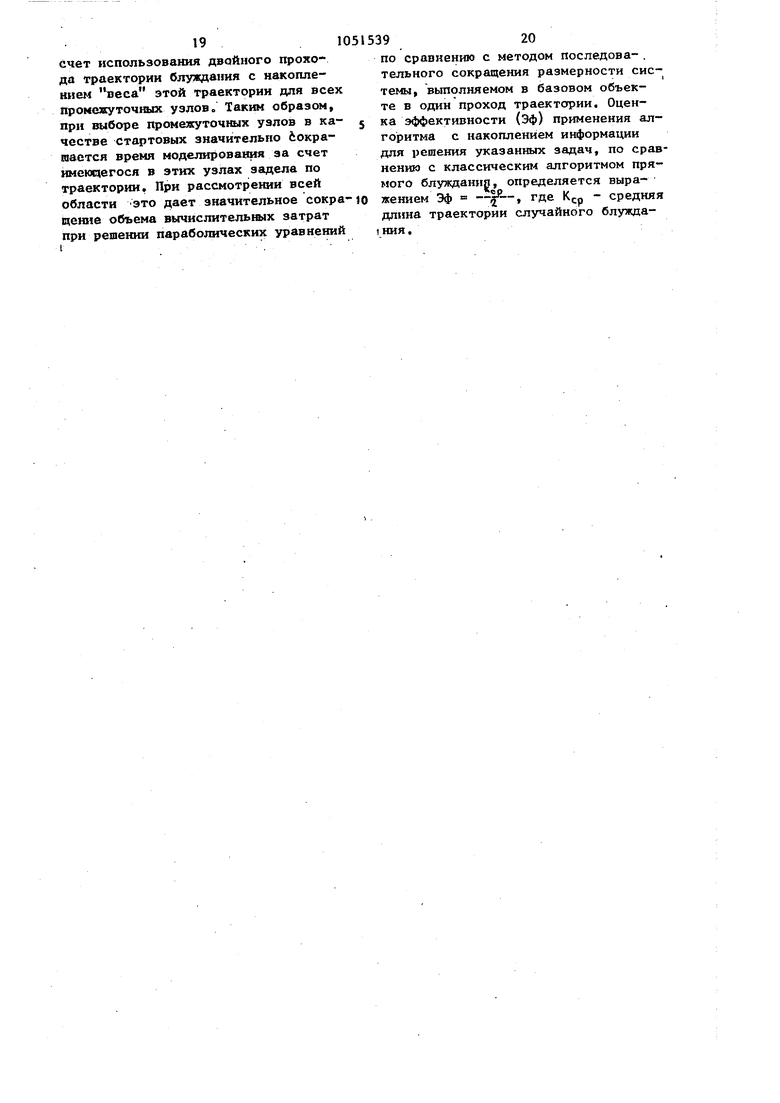

Изобретение относится к вычислительной технике и йожет быть использовано для решения дифференциальных уравнений в частных пронзводшйх, аппроксимированных конечно-разностнымй уравнениями. Известно вероятностное устройство для решения конечно-разностных уравнений, которое содержит линии за- . держки, логические схемы, блок опера тивной памяти, соединенный с регистром информации, подключенным выходами значений функции к входу накапливающего сумматора, блок вероятностного блуждания, выхода которого соединены с выходами регистра блуждания, счетчик числа испытаний, блок анализа, выходы которого соединены с выходами признака регистра информации, счетик поиска и хранения внут ренних узлов сеточной области DJ Недостатком этого устройства является невысокое быстродействие. Наиболее близким к предлагаемому по технической сущности является вероятностное устройство для решения конечно-разностных уравнений, содержащее блок оперативной памяти, первый вход которого является Hi«J opMaционным входом, а первый выход - информационным выходом устройства, регистр информации, вход и выход общей информации которого соединены соответственно с вторыми входом и выходом блока оперативной памяти, блок постоянной памяти, вход которо- го является входом задания закона распределения устройства, процессор, первы) вход которого является входом установки степени точности устройства, первый триггер, единичный вход которого является пускЪвым входом устройства, генератор тактовых импульсов, первый элемент И, первый вход которого соединен с единичным выходом первого триггера, а второй вход - с вьгходом генератора тактовых импульсов, счетный регистр, первый вход которого является входом , началь}1ого адреса, а первый выход является выходом окончания счета устройства и соединен с нулевым входом . первого триггера, первый переключатель, выход которого соединен с входом сброса первого триггера, а вход с вторым входом счетного регистра, -- второй элемент И, первый вход кото;рого соединен с вторым выходом счетного регистрау первый элемент ИЛИ, выход которого соединен с вторым входом второго элемента И, а первый вход - с единичным входом первого триггера, первый элемент задержки, выход которого соединен с вторым входом первого элемента iUDI, первый регистр, первый вход которого соединен с выходом второго элемента И, а выход - с третьим входом блока оперативной памяти, управляемый вероятностный (1-п)-полюсник, первый вход задания размерности которого является входом размерности исследуемой области устройства, а адресный выход соединен с вторым входом нервого регистра, второй переключатель, пер вый вход которого соединен с выходом инф9рмацин вероятностей перехода регистра информации, :а выход - с вхо .дом задания закона распределетшя управляемого вероятностного (1-п)полюсника, третий элемент И, выход которого соединен с входом информации начальгшх ц граничных условий регистра информации, блок усреднения,, выход текущей суммы которого соединен с первым входом третьего элемен, та Н, первый информационный вход с выходом инфo pмauии начальных и граничных условий, общий информационньп выход - с вторым входом про. цёссора, первый управляемый счетчик, первый выход которого соединен с тре тьим входом Процессора-, а первый управляющий вход - с выходом процессора, второй упра.вляемый счетчик, управляющий вход которого .является вхо дом установки числа шагов устройства, третий переключатель, вход которого соединен с выходом второго управляемого счетчика, шифратор, выход .которого соединен с входом информаци положения узла регистра информации, дешифратор, вход которого соединен с выходом информации положения узла регистра информации, второй элемент НШ, первый вход которого .соединен 1 с шпсодом дешифратора,.-второй вход с сигнальным вьпсод управляемого вероятностного )-полюсника9а третий вход - с выходом третьего переключателя, генератор псевдослучайных чисел, второй регистр, формирователь импульсов чтения, формирователь импульсов записи, третий управля счетчик, второй и третий триг . геры, четвертый и пятый переключатели, четвертый, пятый, шестой, седьмой восьмой, девять1й, деся.тый и одиннадцатый элементы И, третий и четвертый элементы ИЛИ и второй элемент задержки, причем единичный вход второго триггера подключен к пусковому входу устройства и соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента И, а вы™ ход - с первым входом пятого элемен™ , выход пятого элемент Н соединен с входом второго регистра8 выход которого соединен с первым входом шестого элемента И, выход шестого элемента И, соединен с перры входом генератора псевдослучайных чисел. первый- выход которого соединен с вероятностным входом управляемого веposTTHocTHpro (1-п)-полюсиика, а второй выход - с вторым входом пятого . элемента И, единичный выход второго триггера соединен с первым входом ieTBepToro элемента .И и с первым уп-; равляющим входом блока усреднения, выход накопленной суммы которого соединен с первым входом седьмого элемента И, нулевой выходвторого триггера соединен с вторым управляюрдим входом блока усреднения, с вторыми входами шестого и седьмого элементов И и с пер-выми входами восьмого, девятого и десятого элементов И, . выход первого элемента И соединен с входами формирователя импульсов записи и формирователя импульсов чтения, выход формирователя импульсов записей соединен с вторым входом генер.атора псевдос,пучайных чисел и вторым входом восьмого элемента И выход которого соединен с четвер.тым входом блока .оператив ной памяти и- единичным входом третьего триггера, нулевой выход третьего триггерасоединен с . первым входом одиннадцатого элемента И, выход которого соединен с вторым управляющим входом первого управлаемого счетчика, второй выход первого управляемого счетчика соединен с нулевым входом третьего триггера . и вторь:м входом счетного регистра, выход формирователя импульс -9 чте--НИН соединен с пятым входом блока оперативной памяти с счетньм входом второго управляемого счетчика, выход второго элемента IfflH соединен с вторым, входом десятогоЭлемента И с входом первого элемента задержки и с входами четвертого и пятого переключателей j выход четвертого переключателя соединен с нулевым входом второго триггера и- с входом второго элемента задержки-, выход которого. соединен с вторым входом четвертого элемента -И и с третьим входом шестого элемента И, .выход пятого переключателя соединен с первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом десятого элемента И, а выход - с счетшлм входом первого управляемого счетчика, выход информации количества траекторий регистра информации соединен с вторым входом девятого элемента И, вызсо которого соединен с вторым входом одиннадцатого элемента И и первым управляющим входом третьего уп-равляемого счетчика, второйуправляю щий вход третьего управляемого счетчика соединен с выходом процессора, первый выход -J с входом информации количества траекторий регистра информации, а в торой, выход - с входом шифратора и вторым входом третьего элемента И, выход йнформадии накопленной суммы весов регистра информащш соединен с вторым информационным входом усреднения, а вход инфор-Гмации накопленной суммы весов ре гистра информации - с выходом седьмого элемента И 2J . В этом устройстве для решения ука занных задач моделируются случайные блуждания для попадания на границу исследуемой области. При этом при ре шёнии параболических уравнений за Один просчет получается приближенное решение только для одиой точки, что существенно увеличивает объем вычислений для получения приближенного решения параболического уравнеНИН ао всех точках сеточной области и снижает быстродействие устройства. , .::.., Цель изобретения - повьипение быст родействий, Поставленная цель достигается тем что вероятностное устройство для ре шения конечно-разностных уравнений, содеражщее первый триггер, единичный вход которого является пусковым входом устройства, первый элемент И, первый вход которого соединен с едишгчным выходом первого триггера, генератор тактовых импульсов, выход которого соеданен с втврым первого элемента И, первый элемент ШБ1, первый вход которого .подклФ чен к пусковому входу устройства, элемент задержки, выход которого соединен с вторьш входом первого элемента ШИ, счетный регистр, первый вход которого является входом -установки начального адреса устройства, а первый выход соединен с нулевым входом первого триггера и является выходом окончания счета, устройства, второй элемент И, первый вход :которого сое динен с вторым выход ш счетного регистра, а второй вход соединён с выходом первого элемента ИШ, первый регистр, первый вход которого соединен с выходом второго элемента И, второй регистр, управляемый вероят1 ностный (1 -п)-полюсник, первый вход 9 которого является входом размерности исследуемой области устройства, второй элемент ИЛИ, первый вход которого соединен с первым выходом управляемого вероятностного (1-п)-полюсника, третий элемент ИЛИ, первый вход которого подключен к пусковому входу устройства, четвертый элемент , первый вход которого соединен I с выходом второго элемента ИЛИ, вто1рой триггер, единичный вход которого подключен к пусковому входу ,устройства, формирователь импульсов записи и формирователь импульсов чте- Ния, входы которых соединены с выходом nepBot-o. элемента И, первый переключатель, выход которого соединен с входом сброса первого триггера,- . блок постопиной памяти вход которого является входом задания закона распределения, устройства, второй переключатель первый вход которого соединен с выходом блока постоянно й - памяти, а выход соединен с вторым входом управляемого вероятностного (1-п)-полюсника, блок оперативной памяти, первые вход и выход которого являются соответственно информационным входом и информационнь1М выходом устройства, группу регистров, вход и выход которых соединены с вторыми соответственно выходом и входом блока оперативной памяти, а выход первого регистра гругаш соединен с вторым входом второго переключателя, третий элемент И, В1ыход которого соединен с входом второго регистра групгш, четвертый и .пятый элементы И, первый генератор Псевдослучайных чисел, шестой элемент И, выход которого соедитнен с входсм первого генератора псевдослучайшлх чисел, блок ycpeднeниЯjL . первый вход которого соединен с единичным выходам второго триггера, -второй вход соединен -с нулевым выходом второго триггера, третий и четвертый входы соединены с выходами соответственно второго и третьего регистров грушш, а первый выход соединен с первым вкодом третьего элемента И, седьмой элемент И, первый вход кото рого соединен с вторым выходом блока усреднения, второй, вход подключен к нулевому выходу второго триггера, а выход соединен с входом третьего регистра группы, первый управляе1« |й счетчик, первый управляющий вход которого является входом задания требуемого числа испытаний устройств а. а выход соединен с входом первого переключателя и вторым входом счетного регистра, третий триггер, нуле вой «ход которого подключен к выходу первого управляемого счетчика, восьмой элемейт И, выход KoT pibro соединен с единичным входом третьего триггера и третьим входом блока оперативной памяти, третий переключатель, второй управляемый счетчик, выход которого соединен с входом третьего переключателя, девятый элемент И, первый вход которого соединен с выходом четвертого регистра группы, а второй, вход подключен к ну- 15 дом

левому выходу второго триггера, десятый элемент И, первый вход которого подключен к выходу второго элемента Ш1И, а второй вход подключен к нулевому выходу второго триггера, одиннадцатый элемент И, первый вход которого соединен с нулевым выхо-дом третьего триггера, второй вход соединен с выходом девятого элемента И, а выход соединен с вторым управляющим входом первого управляемого счетчика, третий управляемый счетчик первый управляющий вход которого подключен к входу задания требуемого числа испытаний устройства, второй упр.авляющий вход подключен к выходу

I - .TI

девятого элемента.И, первый выход соединен с входом четвертого регист.ра группы, а второй выход соединен с вторым входом третьего элемента И, гаифратор, вход которого подключен к второму выходу третьего управляемого счетчика, а выход соединен с входом пятого регистра Труппы, дешифратор, вход которого соединен с выходом пятого регистра группы, а выход соединен с вторым входом второго элемента ИЛИ, выход формирователя импульсов чтения соединен с

четвертым входом блока оперативной памяти, дополнительно содержит второй генератор псевдослучайных чисел, третий регистр, четвертый триггер, двенадцатый, тринадцатый,, четырнад. цатый, пятнадцатый, шестнадцатый, семнадцатый и восемнадцатый элементы И, пятый и шестой элементы ИЛИ, элемент НЕ, причем вход второго регистра является входом установки числа шагов устройства, а выход соединен с первым входом пятого элемента И, выход которого соединен с управляющим входом второго управляемого счетчика, первый вход двеиадцатоход второго триггера соединен с первыми входами шестого, тринадцатого и пятнадцатого элементов И, а нулевой выход соединен с первыми входами восьмого, четырнадцатого и шестнадцатого элементов И и вторым входом двенадцатого элемента И, выход формирователя импульсов записи соединен с вторыми входами четвертого, шестого и восьмого элементов И, выход элемента НЕ соединен с третьими входами шестого и восьмого элементов И, выход шестого элемента И соединен с счетным входом второго управляемого счетчика и первым входом семнадцатого элемента И, второй вход которого со€;динен с выходом первого генератора псевдослучайньтх чисел, а выход соединен с первым входом шестого элемента ИЛИ, выход второго генератора псевдослучайных чисел соединен с первым входом восемнадцатого элемента И, второй- вход которого подключен к выходу восьмого элемента И, а выход соединен с вторым входом шестого элемента ИЛИ, выход шестого элемента ИЛИ соединен с третьим входом управляемого вероятностного {1-п)-полюсника, второй выход управляемого вероятностного (1-п)-полюсника соединен с вторыми входами тринадцатого и четырнадцатого элементов I. И, выход второго элемента И соединен с первым входом третьего регистра, выходы тринадцатого и четырнадцатого элементов И соединены с вторыми входами соответственно первого и третьего регистров, выходы которых соединены с вторыми входами соответственно пятнадцатого и шестнадцатого элементов И, выходы пятнадцатого и шестнадцатого элементов И соединень соответственно с первым и вторым входами пятого элемента ИЛИ, выход кото9«го элемента И, вторые входы пятого элемента Н и третьего элемента ШШ и вход элемента НЕ подключа к выходу второго элемента ИЛИ, выход третьего переключателя соединен с вторым входом четвертого элемента ИЛИ и единичным входом четвертого триггера, нулевой вход которого соединен с выходом третьего элемента ИЛИ, а выход соединен с первым входом четвертого элемента И, ьыход четвертого элемента И соединен с третьим . входом четвертого элемента 1ШИ, вы5СОД которого соединен с нулевым вховторого триггера, единичный вы) рого соединен с пятым входом блока оперативной памяти, выход двенадь ат гр элемента И соединен с входом элемента задержки, выход десятого элемента И соедиг рн с счетным входом первого управляемого счетчика. На фиг. 1 - приведена блок-схема устройства; на фиг. 2 - временные диаграммь работы устройства. Устройство имеет пусковой вход 1 вход 2 установки числа шагов, второй регистр 3, третий элемент ИПИ 4, выход 5 окончания счета, первый триггер 6, генератор 7 тактовых импульсов, первый элемент И 8, пятый элемент И 9, третий переключатель 10 четвертый элемент ШШ 11, четвертый триггер 12, четвертый элемент И 13, первыр переключатель 14, формирователь 5 импульсов чтения, элемент задержки 16, двенадцатый элемент И 17, второй управляемый счетчик 18, второй триггер 19, формирователь 20 импульсов записи, элемент НЕ 21, вход 22 установки начального адреса счетный регистр 23, первый элемент ШМ 24, второй элемент И 25, тринадцатьн1 элемент И 26, четырнадцатый элемент И 27, шестой элемент И 28, :Первый геиератор 29 Псевдослучайных чисел, восьмой элемент И 30, второй генератор 31 псевдослучайных чисел, первый регистр 32, пятнадцатый элемент Н 33, пятый элемент ИЛИ 34, тре тий регистр 35, шестнадцатый элемент И 36, семнадцатый элемент И 37 шестой элемент ИЛИ 38, управляемый вероятностный (1-п)-пол осник 39, восемнадцатый элемент И 40, второй эле мент ИЛИ 41, десятый элемент И 42, вход 43 размерности исследуемой области, вход 44 задания закона распре деления, блок 45 постоянной памяти, второй переключатель 46, информацион ный вход 47, информационный выход 48, блок 49 оперативной памяти, группа 50 регистров информации третий элемент И 51, блок 52 усреднения третий триггер 53, седьмой элемент И 54, девятый элемент И 55, третий управляемый счетчик 56, одиннадцатый элемент И 57, первый управляемый счетчик 58, шифратор 59, дешифратор 60, вход 61 задания требуемого числа испытаний. Единичные входы первого 6 и второ го 19 триггеров соединены с пуске-, вым входом 1 устройства и с первыми входами первого 24 и третьего 4 эле3910ментов ШШ, нулевой вход первого триггера 6 соединен с выходом 5 окончания счета устройства и с первым выходом счетного регистра 23, единичный выход первого триггера подключен к первому входу первого элемента И 6, второй вход которого соединен с выходом генератора 7 тактовых импульсов, выход первого элемента И 8 соединен с входами формирователя 15 импульсов чтения и формирователя 20 импульсов записи, первый вход счетного регистра 23 является, входом 22 начального адреса устройст ва, а второй вход соединен с входом первого переключателя 14, с нулевым входом третьего триггера 53 и выходом первого управляемого счетчика 58, первый вход управляемого вероятностного (1-п1-полю сника 39 является входом 43 размерности исследуемой области устройства, а второй вход соединен с выходом второго переключателя 46, вход блока 45 постоянной памяти является входом 44 задания закона распределения устройства, а выход соединен с первым входом второго переключателя 46, первый вход блока 49 оперативной памяти является информационным входом 47 устройства, а первый выход - информационным выходом 48 устройства, первые управляющие входы первого 58 и третьего 56 управляемых счетчиков соединены с входом 61 зада1тя требуемого числа испытаний устройства, вход и выход группы 50 регистров соединены соответственно с вторыми выходом и входом блока 49 оперативной памяти, выход первого переключателя 14 соединен с входом сброса первого триггера 6, второй выход счетного регистра 23 соединен с первым входом второго элемента И 25, второй вход которого соедигген с выходом первого элемента ИЛИ 24, а выход - с первыми входами первого 32 и третьего 35 регистров, выход элемента 16 задержки соединен с вторым входом первого элемента ШШ 24, второй вход второго ; переключателя 46 соединен с выходом горвого регистра группы 50, выход третьего элемента И 51 соединен с входом второго регистра группы 50, а второй вход соединен с вторым выходом третьего управляемого счетчика 56 и с входом шифратора 59, первый выход блока 52 усреднения соединен с первым входом третьего элемйн11та И третий вход - с выходом второго регистра группы 50, а четвертый вход - с выходом третьего регистра группы 50, вход третьего пере ключателя 10 соединен с выходом вторбго управляемого счетчика 18, выход . Ш1фратора 59 соединен с.входом пятого регистра группы 50, выход которого подключен к ВХОДУ дешифратора 60, первый вход второго элемента ИЛИ 41 соединен с первым выходом управляемо то вероятностного (1-п)-полюсника, 39, а второй вход - с выходом дешифратора 60, выход шестого элемента 28 .И соединен с входом первого генера™ ,тора 29 псевдослучайных чисел, едишгчный выход второго триггера 19 соединен с первым входом блока 52 . усреднения, второй выход которого соединен с первым входом седьмого .элемента И 54, нулевой выход второго триггера 19 соединен с вторым входом блока 52 усреднения и с вторы Ми входами седьмого 54, восьмого 30, девятого 55, десятого 42 элементов И, выход формирователя .20 импульсов записи соединен с первым входом восьмого элемента И 30, выход которого соединен с третьим входом бло ка 49 оперативной памяти и единичным входом третьего триггера 53, .нулевой выход третьего триггера 53 сое динен с первым входом одиннадцатого элемента И 57, выход которого соединен с вторым управляющим входом первого управляемого счетчика 58., выход формирователя 15 импульсов чтения соединец с четвертым входом блока 45 оперативной памяти, выход второго элемента /ИЛИ 41 соединен с первым входом десятого элемента И 42, выход четвертого регистра группы 50 соединен с первым входом десятого элемента И 55, выход которого соединен с вторым ynpaensitoBftw входом третьего управляемого счвтчика 56 и с вторым вxoдo г одиннадцатого элемента И 57, первый выход третьего управляемого счетчика 56 соединен с входом четвертого регистра группы 50, выход седьмого элемента И 54 соединен с входом третьего регистра группы 50, вход второго регистра 3 является входом 2 установки числа шагов устройства, а выход сое:дкквн с первьм входом пятого элемента И 9, второй вход которого подкгшзчен к пер вому входу двенадцатого эпементй И 7 J, к второму входу третьего элемен3912та 1ШИ 4, к входу элемента НЕ 2 Г и к выходу второго элемента 1ШИ 41, выход третьего элемента ИЛИ k соединен с нулевым эходом четвертого триггера 12, единичный вход которого под1 лючен к выходу третьего переключа- , теля 10 и к второму входу четвертого элемента ИЛИ 1, первый вход четвертого элемента И 13 соединен с, единичным выходом четвертого триггера 12, а -второй вход с выходом формирователя 20 импульсов записи и с вторым входом шестого элемента И 28, выход четвертого элемента И 3 3 подключен к третьему входз третьего элемента ЩШ 4, выход ;пятого элемента И 9 соединен с управляющим входом второгоуправляемого счетчика 18, счетный вход которо:го под- , ключей к выходу шестого элемента И 28 и к.первому входу семнадцатого элемента И 37, выход элемента НЕ 21 соединен с третьими входами шестого 28 и восьмого 30 элементов Иг выход двенадцатого элемента И 17 подключен к входу элементJ 16 задержки, а второй вход - к нулевому выходу второго триггера 19 и к пер.вым вхо-, дам четырнад15атого 2 и шестнадцатого 36 элементов И, первый вход шестого- элемента И 28 соединен с единич- 1-1ЫМ выходом второго триггера -19 и с первыми аходами тринадцатого 26 и пятнадцатого 33 элементов И,, второй выход 3™fpaBnHeMoro вероятьостного (1-п)-по,шосника 39 подключен к второму входу тринадцатого элемента И 26 . и к второму входу четырнадцатого элемента И 27, а третий вход - к выходу шестого элемента ИЛИ 38, выход трина,дцатрго элемента И 26 соединен .... . . 1C вторым входом первого регистра 32 выход которого подключен к второму входу .пятнадцатого элемента И 33 выход четырнадцатого элемента И 27 соединен с вторым входом третьего регистра 35, первый вход которого соединен с выходом второго элемента И 25, выход третьего регистра 35 подключен к первому входу шестнадцатого элемента И 36, выход которого соединен с вторым входом пятого элемента ШШ 34, выход пятнадцатого элемента И 33 соединен с первым входом пятого элемента ШШ 34, выход которого подключен к пятому входу блока 49 оперативной памяти, первый вход семнадцатого элемента Н 37 соединен с выходом первого генератора 29 псевдо13случайных чисел, а выход --с пер-, вым входом шестого элемента-ИЛИ 38, первый, вход восемнадцатого элеменфа И 40 соединен с выходам второго ген ратора 31 псевдослучайных чисел, второй вход - с выходом восьмого элемента И 30 и с входом второго ге .нератора 31 псевдослучайных, чисел, а выход - с вторым входом шестого элемента ИЛИ 38, выход десятого эле мента И 42 подключен к счетному вхо ду первого управляемого счетчика 58 Назначениеэлементов устройства следующее. - . На пусковой вход 1 от внешнего формирователя подается сигнал Начало счета ; на вход 2 установки числам шагов также от внешнего форми рователя подается сигнал для устано ки числа шагов и последукицеро его фиксирования во второ регистре 3; с выхода 5 окончания счета поступае I сигнал Окончание счета ; с помощью первого триггера 6 осуществляется пуск и остановка устройства; генера.тор 7 тактовых импульсов задает временную сетку работы устройства; первый переключатель 14 используется при решении задачи для одного узла иш для нескольк1Л узлов исследуемой области; третий переключатель 10 включается при решении параболических уравнений; формирователь 15 импульсов чтения, служит Для тактирования выборки информации из блока 49 оперативной памяти.в регистры группы 50; второй управляемый счетчик 18 осуществляет подсчет числа шагов траектории слзгчайного блуясдания; второй триггер 19 управляет - режимами первого и второго проходов траектории блуждания; формирователь 20 импульсов записи служит для тактирования работы первого 29 и второго 31 генераторов псевдослучайHbix чисел, переноса информации из регистров группы 50 в -блок 49 оперативной памяти и сброса третьего триггера 53; на вход 22 установки начального адреса от внешнего формирователя поступает сигнал выборки начального адреса; счетный регистр 23 фиксирует адрес исследуемого узла области; первый 32 и третий 35 регистры состоят из реверсивных счет чиков координат, обеспечивают возможность решения задач в одно-, двух- и трехмерных областях и исполь Зуются в режимах, соответственно, 3914 первого и второго прохода траектории блуждания; управляемый нероятНОСТ1ШЙ (1-п)-полюсник 39. предназначен для вероятностного преобразования информации и реализации с помоцьп псевдослучайных чисел акона ;блуждания частицы по узлам сеточной области; на вход 43 размерности исследуемой области от внешнего формирователя подается сигнал установки размерности исследуемой обдасти путем переключения выходов управ.ляемого вероятностного (1-п)-полюсника 39; на вход 44 задания закона распределения также от внешнего формирователя подается сигнал задания закона распределения блуждания частицыпо узлам сеточной области; в .блоке 45 постоянной памяти хра.нятся значения вероятностей переходов из исследуемого узла в соседние узлы; на информационный вход 47 от внешнего формирователя поступают сигналы значений законов вероят- костных переходов, начальных «граничных уславий, признаков внешних, граничных и. внутренних узлов; с информационного выхода 48 вы,: аются ре1зультаты решения; группа 50 регистров предназначена для организации обмена анализируемой и результирующей информации; по виду информации, заносимой в регистры группы, их можно разделить на-пять регистров: содержимое, первого определяет вероят- кости перекодов из данного узла в соседние, содержимое второго - начальН1ме и граничные условия, содержимое третьего формируется и используется при повторном проходе траекторий и определяет накопленную сумму весов по всем траекториям, прошедш1Ш через данный узел, содержимое четвертого формируется во время пбв- торного прохода и определяет ко.пичество траекторий, прошедших через данный узел, содержимое пятого определяет принадлежность данного узла к внутренней части области, границе или внешней части области Блок 52 усреднения предназначен для получения среднеис арифметического веса по траекториям, начинающимся с узла, для которого находится решение;.третий триггер 53 управляет коррекцией числа испытаний для каждой новой стартовой точки, кроме первой; третий управляемый счетчик 56 предназначен для подсчета числа траекторий. прошедших через данный узел, н для Обеспечения точно N испытаний для исследуемого узла; первый управляемый счетчик 58 обеспечивает посторое ние точно N траекторий из данного узла; шифратор 59 предназначен для выработки кода П, соответствующего признаку граничного узла и маркировЛи-этим кодом узлов, для которых найдено решение; дешифратор 60 осуществляет дешифрирование последних двух разрядов пятого регистра группы 50 с целью фиксирования окончания построе тя одной траектории, когда последняя попадает на границу на вход 61 задания требуемого числа испытаний от внешнего формирователя подается сигнал для установки требуемого числа испытаний NtpeJ. Предлагаемое устройство обеспечивает возможность решения конечноразностных уравнений как эллиптического, так и параболического типов способом накопления .информации, т.е в режиме двойного прохода траектории блуждания. При этом способе каждая траектория случайного блуждан11я используется для получения оценки решения задачи в различш 1х точках сеточной области одновременно. Воспроизведение траектории случайного блуж дания осуществляется с помощью втор го генератора псевдосл-учайных чисел который идентичен первому генератору и перед началом работы устройства находится в Одинаковом с ним состояРабота устройства, реализующего ускоренный вариант решения уравнений параболического типа методом последо вательного сокращения размерности системы для случая плоской задачи, происходит следующим образом. После ввода исходных данных в бло 49 оперативной памяти по информацион ному входу 47, установки начального адреса (х;, у,) в счетном регистре 23 по входу 22, установки начального адреса занесения числа шагов блуждания К во второй регистр 3 и во второй счетчик 18 (для упрощения цепь первоначальной установки К в счетчик 18 на фиг, 1 не показана) по входу . 2, установки числа шагов, задания размерности исследуемой области по входу 43 размерности исследуемой области, установки N-rpef. по входу 61 задания требуемого числа испытаний в счетчики 56 и 58 и включения тре тьего переключателя 10 на пусковой вход 1 устройства подается сигнал Начало счета (фиг, 2а), который переводит первый 6 и второй 19 триггеры в единичное состояние, а четвертый триггер 12 - в нулевое состояние, осуществляет через элементы ИЛИ 24 и И 25 перенос координат начального узла Р (х|, у,) из счетного регистра 23 в первый 32 -и третий 35 регистры. Тактовые импульсы от генератора 7 тактовых импульсов начинают поступать через элемент И 8 на формирователь 15 импульсов чтения , формирующий импульсы чтения от переднего фрон/а тактовых импульсов, и на формирователь 20 импульсов записи, формирующий импульсы записи от .заднего фронта тактовых импульсов (фиг. 2а). Координаты стартового узла из первого регистра 32 через элементы Н 33 и ИЛИ 34 поступают в блок 49 оперативной памяти, где возбуждают соответствующую ячейку. По импульсу чтения из блока 49 оперативной памяти считывается информация, относящаяся к данному узлу P(xj, у,), в соответствующие регистры группы 50. Из второго регистра группы 50 в блок 52 усреднения поступает начальное значение функции в данном узле Одновременно из первого регистра группы 50 через второй переключатель 46 в (1-п)-полюсник 39 считыЕа атся значения вероятностей перехода узла Р(х, у) в соседние узль1. В соответствии с этими вероятностями начинается построение траектории блуждания: по иьшульсу записи, поступающему с выхода формирователя 20 через элемент И 28 на вход первого генератора 29, последний формирует псевдослучайное число, в соответствии с которым на одном из выходов (l-n)полюсника 39 появляется сигнал, определяющий направление перемещения траектории, Б результате в следующем такте в первом регистре 32.будет новый адрес - адрес узла соседнего со стартовым. Далее процесс построения траектории блуждания повторяется аналогично описанному. Блуждание по траектории заканичивается, если дешифратор 60 зафиксирует признак грашгчного.узла. Траектория может зако1гчнться не только на границе, н.о и в том случае, если она попала в условное поглощающее со стояние с внутреннего узла, фиксируемое (1-п)-полюсником. Во всех этих случаях сигнал Конец траектории с вы хода элемента HJM 41 через элемент 11ПИ 11 поступает на счетный вход триггера 19, устанавливая его в нулевое состоя1те, соответствующее режиму управления вторьи проходом траектории. Накопленная к концу первого прохода в блоке 52 сумма является весом данной траектории для стартовой точки. Для всех промежуточных у лов траектории вес определяется в Процессе повторного прохода этой траектории. При решении параболических уравн ний возможны следующие режимы управ ления вторьтм проходом трактории блу дания. В первом режиме первый проход траектории заканичивается за число шагов меньшее или равное К либо на границе, либо в поглощающей точке сеточной области и, как описывалось выше, триггер 19 устанавливается в нулевое состояние. При этом возбуждаются элементы И 27, 30 и 36, обес печивающие управление вторым проходом траектории с помощью третьего регистра 35 и вторего генератора 31 псевдослучайных чисел. Воспроизведение траектории осуществляется ана логично ее первому проходу, только в этом чтение информации иэ блока 49 в регистры группы 50 по адресу текущего узла траектории чередуется с записью вычисленного в блоке 52 веса этой траектории для данного узла (фиг. 2б). Во второй режим управления вторым проходом устройство переходит по сигналу с выхода счетчика 18, фиксирующего прохождение траекторией блуждания К шагов. При этом триггер 19 устанавливается в нулевое состояние, а триггер 12 - в единичное состояние, обеспечивая через элементы И 13 и ИЛИ 11 подачу 1&шульсов записи на счетный вход триггера 19 (фиг. 2в). Таким образо осуЕ(ествляется управление поочередным за каждый такт построением трае тории как в первом, так и во втором проходах до попадания траектории в первом проходе либо на границу, либо в поглощающий узел. После это .реализуется перпый режим управления 39,8 вторым проходом траектории блужда.ния. После окончания второго прохода каждой траектории происходит увеличение на единицу содержимого счетчика 58 по сигналу с выхода элемента ШМ 41 через Н 42 триггер 19 устанавливается в единичное состояние и адрес начального узла с помощью элементов 17, 16, 24, 25 переписывается из счетного регистра 23 в регистры 32 и 35. Далее моделируется новая траектория из стартовой точки, осуществляется ее повторный проход и Т:,д. После переполнения счетчика 56 вычисление функции для стартового узла заканичивается. Накопленный при этом по N-rpef траекториям вес из третьего регистра группы 50 передается в блок 52, где происходит определение среднего арифметического веса по Ntpe траекториям. Полученное значение функции через элемент Н 54 переписывается во второй регистр группы 50, одновременно шифратор 59 изменяет содержимое пятого регистра группы 50, определяя узел Р(х, У() как грашгчный, затем возбуждается адрес блока 49 и числовая 1Н1формация из регистров группы 50 переписывается D блок -49 по указанному адресу. В дальнейпих вычислениях узел P(xi у,) уже будет выступать S качестве граю1чиого. После переполнения счетчика 58, последний формирует сигнал Конец испытаний, переводяпэ1Й триггер 53 в нулевое состояние и увеличивающий на единицу содер/химое счетного регистра 23. Таким образом, после окончаш1я второго прохода в N Tpef испытании для стартового узла Р(х,-, ) в регистры 32 и 35 поступят координаты новой стартовой точк.и Р(х, , у,-) по сигналу Конец траектории, задержанному элементом 16 задержки. После обхода псех узлов исследуемой области на выходе счетного регистра 23 появляется сигнал Окончание счета, устанавливающ11й триггер 6 в нулевое состояние. При этом результирующая информация из блока 49 выводится либо на печать, либо в универсальную ЭВМ. Предлагаемое устройство обладает следующими техническими преимущестBattOi по сравнению с прототипом: оно имеет больпое быстродействие при решении параболических уравнений за 191 ечет использования двойного прохода траектории блуждания с накоплением паса этой траектории для всех промежуточных узлов. Таким образом, при выборе промежуточных узлов в качестве стартовых значительно ёокрашается время моделирования за счет имеющегося в этих узлах задела по траектории. При рассмотрении всей области ЭТО дает значительное сокра пение объема вычислительных затрат при решении параболических уравнений 9 по сравнению с методом последова- . тельного сокращения размерности системы, вьшолняемом в базовом объекте в один проход траектории. Оценка эффективности (Эф) применения алгоритма с накоплением информации для решения указанных задач, по сравнению с классическим алгоритмом прямого блуждания, определяется выра- жением Эф , где К(.р - средняя длина траектории случайного блуждания.

jm

3$

. гЧ

Авторы

Даты

1983-10-30—Публикация

1981-12-10—Подача