I

Изобретение относится к электроизмерительной технике и предназначено для запоминания аналогового напряжения.

Известно аналоговое запоминающее устройство 1, включающее в себя операционный усилитель и запоминающий конденсатор в цепи его отрицательной обратной связи.

Однако известное устройство не обеспечивает одновременно высокого быстродействия и длительного времени хранения с высокой точностью.

Наиболее близким решением по технической сущности к изобретению является аналоговое запоминающее устройство (АЗУ),которое содержит операционный усилитель, конденсатор, включенный в цепь обратной связи, а между неинвертирующим входом усилителя и шиной нулевого потенциала включены параллельно соединенные допол.нительный конденсатор и размыкающий контакт, что приводит к повышению точности запоминания - уменьшению напряжения утечки запомненного напряжения за счет частичной компенсации входного тока по инвертирующему входу усилителя 2.

Однако при запоминании аналоговых сигналов в длительном временном диапазоне напряжение утечки вследствие неполной компенсации входных токов усилителя, может принимать неприем10лемо большие значения.

Целью изобретения является повышение точности устройства..

Поставленная цель достигается тем, что в аналоговое запоминающее устрой15ство, содержащее основной интегратор, первый вход которого является входом устройства, а выход - выходом устройства, дополнительный интегратор, первый и второй накопительные элементы,

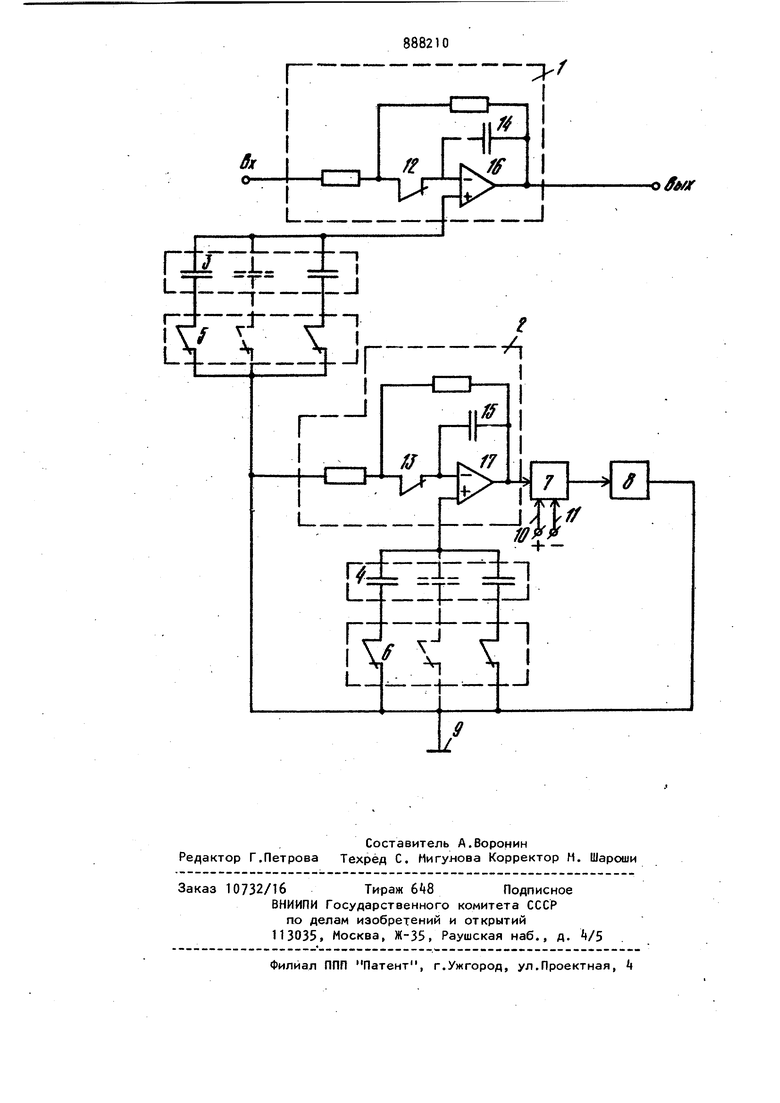

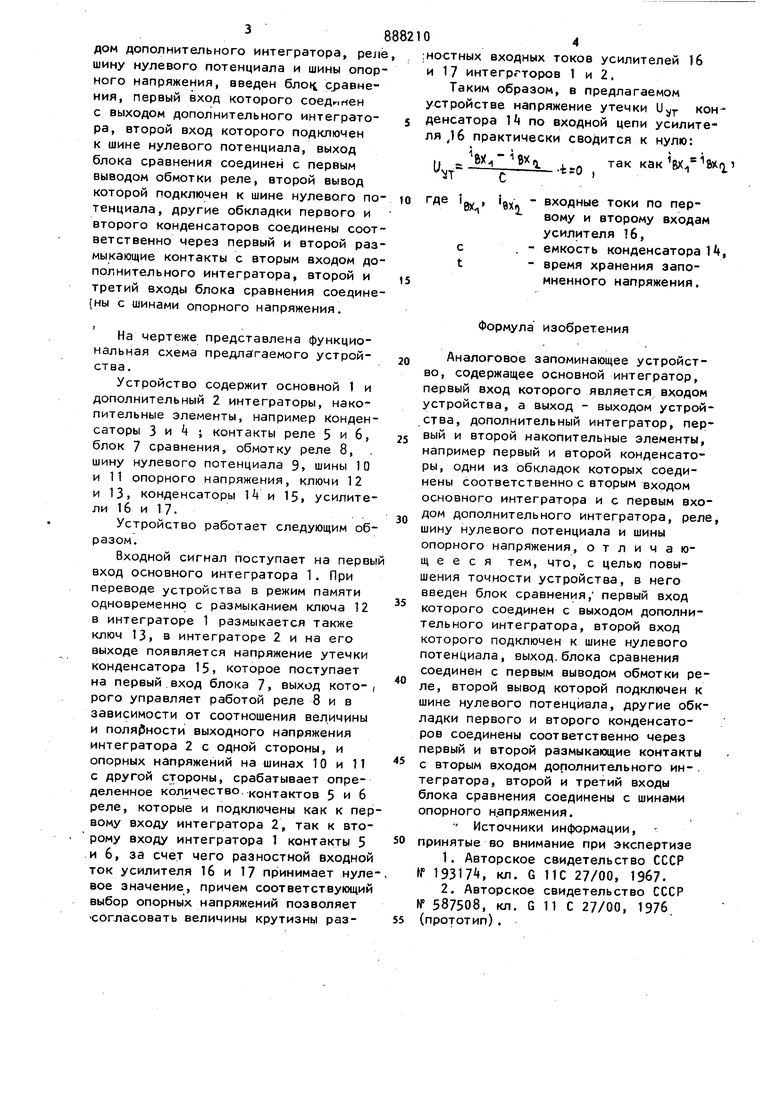

20 например, первый и второй конденсаторы, одни из обкладок которых соединены соответственно с вторым входом основного интегратора и с первым вхо3дом дополнительного интегратора, реле шину нулевого потенциала и шины опор ного напряжения, введен блоц сравнения, первый вход которого соединен с выходом дополнительного интегратора, второй вход которого подключен к шине нулевого потенциала, выход блока сравнения соединен с первым выводом обмотки реле, второй вывод которой подключен к шине нулевого по тенциала, другие обкладки первого и второго конденсаторов соединены соот ветственно через первый и второй раз мыкающие контакты с вторым входом до полнительного интегратора, второй и третий входы блока сравнения соедине (ны с шинами опорного напряжения. На чертеже представлена функциональная схема предлагаемого устройства. Устройство содержит основной 1 и дополнительный 2 интеграторы, накопительные элементы, например конденсаторы 3 и 4 ; контакты реле 5 и 6, блок 7 сравнения, обмотку реле 8, шину нулевого потенциала 9 шины 10 и 11 опорного напряжения, ключи 12 и 13) конденсаторы 14 и 15, усилители 16 и 17. Устройство работает следующим образом. Входной сигнал поступает на первы вход основного интегратора 1. При переводе устройства в режим памяти одновременно с размыканием ключа 12 в интеграторе 1 размыкается также ключ 13, в интеграторе 2 и на его выходе появляется напряжение утечки конденсатора 15, которое поступает на первый вход блока 7, выход которого управляет работой реле 8 и в зависимости от соотношения вел.ичины и поля|5ности выходного напряжения интегратора 2 с одной стороны, и опорных напряжений на шинах 10 и 11 с другой стороны, срабатывает определенное количество.контактов 5 и 6 реле, которые и подключены как к пер вому входу интегратора 2, так к второму входу интегратора 1 контакты 5 и 6, за счет чего разностной входной ток усилителя 16 и 17 пр инимает нуле вое значение, причем соответствующий выбор опорных напряжений позволяет согласовать величины крутизны раз4ностных входных токов усилителей 16 и 17 интегргторов 1 и 2. Таким образом, в предлагаемом устройстве напряжение утечки U,y кон денсатора Ц по входной цепи усилителя 16 практически сводится к нулю: так как )l где i , ig - входные токи по пер вому и второму входам усилителя 16, с . - емкость конденсатора 1, t - время хранения запомненного напряжения. Формула изобретения Аналоговое запоминающее устройство, содержащее основной интегратор, первый вход которого является входом устройства, а выход - выходом устройства, дополнительный интегратор, первый и второй накопительные элементы, например первый и второй конденсаторы, одни из обкладок которых соединены соответственно с вторым входом основного интегратора и с первым входом дополнительного интегратора, реле, шину нулевого потенциала и шины опорного напряжения, отличающееся тем, что, с целью повышения точности устройства, в него введен блок сравнения, первый вход которого соединен с выходом дополнительного интегратора, второй вход которого подключен к шине нулевого потенциала, выход.блока сравнения соединен с первым выводом обмотки реле, второй вывод которой подключен к шине нулевого потенциала, другие обкладки первого и второго конденсаторов соединены соответственно через первый и второй размыкающие контакты с вторым входом дополнительного интегратора, второй и третий входы блока сравнения соединены с шинами опорного напряжения. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 19317, кл. G 11С 27/00, 1967. 2.Авторское свидетельство СССР Vf 587508, кл. G 11 С 27/00, 1976, (прототип).

Ч

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1990 |

|

SU1734123A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU830585A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU905861A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU858112A1 |

| Аналоговое запоминающее устройство | 1983 |

|

SU1267482A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU822294A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU1005191A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU830582A1 |

| Интегратор с запоминанием | 1978 |

|

SU698009A1 |

| Аналоговое запонинающее устройство для узкополосного сигнала | 1988 |

|

SU1695391A1 |

Авторы

Даты

1981-12-07—Публикация

1980-03-26—Подача