Изобретение относится к устройст вам автоматики и вычислительной техники, а именно к аналоговым запоминающим устройствам статического типа, и может быть использовано для запоминания аналогового сигнала в системах управления и информационных устройствах.

Одной из основных характеристик устройств для запоминания аналоговых сигналов является точность в режиме хранения записанного сигнала, которая определяется скоростью изменения выходного напряжения.

Известно аналоговое запоминающее устройство, содержащее входной операционный усилитель, выход которого подключен через нагрузочный элемент к шине нулевого потенциала, а через первый ключ к инвертирующему входу данного усилителя, накопительный элемент, например, конденсатор, одна обкладка которого соединена с шиной нулевого потенциала, выходной операционный усилитель, охваченный отрицательной обратной связью, ключи и шину входного сигнгша. При этом шина входного сигнала через второй ключ соединена с инвертирующим входом входного операционного усилителя и неинвертирующим входом выходного операционного усилителя, выход которого через третий ключ подключен к другой обкладке конденсатора и неинвертирующему входу входного операционного усилителя, выход которого соединен с инвертирующим входом выходного операционного усилителя 1.

10

Недостатком известного устройства является низкая точность в режиме хранения записанного сигнала, обусловленная разрядом запоминающего конденсатора вследствие токов утеч15ки коммутирующего ключа.

Наиболее близким к предложенному по технической сущности является аналоговое запоминающее устройство, содержащее узел сравнения, первый

20 вход которого является входом устройства, второй вход соединен с выходом интегратора, выход которого является выходом устройства, а выход узла сравнения через усилитель соеди25нен с входом ключа. При этом выход ключа подсоединен к входу интегратора, который включает в себя операционный усилитель и конденсатор, введенный в обратную связь. В режи30ме хранения записанного сигнала

ключ разомкнут и напряжение на выхо де интегратора равно напряжению в момент размыкания ключа 2.

Основным недостатком известного устройства является его недостаточная точность в режиме хранения сигнала, что.связано с изменением выходного напряжения, вызываемого разрядом конденсатора, вследствие наличия токов утечки ключа.

Цель изобретения - повышение точности устройства в режиме хранения сигнала путем снижения скорости изменения выходного напряжения тока при устранении влияния то,ков утечки,

Поставленная цель достигается тем, что в аналоговое запоминающее устройство, содержащее интегратор, выход которого соединен с выходом устройства и с первым входом блока сравнения, усилитель, вход которого соединен с выходом блока сравнения, первый ключ, вход которого подключен к выходу .усилителя, второй вход блока сравнения соединен с входом устройства, и шину нулевого по1тенциала, введены нелинейный эле-i мент и второй ключ, вход которого соединен с выходом первого ключа и с входом нелинейного элемента/ выход второго ключа соединен с шиной нулевого потенциала, выход нелинейного элемента соединен с входом интегратора.

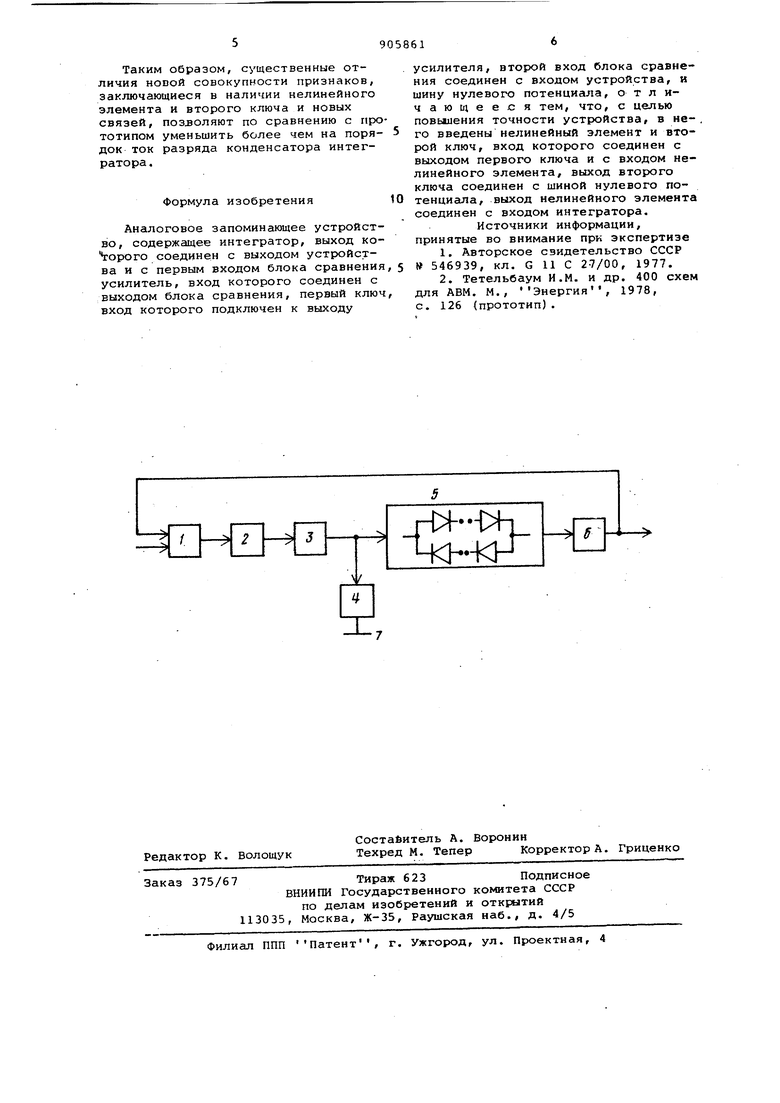

На чертеже показана функциональная схема предложенного устройства.

Оно содержит блок сравнения 1, усилитель 2, ключи 3 и 4, нелинейный элемент 5, интегратор 6 и шину нулевого потенциала 7.

Блок сравнения 1 может быть выполнен в виде двух резисторов, включенных на входе усилителя 2, в качестве которого можно использовать операционный усилитель любого типа. Ключи 3 и 4 могут быть выполнены, например, на полевых или биполярных транзисторах. Нелинейный элемент 5 включает в себя встречно-параллельно соединенные диоды. Интегратор б (как и в известном) может состоять из операционного усилителя и конденсатора включенного в обратную связь, при этом в качестве операционного усилителя можно использовать усилители типа К544 УД1 или К140 УД8.

Устройство работает следующим образом.

Входной сигнал подается на один из входов блока сравнения 1 и сравнивается с сигналом обратной связи, поступающим на др1гой вход с выхода интегратора 6. Сигнал рассогласования через усилитель 2 подается на вход ключа 4. В зависимости от режима работы устройства на вход интегратора 6 через нелинейный элемент 5

подается сигнал либо с выхода ключа 3 (режим записи сигнала), либо через ключ 4 с шины нулевого потенциала 7 (режим хранения записанного сигнала).

В режиме записи сигналу ключ 3 замкнут, ключ 4 разомкнут, сигнал с выхода ключа 3 через нелинейный элемент 5 поступает на вход интегратора 6. При этом сигнал на выходе устройства становится равным входному сигналу за счет отрицательной обратной связи с выхода интегратора 6 на ,|Вход блока сравнения 1. В режиме записи сигнала падение напряжения на диодах нелинейного элемента 5 не сказыйается на величине выходного напряжения за счет выполнения усилителя 2 с большим коэффициентом усиления, В режиме хранения записанного сигнала ключ 3 разомкнут, ключ 4 замкнут, а вход нелинейного элемента 5 через ключ 4 соединен с шиной нулевого потенциала 7. Таким образом, токи утечки ключа 3 отводятся ключом 4 на шину нулевого потенциала 7 и не сказываются на напряжении нелинейного элемента 5. Напряжение нелинейного элемента 5 равно напряжению смещения на входе интегратора б и балансирозкой его операционного усилителя может быть уменьшено до величины порядка единиц микровольт. Выходное напряжение запоминается равным напряжению в момент размыкания ключа 3. Ток разряда конденсатора обратной связи интегратора 6 определяется током, протекающим через нелинейный элемент 5, и следовательно, не зависит от токов утечки ключей 3 и 4 и описывается выражением

r.,

где д - тепловой ток диода нелинейного элемента 5; UCM - напряжение смещения на входе интегратора 6; k - число последовательно включенных диодов; % - температурный потенциал

диодов.

Как следует из приведенного выражения, с уменьшением напряжения смещения на входе интегратора б снижается ток разряда его конденсатора, вследствие чего уменьшается скорость изменения выходного напряжения.

При конкретной реализации макета по предложенному техническому решению использовались кремниевые диоды Д 223Б, операционные усилители К140 УД8 и ключи на полевых транзисторах К284К41. Для такой схемы с параметрами UtM В, Зо 10 А, ff 2,5-10 В расчетная величина тока,протекающего через диоды, бьлла 4-10 А, соответствует разряду запоминающего конденсатора емкостью s 1 мкФ на Z4 МБ за 10 мин. Таким образом, существенные отличия новой совокупности признаков, заключающиеся в наличии нелинейного элемента и второго ключа и новых связей, позволяют по сравнению с про тотипом уменьшить более чем на порядок ток разряда конденсатора интегратора. Формула изобретения Аналоговое запоминающее устройство, содержащее интегратор, выход когорого соединен с выходом устрюйства и с первым входом блока сравнения усилитель, вход которого соединен с выходом блока сравнения, первый ключ вход которого подключен к выходу усилителя, второй вход блока сравнения соединен с входом устройства, и шину нулевого потенциала, о т л ичающееся тем, что, с целью повыиения точности устрюйства, в него введены нелинейный элемент и второй ключ, вход которого соединен с выходом первого ключа и с входом нелинейного элемента, вьлход второго ключа соединен с шиной нулевого потенцисша, выход нелинейного элемента соединен с входом интегратора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР W 546939, кл. G 11 С 2-7/00, 1977. 2.Тетельбаум И.М. и др. 400 схем для АВМ. М., Энергия, 1978, с. 126 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой интегратор | 1977 |

|

SU732905A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ИНТЕГРИРУЮЩЕГО ТИПА ДЛЯ ИЗМЕРЕНИЯ МАЛЫХ ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ | 2018 |

|

RU2693647C1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU858112A1 |

| Аналоговое запоминающее устройство | 1975 |

|

SU746738A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU729642A1 |

| Аналоговое запоминающее устройство | 1976 |

|

SU618797A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU1015444A1 |

| Аналого-цифровой интегратор | 1978 |

|

SU805345A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU936032A1 |

| Аналоговый интегратор | 1979 |

|

SU807326A1 |

Авторы

Даты

1982-02-15—Публикация

1980-06-19—Подача