Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1981 |

|

SU970474A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU957275A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU963105A1 |

| Аналоговое запоминающее устройство | 1987 |

|

SU1531173A1 |

| Аналоговое запоминающее устройство | 1984 |

|

SU1223308A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU894795A1 |

| Аналоговое запоминающее устройство | 1982 |

|

SU1065889A1 |

| Аналоговое запоминающее устройство | 1986 |

|

SU1383448A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU920843A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU991514A1 |

Изобретение относится к вычислительной, контрольно-измерительной технике и предназначено для аналого-цифровых преобразователей, систем сбора данных и устройств аналоговой обработки сигналов. Целью изобретения является повышение точности запоминания. Цель достигается за счет введения четвертого пассивного элемента на переменном резисторе 12, второго операционного усилителя 6. Резистивный делитель 11 и 12 компенсирует сигнал про- лезания, что позволяет повысить точностные параметры схемы АЗУ. 2 ил.

VJ

GJ

ю со

Изобретение относится к вычислительной, контрольно-измерительной технике и предназначено для аналого-цифровых преобразователей, систем сбора данных и устройств аналоговой обработки сигналов.

Известно аналоговое запоминающее устройство, содержащее инвертирующий и неинвертирующий усилители, к входам которых через ключи и пассивные элементы подключены накопительные конденсаторы, сигналы с которых через буферные усилители поступают на дифференциальный усилитель.

Введение в известную схему неинвертирующего усилителя и двух буферных усилителей обеспечивает повышение тока перезаряда и исключает дополнительную погрешность, возникающую при уменьшении длительности сигнала выборки, т.е. приводит к некоторому повышению быстродействия.

Недостатком этого устройства является его низкое быстродейстие, ограниченное быстродействием инвертирующего, неинвертирующего усилителей и пассивных элементов.

Известно аналоговое запоминающее устройство, содержащее два канала, каждый из которых состоит из операционного усилителя с конденсатором между входом и выходом (интегратор), резистора, подключенного между выходом операционного усилителя и входом ключа, выход которого соединен с входом операционного усилителя; резистора, который в одном канале включен между входом устройства и входом ключа, в другом канеле - между шиной нулевого потенциала и входом ключа; суммирующий усилитель, входы которого соединены с выходами операционных усилителей (интеграторов) через пассивные элементы. Введение в рассматриваемую схему операционного усилителя с накопительным конденсатором и резистором обратной связи позволяет уменьшить токи утечки, а при равенстве входных токов по инвертирующим входам можно добиться полного отсутствия напряжения смещения запоминающего напряжения, что позволяет повысить точность аналогового запоминающего устройства.

Недостатком данного устройства является низкое быстродействие, вызванное наличием пассивных элементов (резисторов) на входах, низкая технологичность, вызванная сложность выравнивания входных токов операционных усилителей (особенно при изменении условий эксплуатации) с целью достижения заданной точности.

Наиболее близким к предлагаемому является аналоговое запоминающее устройство, содержащее два управляющих ключа, сумматор, первый и второй накопительные

элементы (конденсаторы), первые обкладки которых соединены с шиной нулевого потенциала, вторые обкладки - с выходами управляющих ключей, входы которых объединены и являются входом устройства; вто0 рая обкладка первого конденсатора также соединена с одним из входов сумматора, выход которого является выходом устройства; вторая обкладка второго конденсатора через повторитель напряжения соединена с вторым входом сумматора. Такое устройст5 во обладает необходимым быстродействием, высокой точностью запоминания входного сигнала при длительном времени сохранения входной информации на выходе.

Недостатком известного устройства яв0 ляется низкая технологичность, вызванная повышенными требованиями к соотношению величин конденсаторов, которое определяет коэффициент передачи устройства, компенсацию сигнала управления ключами,

5 что приводит к снижению точности запоминания входного сигнала.

Целью изобретения является повышение точности запоминания.

Поставленная цель достигается тем, что

0 в аналоговое запоминающее устройство, содержащее два ключевых элемента, два накопительных элемента на конденсаторах, первый операционный усилитель, сумматор, который выполнен на операционном

5 усилителе и трех пассивных элементах на резисторах, первые выводы резисторов первого и второго пассивных элементов объединены и подключены к инвертирующему входу операционного усилителя сум0 матора, выход которого объединен с вторым выводом резистора второго пассивного элемента и является информационным выходом устройства, второй вывод резистора первого пассивного элемента является пер5 вым входом сумматора, первый вывод резистора третьего пассивного элемента подключен к неинвертируемому входу операционного усилителя сумматора, информационный вход первого ключевого элемента

0 является информационным входом устройств, а его информационный выход подключен к первому выводу конденсатора первого накопительного элемента и неинвертирующему входу первого операционно5 го усилителя, инвертирующий вход которого объединен с его выходом и подключен к первому входу сумматора, управляющие входы первого и второго ключевых элементов объединены и являются входом задания режима устройства, информационный выход второго ключевого элемента подключен к первому выводу конденсатора второго накопительного элемента, вторые выводы конденсаторов первого и второго накопительных элементов подключены к шине нулевого потенциала устройства, в него введены четвертый пассивный элемент на переменном резисторе, второй операционный усилитель, неинвертирующий вход которого подключен к первому выводу конденсатора второго накопительного элемента, а инвертирующий вход объединен с его выходом, подключен к второму входу сумматора и является первым выводом переменного резистора четвертого пассивного элемента, второй вывод которого подключен к первому выводу резистора третьего пассивного элемента, информационный вход второго ключевого элемента и второй вывод резистора третьего пассивного элемента подключены к шине нулевого потенциала устройства.

Предлагаемое включение элементов аналогового запоминающего устройства приводит к снятию жестких требований к величине соотношения накопительных конденсаторов по отношению к прототипу, повышает технологичность, так как величина пролезания управляющего сигнала легко устраняется изменением соотношения ре- зистивного делителя на входе сумматора, а значит, повышается точность преобразования входного сигнала.

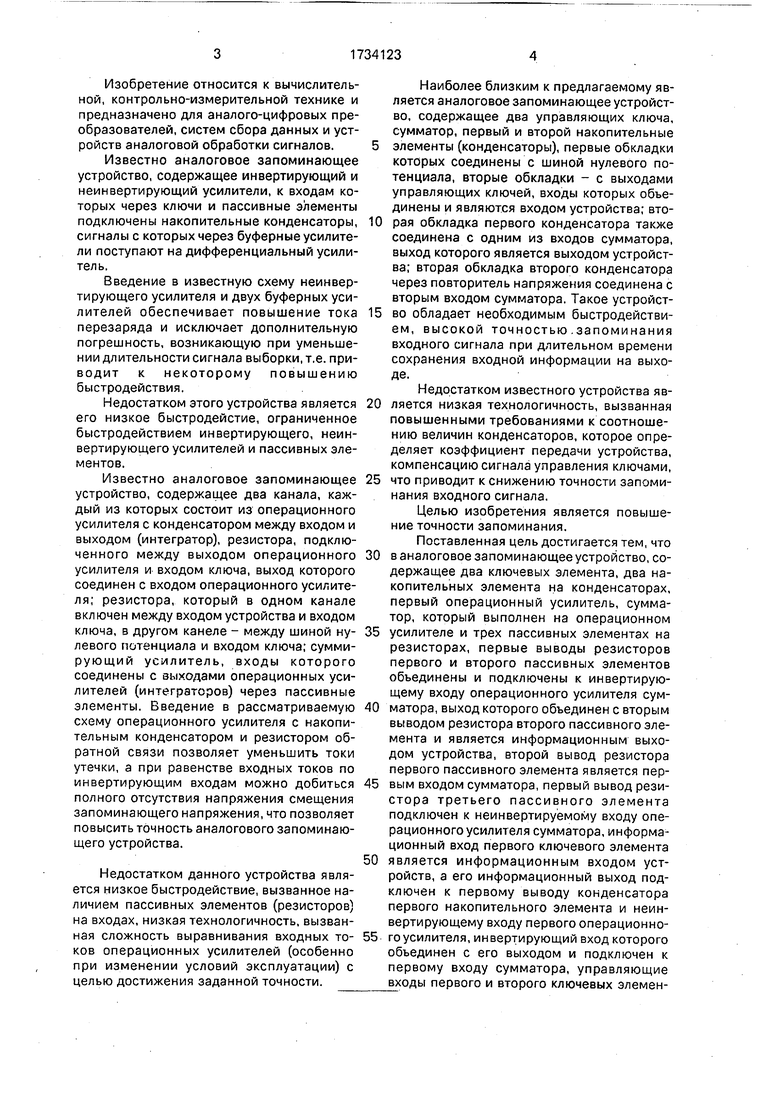

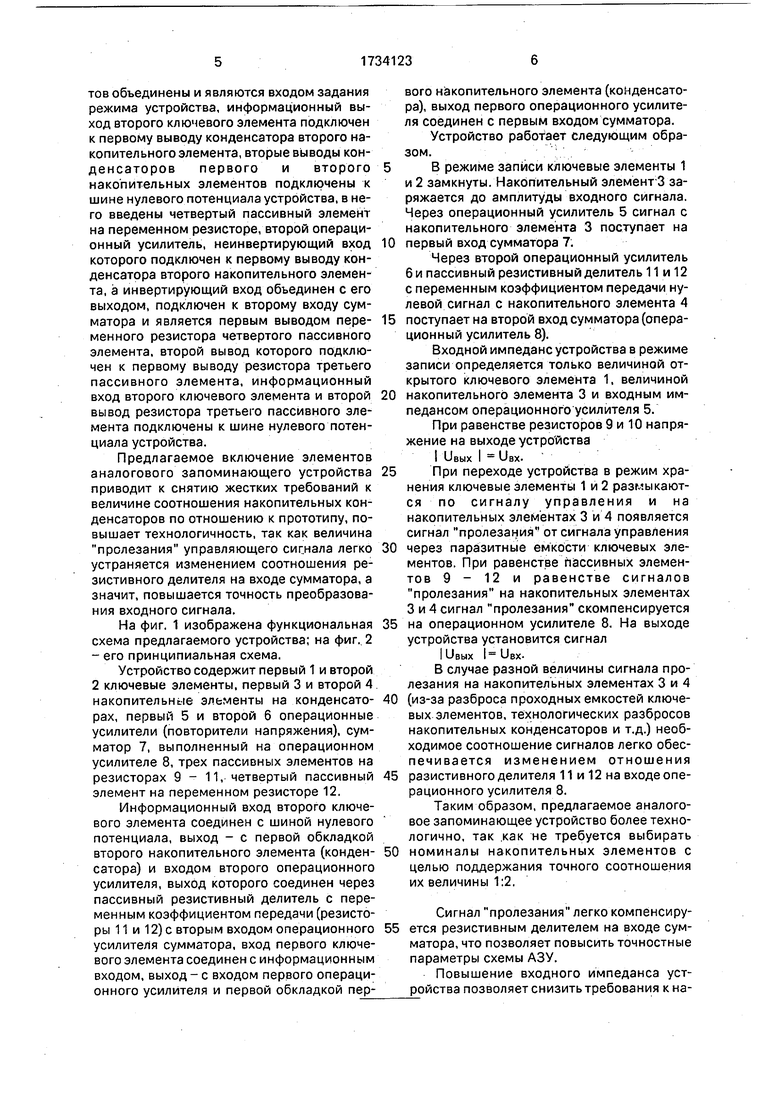

На фиг. 1 изображена функциональная схема предлагаемого устройства; на фиг. 2 - его принципиальная схема.

Устройство содержит первый 1 и второй 2 ключевые элементы, первый 3 и второй 4 накопительное элементы на конденсаторах, первый 5 и второй 6 операционные усилители (повторители напряжения), сумматор 7, выполненный на операционном усилителе 8, трех пассивных элементов на резисторах 9-11, четвертый пассивный элемент на переменном резисторе 12.

Информационный вход второго ключевого элемента соединен с шиной нулевого потенциала, выход - с первой обкладкой второго накопительного элемента (конденсатора) и входом второго операционного усилителя, выход которого соединен через пассивный резистивный делитель с переменным коэффициентом передачи (резисторы 11 и 12) с вторым входом операционного усилителя сумматора, вход первого ключевого элемента соединен с информационным входом, выход - с входом первого операционного усилителя и первой обкладкой первого накопительного элемента (конденсатора), выход первого операционного усилителя соединен с первым входом сумматора.

Устройство работает следующим образом.

В режиме записи ключевые элементы 1 и 2 замкнуты. Накопительный элемент 3 заряжается до амплитуды входного сигнала. Через операционный усилитель 5 сигнал с накопительного элемента 3 поступает на первый вход сумматора 7.

Через второй операционный усилитель 6 и пассивный резистивный делитель 11 и 12 с переменным коэффициентом передачи нулевой сигнал с накопительного элемента 4 поступает на второй вход сумматора (операционный усилитель 8).

Входной импеданс устройства в режиме записи определяется только величиной открытого ключевого элемента 1, величиной накопительного элемента 3 и входным импедансом операционного усилителя 5.

При равенстве резисторов 9 и 10 напряжение на выходе устройства

I Увых I UBX.

При переходе устройства в режим хранения ключевые элементы 1 и 2 размыкаются по сигналу управления и на накопительных элементах 3 и 4 появляется сигнал пролезания от сигнала управления

через паразитные емкости ключевых элементов. При равенстве пассивных элементов 9 - 12 и равенстве сигналов пролезания на накопительных элементах 3 и 4 сигнал пролезания скомпенсируется

на операционном усилителе 8. На выходе устройства установится сигнал Швых l-Uex.

В случае разной величины сигнала пролезания на накопительных элементах 3 и 4

(из-за разброса проходных емкостей ключевых элементов, технологических разбросов накопительных конденсаторов и т.д.) необходимое соотношение сигналов легко обес- печивается изменением отношения

разистивного делителя 11 и 12 на входе операционного усилителя 8.

Таким образом, предлагаемое аналоговое запоминающее устройство более технологично, так как не требуется выбирать

номиналы накопительных элементов с целью поддержания точного соотношения их величины 1:2.

Сигнал пролезания легко компенсиру- ется резистивным делителем на входе сумматора, что позволяет повысить точностные параметры схемы АЗУ.

Повышение входного импеданса устройства позволяет снизить требования к нагрузочной способности источника входного сигнала, снизить его энергоемкость.

Пример конкретного выполнения предлагаемого устройства приведен на фиг. 2. По приведенной схеме выполнено АЗУ в элек- тронном модуле 6П287Е (аналого-цифровой преобразователь). Достигнутая точность преобразования составила ±1%.

Формулаизобретения

Аналоговое запоминающее устройство, содержащее два ключевых элемента, два накопительных элемента на конденсаторах, первый операционный усилитель, сумматор, который выполнен на операционном усилителе и трех пассивных элементах на резисторах, первые выводы резисторов первого и второго пассивных элементов объединены и подключены к инвертрующе- му входу операционного усилителя сумма- тора, выход которого объединен с вторым выводом резистора второго пассивного элемента и является информационным выходом устройства, второй вывод резистора первого пассивного элемента является пер- вым входом сумматора, первый вывод резистора третьего пассивного элемента подключен к неинвертирующему входу операционного усилителя сумматора, информационный вход первого ключевого элемента является информационным входом устройства, а его информационный выход подклю590KHSA

чен к первому выводу конденсатора первого накопительного элемента и неинвертирующему входу первого операционного усилителя, инвертирующий вход которого объединен с его выходом и подключен к первому входу сумматора, управляющие входы первого и второго ключевых элементов объединены и являются входом задания режима устройства, информационный выход второго ключевого элемента подключен к первому выводу конденсатора второго на- копитального элемента, вторые выводы конденсаторов первого и второго накопитальных элементов подключены к шине нулевого потенциала устройства, отличающееся тем, что, с целью повышения точности, в него введены четвертый пассивный элемент на переменном резисторе, второй операционный усилитель, неинвертирующий вход которого подключен к первому выводу конденсатора второго накопительного элемента, а инвертирующий вход объединен с его выходом, подключен к второму входу сумматора и является первым выводом переменного резистора четвертого пассивного элемента, второй вывод которого подключен к первому выводу резистора третьего пассивного элемента, информационный вход второго ключевого элемента и второй вывод резистора третьего пассивного элемента подключены к шине нулевого потенциала устройства.

Ь,1к

10к

| ВЫСЕВАЮЩИЙ АППАРАТ/: ..-лиотЕКЛ | 0 |

|

SU303013A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU970474A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-05-15—Публикация

1990-01-02—Подача