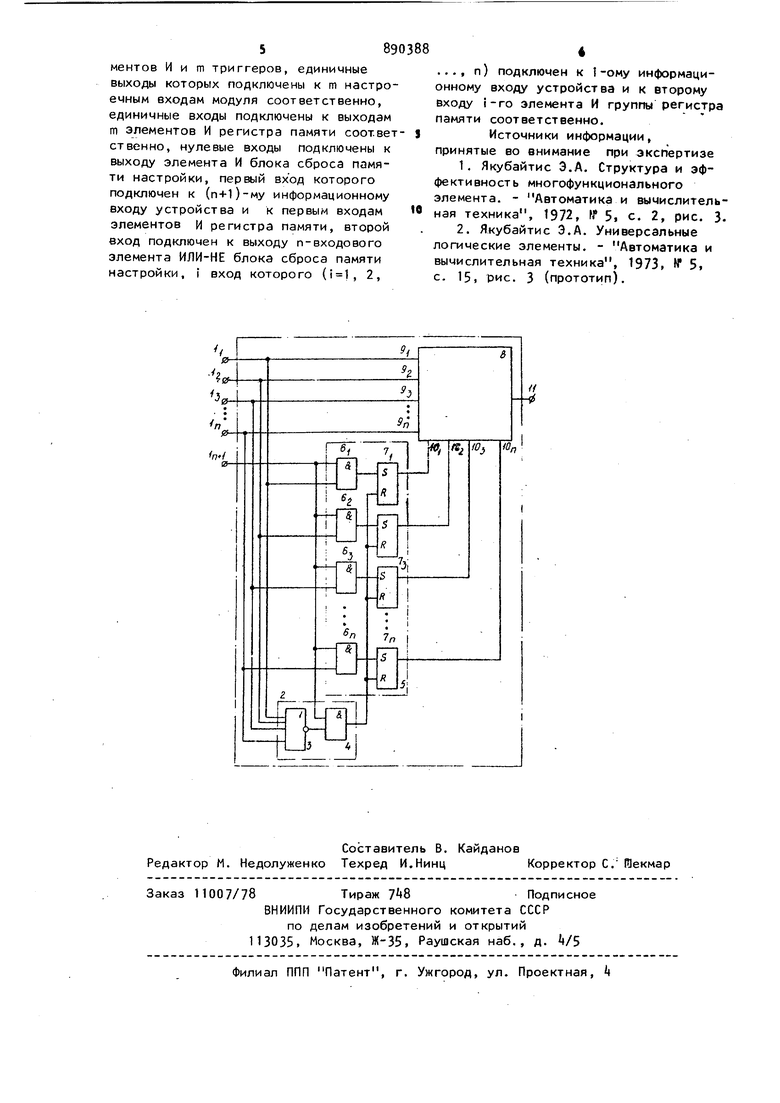

Изобретение относится к автоматике и вычислительной технике и предназ начено для реализации путем настройки булевых функций. Известно устройство с последовател ной настройкой, содержащее в качестве операционного блока многофункциональный логический модуль с п информацион настро ными и п настроечными входами ка которого осуществляется только путем подачи констант О и 1, сдвигающий регистр состоит из п ячеек, а выходы этого регистра подсоединены к соответствующим настроечным входам модуля. Это устройство имеет два настроечных входа, на один из которых последовательно подаются тактовые импульсы, а на второй - код настройки 111 . Недостатком известного устройства является то, что число тактов, которое необходимо для настройки таких устройств велико и равно п. Наиболее близким к предлагаемому по технической сущности является устройство с последовательной настройкой, в котором вместо сдвигающего регистра, содержащего п ячеек, используется счетчик, состоящий из того же числа ячеек. Это устройство имеет всего лишь один настроечный вход, на который подаются настроечные сигналы, число которых равно десятичному эквиваленту кода настройки. Число тактов, необходимых для настройки устройства, может достигать 2 2. Недостатком данного устройства является низкое быстродействие при настройке. Цель изобретения - повышение быстродействия при настройке. Это достигается тем, что настраиваемое устройство, содержащее многофункционаг.ьный логический мбдуль с п информационными входами, подключенными к п информационным входам устройства соответственно, и m настроеч3иыми входами (), дополнительно содержит регистр памяти настройки и блок сброса памяти настройки, содержащий п-входовой элемент ИЛИ-НЕ и двухвходовой элемент И, регистр па-мяти настройки, содержит m двухвходовых элементов И и m триггеров, единичные выходы которых подключены к m настроечным входам модуля соответственно, единичные входы подключены к выходам m элементов И регистра памяти соответственно, нулевые входы подключены к выходу элемента И блока сброса памяти настройки, первый вход которого подклюме.н к (п+1)-му информаиионному входу устройства и к первым входам элементов И регистра памя1И, второй вход подключен к выходу п-входового элемента ИЛИ-НЕ блока сбр са памяти настройки, I вход которого (i 1, 2, ..., п) подключен к i-ому информационному входу устройст ва и к второму входу i-ro элемента И группы регистра памяти соответственно. На чертеже приведена схема настра ваемого устройства. Настраиваемое устройство содержит (п+1 ) входов 1,, и, ..., 1ц, Inti блок 2 сброса памяти настройки, сост ,щий из п-входового элемента ИЛИ-НЕ 3 и двухвходового элемента И k, регист 5 памяти, состоящий из п двухвходоаых элементов И 6i , 6, ..., 6ni и п триггеров с раздельными входами, информация в которых не разрушается пр снятии напряжения питания 7i. 7г, 7т, многофункциональный логический модуль 8 с п информационными Э, За ..., 9п и m настроечными входами 10, , 102, .. 10, выход 11. Функционирование устройства происходит а1едующим образом. При подаче на (п+1) вход устройства первого импульса и отсутст вии сигналов на первых п входах устройства 1, , Ij, ..., 1п срабатывает элемент И k блока сброса, так как пр этом на выходе элемента ИЛИ-НЕ 3 име ется единичный сигнал. Выходной сигнал элемента И k блока сброса переводит все триггеры 7( 72., 7т регистра памяти 5 в состояние О. Если код настройки состоит из всех н лей, то на этом настройка устройства завершается. Если в коде настройки присутствует хотя бы одна единица, т настройка осуществляется следующим образом. На первые п входы устройств 1 1 г1 подается код настройки. С выхода элемента ИЛИ-НЕ исчезает единичный сигнал, и блок сброса отключается от выходов установки в О триггеров регистра памяти. После этого на (n-fl )-й вход устройства подается второй импульс. Единичный сигнал появляется на выходах всех тех элементов И, на первые входы которых поступают единичные сигналы со входов устройства. Эти сигналы соответствуют тем разрядам кода настройки, в которых имеются единицы. Триггеры, связанные с элементами И, на выходе которых имеется единичный сигнал, переходят в состояние 1, а на единичных выходах этих триггеров появляются единичные сигналы, поступающие на соответствующие настроечные входы модуля. Таким образом, модуль настраивается на реализацию требуемой булевой функции. При этом код настройки записан в регистре памяти. Настройка устройства осуществлена всего лишь за два такта - такта обнуления и такта записи кода настройки. Выигрыш по времени настройки по сравнению с известным,имеющим то же самое число внешних выводов, может достигать раз. В силу того, что в устройстве применяются триггеры, информация в которых не разрушается при снятии напряжения питания, его настройка может осуществляться в одном приборе (приборе настройки), а использование - в другом (проектируемом приборе). После того как устройство настроено на реализацию заданной функции, оно может применяться для реализации любой схемы (в том числе и асинхронной) как логический модуль с п входами. Формула изобретения Настраиваемое устройство, содержащее многофункциональный логический модуль с п информационными входами, подключенными к п информационным входам устройства соответственно, и m настроечными входами (п sт), отличающееся тем, что, с целью повышения быстродействия при настройке, устройство дополнительно содержит регистр памяти настройки и бюк сброса памяти настройки, содержащий п-входовой элемент ИЛИ-НЕ и двухвходовой элемент И, регистр памяти настройки содержит m двухвходовых эле5890

ментов И и m триггеров, единичные выходы которых подключены к m настроечным входам модуля соответственно, единичные входы подключены к выходам m элементов И регистра памяти соответственно, нулевые входы подключены к выходу элемента И блока сброса памяти настройки, первый вход которого подключен к (п+1)-му информационному входу устройства и к первым входам элементов и регистра памяти, второй вход подключен к выходу п-входового элемента ИЛИ-НЕ блока сброса памяти настройки, i вход которого (, 2,

.... п) подключен к -ому информационному входу устройства и к второму входу i-ro элемента И группы регистра памяти соответственно.

Источники информации, принятые во внимание при экспертизе

1,Якубайтис Э.А, Структура и эффективность многофункционального элемента. - Автоматика и вычислительная техника, 1972, ff 5, с. 2, рис. 3.

2.Якубайтис Э.А. Универсальные логические элементы. - Автоматика и вычислительная техника, 1973, N 5, с. 15, рис. 3 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный логическийМОдуль | 1979 |

|

SU838700A1 |

| Устройство для реализации логических функций | 1981 |

|

SU1001080A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1661752A1 |

| Арифметико-логическое устройство для умножения чисел по модулю | 2017 |

|

RU2653263C1 |

| ТРЕХКАСКАДНАЯ КОММУТАЦИОННАЯ СИСТЕМА | 2007 |

|

RU2359313C2 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1982 |

|

SU1072036A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ПРОГРАММНО-УПРАВЛЯЕМОЙ СРЕДЫ | 1997 |

|

RU2132081C1 |

| МАТРИЧНЫЙ КОММУТАТОР С ПРОГРАММИРУЕМОЙ ЛОГИКОЙ | 2003 |

|

RU2251792C2 |

| Генератор псевдослучайных последовательностей | 1981 |

|

SU1023325A1 |

| Устройство для умножения элементов конечного поля GF(2 @ ) при м @ 3 | 1990 |

|

SU1728858A1 |

Авторы

Даты

1981-12-15—Публикация

1979-10-15—Подача