(54) УСТРОЙСТВО ДЛЯ РЕАЛИЗАЦИИ ЛОГИЧЕСКИХ ФУНКЦИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический вычислитель в системе остаточных классов | 2016 |

|

RU2637488C1 |

| САМОПРОВЕРЯЕМЫЙ МОДУЛЯРНЫЙ ВЫЧИСЛИТЕЛЬ СИСТЕМ ЛОГИЧЕСКИХ ФУНКЦИЙ | 2009 |

|

RU2417405C2 |

| Устройство для вычисления систем логических функций | 1985 |

|

SU1264160A1 |

| Устройство умножения булевых матриц | 1980 |

|

SU959063A1 |

| САМОПРОВЕРЯЕМЫЙ СПЕЦИАЛИЗИРОВАННЫЙ ВЫЧИСЛИТЕЛЬ СИСТЕМ БУЛЕВЫХ ФУНКЦИЙ | 2012 |

|

RU2485575C1 |

| МОДУЛЯРНЫЙ ВЫЧИСЛИТЕЛЬ СИСТЕМ БУЛЕВЫХ ФУНКЦИЙ | 2007 |

|

RU2373564C2 |

| Настраиваемое устройство | 1979 |

|

SU890388A1 |

| Адаптивное вычислительное устройство | 1980 |

|

SU957214A1 |

| Программируемое логическое устройство | 1991 |

|

SU1777133A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

. .1.

Изобретение относится к автоматике и вычислительной технике и предназначено для реализации систем булевых функт ций.

Известно логическое устройство, предназначенное для реализации систем Qyyie- вых функций 1 .

Недостатком данного устройства является значительная сложность.

Шиболее близким к предлагаемому о по технической сущности является устройство длза 1)ешения логических задач, содержащее коммутатор грутш nepe jeHBtbpc о первой и второй группами йнгЬормационных входов, ifvi управляющими входами и tl ВЬР ts ходами, одновыходнрй настраиваемый логический модуль с Y информационными и 2 настроечными входами, универсальный в классе всех булевых функций от Л переменных, блок посто5шной памяти 20 значений реализуемых (функций с tvt входами и 2 выходами, распределитель не- ; ременных с одним информационным и Уп

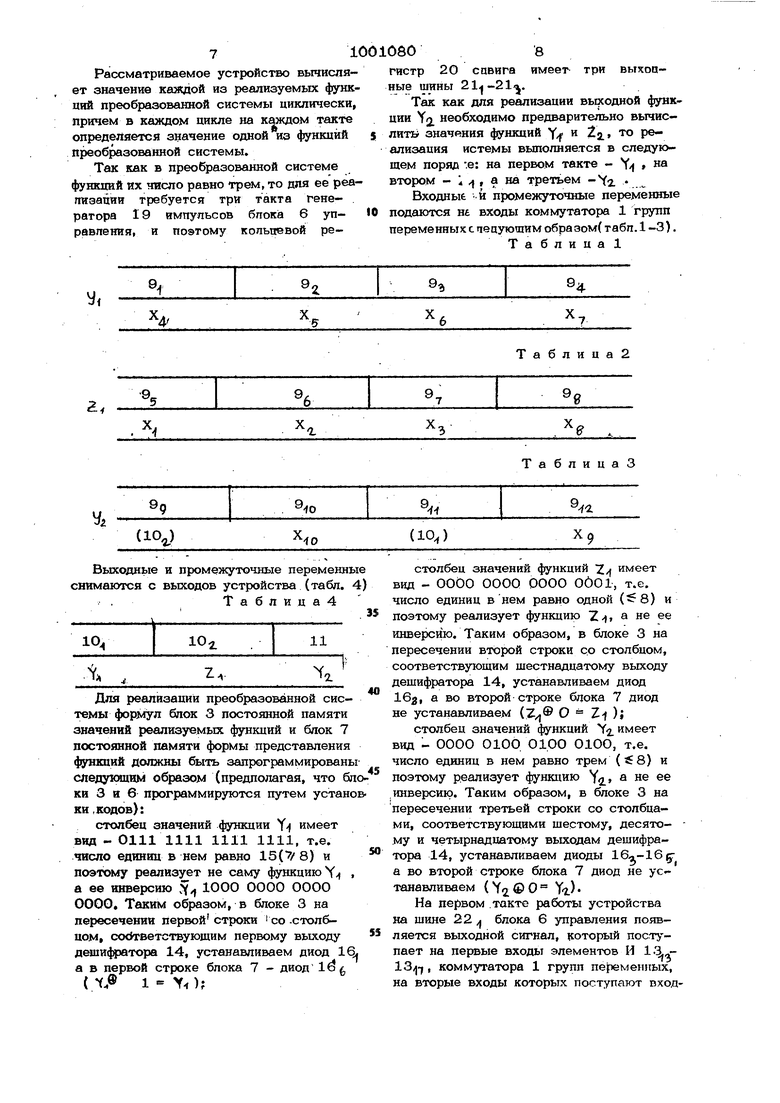

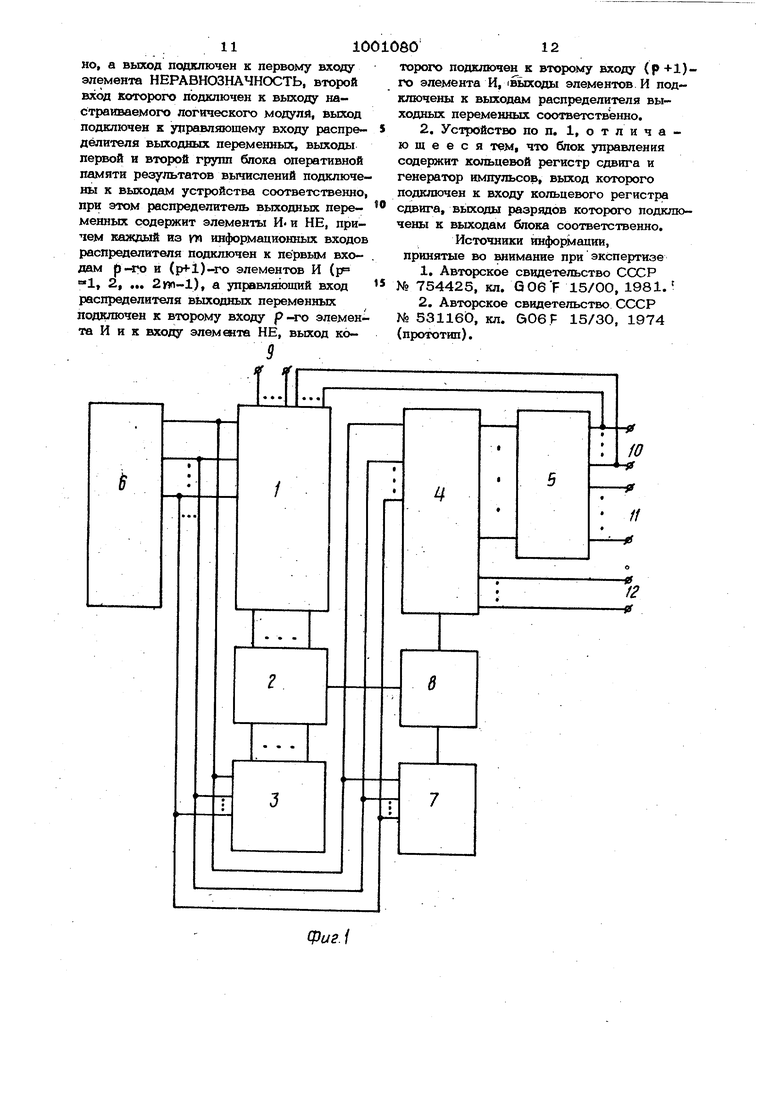

управляющими входами и двумя группами выходов, вторая из которых содержит 2УУ выходов, блок оперативной памяти результатов вычислений с 2 км входами и первой группой выходов, блок управления с m входами, входы и импульсные выходы, причем входы устройства соединеш 1 с перврй группой информационных входов коммухатора, а вторая группа его информационных входов - с первой группой выходов блока оперативной памяти, -j -ый выход коммутатора соединен с -1 -ым информационным входом настраиваемого логического модуля (-т 1, ... ,п), J-ый настроечный вход модуля соединен с j-ым выходом блока постоянной памяти значений реализуемых функций (j 1, ... , и), к-ый выход блока управления соединен с К -ым упpaвляющшv входом коммутатора групп неременных, X -ым входом блока постоянной памяти значений реализуемых функ-; ций и К-ым управляющим входом рас- пределителя переменных (И 1, ... ,) первая группа выходов распределителя соединена с импульсными выходами устройства, 2-Ь1й выход йтьрбй группы вьь ходов распределителя: соеди:&ен с -ым входом блока оперативной памяти резуль татов вьгчислений { S 1, 2, ... 2ni). В известном устройстве одновыходной логический модуль с И информационными и 2 настроечными входами, универсальный в классе всех булевых функций от Л переменных, реализован в виде дешиф ратора с УТ входами и 2 выходами, 2 логических элементов И и 2 - входовог логического элемента Wllif2. Недостатками устройства являются высокая сложиостъ блока постоянной , памяти, значений реализуемых функций и соответствен11о сложность операции настройки устройства (при реализации этого блока в виде диодной матрицы чис ла диодов, устанавливаемых в каждой строке, определяется числом единиц в столбце значений вычисляемой функции при всех возможньк наборах входных переменных, составляющих группу; и может достигать величины 2 -1, где К1- числ входных переме шых в группе), распределитель переменных осуществляет только распределение команд записи на триггеры блока оперативной памяти результатов вычислений, но не обеспечивает сброса этих триггеров до начала работы ив процессе функционирования, чаю усложняет бпсяс управления и определяет наличие св51зей между блоком оперативной памяти и блоком управления. Кроме того, известное устройство не позволяет управлять исполнительными механизмами имеющими потенциальные входы, так как выходы устройства не имеют связи с элементами памяти и блока оперативной памяти. Цель изобретения - упрющение и расширение области применения устройства за счет возможности формирования выходных потенциальных сигналов. Поставленная цель достигается тем, что устройство для реализации логичес. ких функций, содержащее блок управлени коммутатор, настраиваемый логический модуль блок постоянной памяти значений реализуемых функций, распределитель выходных переменных и блок оператугоно памяти результатов вычислений, причем выходы блока управления подключены к управляющим входам коммутатора и к информационным входам блока постоянно памяти значений реализуемых функций и распределителя выходных переменных соответственно, первая группа информационных входов коммутатора подключена к информационным входам устройства соответственно, вторая группа информа- . ционных входов коммутатора подключена к информационным выходам первой группы блока оперативной памяти результатов вычислений соответственно, входы которого подключены к выходам распределителя выходных переменных соответственно, первая группа входов настраиваемого логического модуля подключена к выходам коммутатора соответственно, вторая группа входов настраиваемого логического модуля подключена к выходам блока постоян- ной памяти значений реализуемых функций соответственно, устройство также содержит элемент НЕРАВНОЗНАЧНОСТЬ и блок постоянной памяти форм представления функций, входы которого подключены к выходам блока управления соответственно, а выход подключен к первому входу элемента НЕРАВНОЗНАЧНОСТЬ, второй вход которого подключен к выходу настраиваемого логического модуля, а выход подключен к управляющему входу распределителя выходных переменных, выходы первой и второй групп блока оперативной памяти результатов вычислений подключены к выходам устройства соответственно, при этом распределитель, выходных переменных содержит элементы И и НЕ, причем каждый из ум информаЛ ционных входов распределителя подключен к первым входам р-го и (р+1) -го элементов И (р 1, 2, ... .2уу|-1), а управляющий вход распределителя выходных переменных подключен к второму входу р-го элемента И и к входу элемента НЕ, выход которого подключен к второму входу ()-го элемента И, выходы элементов И подключены к выходам распределителя выходных переменных соответственно. Кроме того, блок управления содержит кольцевой регистр сдвига и генератор импульсов, выход которого подключен к входу кольцевого регистра сдвига,, выходы разрядов которого подключены к выходам блока соответственно. На фиг„ 1 представлена структурная схема устройства; на фиг. 2 - функциональная схема, устройства, реализующего заданную систему булевых формул. Устройство для реализации логргческих функций (фиг. 1) содержит коммутатор 1 групп переменных, дешифратор 2, блок 3 постоянной памяти значений реализуем функций, распределитель 4 выходньк переменных, блок 5 оперативной памяти р зультатов вычислений, блок 6 управпеНИИ, блок 7 постоянной памяти формы представления функций, элемент НЕРАВНОЗНАЧНОСТЬ 8, входы , первую 10/ и вторую 11 группы потенциальных выходов и импульсные выходы 12. Функциональная схема устройства (фиг. 2) содержит логические элементы И Дешифратор 4x16 - 14, логический элемент ИЛИ 15, диоды 16, , логический элемент НЕ 17, RS -тригге ры , , генератор 19 импульсов, кольцевой регистр 2О сдвига, шины 21 и 22. . Блок 6 управления (фиг. 1) состоит из генератора 19 импульсов и кольцево го регистра 20 сдвига (фиг. 2). Упрощение блока 3 постоянной памяти значений реализуемых функций и соответственно сложность операции настро ки достигается за счет обеспечения в предлагаемом устройстве возможности реализации соотношений f®- и Ye-l-Y Предполагая, что блоки постоянной памяти программируются путем установк диодов, необходимо, чтобы после проведе ния операции настройки число диодов в них было минимальным. Если Г : то Необходимо использовать соотношение tp-f- , т.е. в соответствующей строке настраиваемого логического модуля 2 устанавливается Y диодов, размешение которых определяется расположением единиц в столбце значений функций Y , где f- - ранг функций (число единиц в столбце значений функции Y ). Если , то необходимо использовать соотношение Y Y ив соответствующей строке блоков 3 и 7 устанавливается l - r+l диодов. Приведем другие соотношения, определяющие ocHOBHbie характеристики устройства. Число тактов Т, требующихся для реализации системы из булевых формул, заданных в базисе , V © j в пра вых частях KOTopbix суммарное число букв Н 1) , удовлетворяет соот ношению где У1 - число переменных, от которого настраиваемый логический модуль, используемый в схеме устройства, универсален в классе всех булевых функций. Для числа входов устройства справедливо соотношение: .-NЧисло двухвходовых элементов И в коммутаторе 1 групп переменных удовлет воряет соотношению; Число двухвходовых элементов И в настраиваемом модуле устройства определяется соотношением U2.t2 Число двухвходовых элементов И в распределителе 4 выходных переменных удовлетворяет соотношению: J,U,,.(). Общее число элементов И в схеме устройства ,..«) Использование устройства предполагает наличие только прямых выходов у источников информации и триггеров оперативной памяти и не требует наличия юс инверсных выходов.- Принцип действия устройства рассмотрим на примере (фиг. 2) реализации на его потенциальных выходах следующей системы булевых формул : Ч2.ЧХ „ X V X о) Х4. Так как в данном случае в устройстве используется настраиваемый логический модуль, реализующий путем настройки юбую функцию от четырех переменных, то представим заданную систему функций в виде системы, в которой каждая из ункций зависит не более, чем от четырех переменных vvgvy vy . ,,Xg ()V,X).

Рассматриваемое устройство вычисляет значение каждой из реализуемых функций преобразованной системы циклически, причем в каждом цикле на каждом такте определяется значение одной из функций преобразованной системы.

Так как в преобразованной системе функций их число равно трем, то для ее реапизации требуется три такта генератора 19 импульсов 6noKia 6 управления, и поэтому кольиевой реX.

Ч Выходные и промежуточные переменны снимаются с выходов устройства (табл. .Т а б л и ц а 4 Для реализаций преобразованной системы формул блок 3 постоянной памяти значений реализуемых функций и блок 7 постоянной памяти формы представления функций должны быть запрограммированы следующим образом (предполагая, что бл ки 3 и 6 программируются путем устано ки .кодов): столбец значений функции Y-i имеет вид - 0111 1111 1111 1111, т.е. число единиц в нем равно 15(/в) и поэтому реализует не саму функцию Y а ее инверсию 1000 0000 0000 ОООО, Таким образом, в блоке 3 на пересечении первой строки со -столбцом, соответствующим первому выходу деши4 тора 14, устанавливаем диод 1Q а в первой строке блока 7 - диод 1и/ (Ч.® 1 У4)

гистр 20 спвига имеет три выхопные шины .

Так как для реализации выходной функции Yi необходимо предварительно вычислить значения функций Yf и Zi то реализация истемы выполняется в следующем поряд .е: на первом такте - Y/i на втором - i , а на третьем -Ча

Входные и промежуточные переменные подаются н входы коммутатора 1 групп переменных с пецующим образом( табл. 1 -3). Таблица 1

X.

Таблица2

ТаблицаЗ столбец значений функций Z/t имеет вид - ОООО 0000 0000 OOOl, т.е. число единиц в нем равно одной (8) и поэтому реализует функцию Z -|, а не ее инверсию. Таким образом, в блоке 3 на пересечении второй строки со столбцом, соответствующим щестнадцатому выходу дешифратора 14, устанавливаем диод 16, а во второй строке блока 7 диод не устанавливаем ()i столбец значений функций У. имеет вид - ОООО 0100 0100 0100, т.е. число единиц в нем равно трем (8) и поэтому реализует функцию Y. не ее , инверсию. Таким образом, в блоке 3 на пересечении третьей строки со столбцами, соответствующими щестому, десятому и четырнадцатому выходам дешифратора 14, устанавливаем диоды 16 -165а во второй строке блока 7 диод не устанавливаем (Yj © О У-г) На первом такте работы устройства на щине 22 блока 6 управления появляется выходной сигнал, который поступает на первые входы элементов И Iiv13 -j, коммутатора 1 групп пе ремениых, на вторые входы которых поступают входные переменные Хд - Х-у со входов 9 9ц. Эти сигналы поступают на информационные входы настраиваемого логического модуля 2 (на входы дешифратора 4x16-14), а на настроечные входы (вторые входы элементов И 13.,-13 подается сигнал настро&кщ определяемый расстановкой диодов в первой строке блока 3. На выходе элемента НЕРАВ НОЗНАЧНОСТЬ 8 появляется выходной сигнал, равный вычисленному значению функции Y-f на этом такте. В случае, если сигнал на выходе элемента 8 равен 1, то появляется сигнал на выходе элемента И 13 рас пределителя 4 выходных переменных, который поступает на вход установки триггера 18 блока 5 оперативной памя ти результатов вычислений. После срабатывания этого триггера появляется единичный сигнал на выходной шине 1О который поступает также и на вход 9 так как переменная Y входит в функцию 2 , которая реализуется на третьем такте. В случае, если сигнал на выходе эле мента 8 равен О, то на выходе элеме Tia НЕ 17 появляется сигнал, равный единице, что приводит к появлению единичного сигнала на выходе элемента И 13 5, который поступает на вход 18 сброса триггера блока 5 оперативной памяти результатов вычислслмй. После перехода этогю триггера в состо$шие О на выходной шине 10 пояпвляется нулевой сигнал, поступающий также и на ВХОД 9, На остальньгх двух тактах рассматри ваемого цикла при реализации функций Z-1 и YI и на последующих циклах устройство работает аналогично. Таким образом в предлагаемом устройстве обеспечивается упрощение. .Действительно, для реализации рассматриваемой системы функций в устрой стве суммарное число диодов в обоих блоках постоянной памяти равно шести, в то время как в прототипе в блоке постояшюй памяти в этом случае должно быть 19 диодов (введение одного двухвходового элемента НЕРАВНОЗНАЧНОСТ в предлагаемое устройство его сложность практически не увеличивает). При реализации более сложных систем функций Достигается еше более сушественньй выигрьш в количестве диодов. Структура распределителя переменных позволяет подавать на триггера оперативной памяти не только команды записи, но и команды сброса. Кроме того, структура распределителя позволяет не производить первоначальный сброс триггеров оперативной памяти, так как уже в первом цикле .распределитель производит их правильную установку. Это также приводит к упрощению устройства, так как при этом упрощается блок управления и устраняются связи между устройством управления и блоком оперативной памяти Расширение области применения достигается тем, что предлагаемое устройство обеспечивает возможность управления исполнительными механизмами, имеющими потенциальные входы. Формула изобретения 1. Устройство для реализации логических функций, содержащее блок управления, коммутатор, настраиваемый логический модуль, блок постоянной памяти значений реализуемых функций, распределитель выходных переменных и блок оперативной памяти результатов вычислений, причем выходы блока управления подключены к управляющим входам коммутатора и к информационным входам блока постоянной памяти значений реализуемых функций и распределителя выходных переменных соответственно, первая группа информационных входов коммутатора подключена к информационным входам устройства соответственно вторая информационных входов коммутатора подключена к информационным выходам первой труппы блока оперативной памяти результатов вычислений соответственно, входы которого подключены к выходам распределителя выходных переменных соответственно, первая группа входов настраиваемого логического модуля подключена к выходам коммутатора соответственно, вторая грудпа входов настраиваемого логического модуля подключена к выходам блока постоянной памяти значений реализуемых функций соответственно, отличающееся тем, что, с целью упрощения и расширения области применения за счет возможности формирования выходных потенциальных сигналов, оно содержит элемент НЕРАВНОЗНАЧНОСТЬ и блок посто5шной памяти форм представления функций, входы которого подключены к выходам блока управления соответственно, а выход подключен к первому входу элемента НЕРАВНОЗНАЧНОСТЬ, второй вход которого подключен к выходу настраиваемого логического модули, выход подключен к управляющему входу распределителя выходных переменных, выходы первой и второй групп блока оперативной памяти результатов вычислений подключены к выходам устройства соответственно, при этом распределитель выходных переменных содержит элементы И- и НЕ, причем каждый из V7I информационных входов распределителя подключен к первьп входам р-го и ()-1Ч элементов И (р 1, 2, ,., 2пп-1), а управляющий вход распределителя выходных переменных подключен к второму входу р-го элемента И и к входу элемента НЕ, выход ко- 10 6012 торого подключен к второму входу (р +1)го элемента И|1выхо|ды элементов И подключены к выходам распределителя выходных переменных соответственно. 2. Устройство по п. 1, о т л и ч а ю щ е е с я что блок управления содержит кольцевой регистр сдвига и генератор импульсов, выход которого подключен к входу кольцевого регистра сдвига, выходы разрядов которого подключены к выходам блока соответственно. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР № 754425, кл. Q06F 15/00, 1981. 2.Авторское свидетельство СССР № 531160, кл. G06F 15/30, 1974 (прототип).

Авторы

Даты

1983-02-28—Публикация

1981-09-03—Подача