1

Изобретение относится к цифровой вычислительной технике и автоматике и может быть использовано в информационно-измерительных системах и устройствах, требующих дискретное изменение в большом диапазоне стабилизированной частоты, например в цифровых задатчиках частоты, в цифровых реле времени, в формирователях временных интервалов и пачек импульсов, в частотомерах, для цифровых систем управления, в качестве управляемого делителя частоты в синтезаторах частот, в преобразователях кода в частоту и т.д.

Известен делитель частоты с про- граммным заданием коэффициента деления, содержащий генератор, соединенный с переключателем, программный блок, выходы которого подключены к установочным входам пересчетного устройства t-LlНедостатком этого устройства является ограниченная возможность в управлении, так как устройство не позволяет корректировать выходную частоту без изменения программы в программном блоке.

Известен делитель частоты с переменным коэффициентом деления, содержащий входную шину, П последовательно соединенных счетных декац, П элементов сравнения, первые входы которых соединены с выходами соответствующих счетных декад, задающий блок, информационные выходы которого соединены со вторыми входами соответствующих элементов сравнения, П-1 декадных элементов И, первые входы которых

10 соединены с выходами соответствующих элементов сравнения, элемент задержки и триггеры 2.

Однако в схеме устройства отсутствует вход синхронизации момента смены коэффициента деления, и поэтому этот делитель частоты не может работать в режиме автоматического управления. Он не позволяет также формировать одновременно функционально эави20 симые, автоматически корректируемые и изменяемые сигналы, что сужает функциональные,возможности.

Цель изобретения - расширение функциональных возможностей устройст25ва.

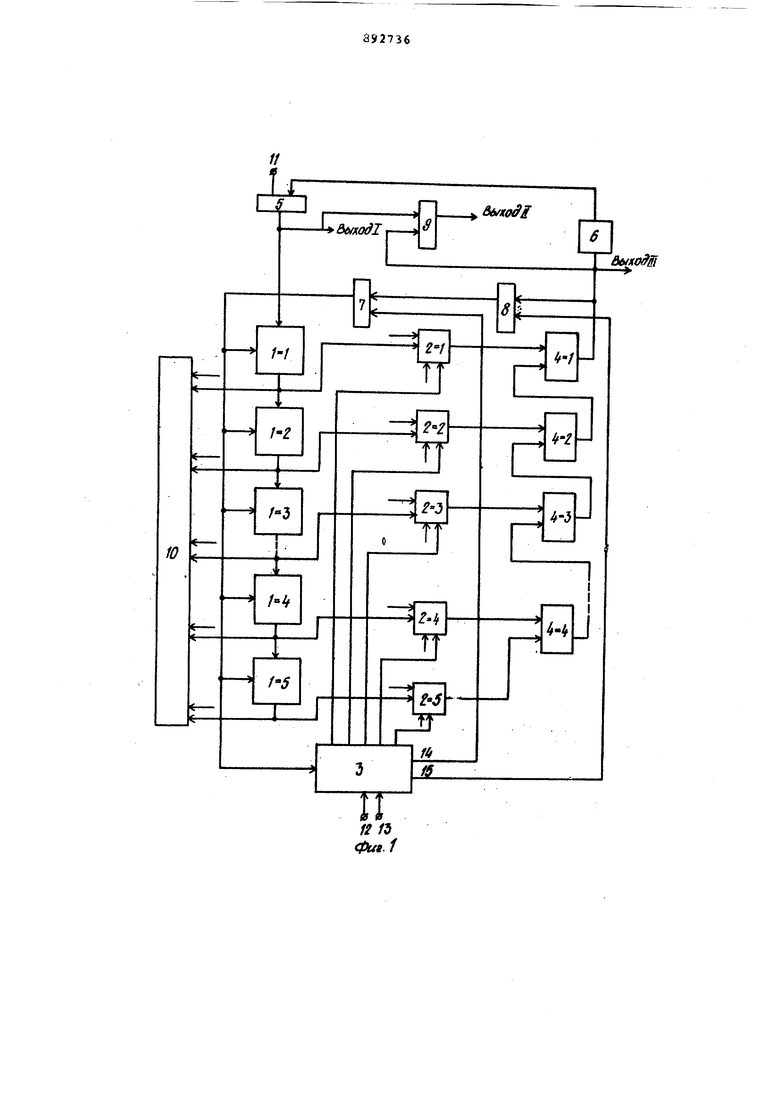

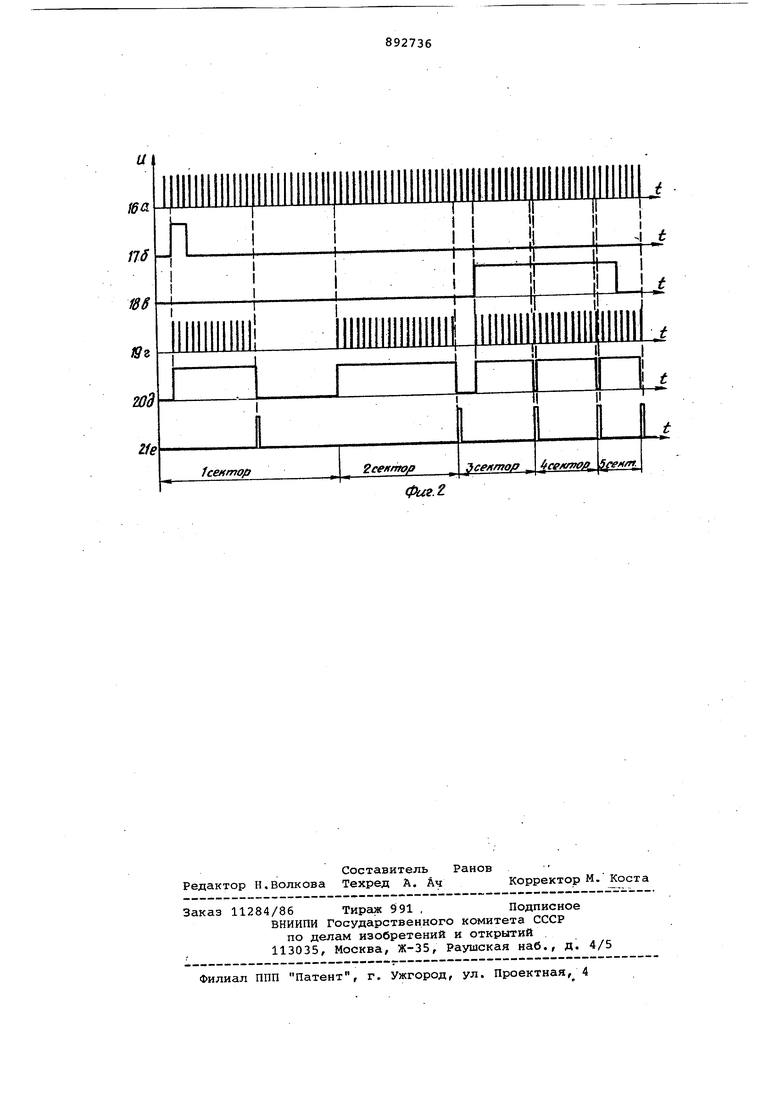

Указанная цель достигается тем, что в счетное устройство, содержащее входную шину, П последовательно соединенных счетных декад, П элементов 30 сравнения, первые входы которых сое цйнены с выходами соответствующих V учетных декад, задающий блок, инфор мационные выходы которого соединены со вторыми входами соответствующих элементов сравнения, П-1 декадных элементов И, первые входы которых соединены с выходами соответствукмцию элементо.в сравнения, введены блок индикации, два элемента И, триггер, элемент tffi и элемент ИЛИ, выход кото рого соединен со входами сброса счет ных декад и с первым входом задаюадего блока, первый и второй управлзйощие выходы которого соединены соответственно с первыми входами, элемента ИЛИ и первого элемента И, ВТОЕЮЙ вход которого соединен с выходом первого декадного элемента И, со входом элемента НЕ и с первым входом триггера, второй вход которого соединен со счетным входом первой счетной декады и с выходом второго элемента И, первый и второй входа которого соединены соответственно со входной шиной и с выходом элемента HEf второй вход элемента ИЛИ соединен с выходом первого элемента И, выход каждого декадного элемента И, кроме первого, соединен со вторым входом предьщущего декадного элемента И, второй вход последнего декадного элемента И соединен с выхо дом последнего элемента сравнения, входы блока индикации соединены с выходами счетных декад, второй и третий входы задающего блока соединены с шинами управления. На фиг, 1 приведена структурная схема счетного устройства; на фиг. 2 - временные диаграммы, пояс;няющие работу счетного устройства. Устройство содержит последовател но соединенные счетные декады элементы 2 1-2-5 сравнения, задающий блок 3, декадные элементы И элемент И 5, элемент НЕ б, элементы ИЛИ 7 и И- 8, триггер 9, блок 10 индикации, входную шину 11, шины 12 и 13 управления и выходы 14 и 15 управления задающего блока 3. Выходы счетных декад соединены со входами блока 10 индикации и соединены соответственно с первыми входами элементов сравнения, вторые входы которых соединены с ин.формационными выходами задающего бло ка 3, первый вход которого соединен со входами сброса счетных декад и с выходом элемента ИЛИ 7, первый и второй входы которого соединены соответственно с выходом 14 управ ления задающего блока 3 и с выходом элемента И 8, первый и второй входы которого соединены соответственно с выходом 15 управления задающего блока 3 и с выходом декадного элемента И , выход которого соединен со входом элемента НЕ б и с первым триггера 9, второй входкоторого соединен со счетным входом счетной декады и с выходом элемента И 5, первый и второй входы которого соединены соответственно со входной шиной 11 и с выходом элемента НЕ 6, выходы элементов сравнения соединены соответственно с первыми входами декадных элементов И 4-1-4 4, вторые входы которых соединены соответственно с выходами декадных элементов и 4в2-4 4, второй вход последнего из которых соединен с выходом элемента сравнения, второй и третий входы задающего блока 3 соединены соответстьенно с шинами 12 и 13 управления. Временные диаграммы, поясняющие работу устройства (фиг. 2), включают временную диагЕ)амму 16 сигналов на входной шине 11, диаграмму 17 сигналов на выходе 14 управления задающего блока 3, диаграмму 18 сигналов на выходе 15 управления задающего блока 3, диаграмму 19 сигналов на выходе элемента И 5, диаграмму 20 сигналов на выходе триггера 9, временную диаграмму 21 сигналов на входе элемента НЕ 6. Устройство работает следующим образом. В исходном состоянии с выхода 14 задающего блока 3 поступает запрещающий сигнал, который, проходя че|зез элемент ИЛИ 7, удерживает счетные декады Itrl-lsS в нулевом состоянии. На вход элемента И 5 подают сигналы по входной шине 11 (иг. 2,диаграмма 16), а в задающем блоке 3 устанавливают режим работы устройства по шинам 12 и 13. Далее убирают запрещающий сигнал с выхода 14 задающего блока 3, при этом счетные декады начинают работать. Предположим, что в задающем блоке 3 установлена программа на формирование устройством пачек импульсов с числом импульсов в пачке, превышающим емкость счетных декад 1 1-1-4. Тогда первый же импульс, прошедший через элемент И 5, осуществляет опрокидывание триггера 9, а после отработки счетной декадой 1-5 кода, совпадающего с кодом/ поступающим на вторые эходы элемента сравнения, с выхода последнего поступает разрешающий сигнал на второй вход декадного элемента И . После отработки счетной декадой 1-4 кода, совпадающего с кодом, поступающим с инфо{Я4ационных выходов задающего блока 3 на вторые входы элемента 2«4 сравнения, с выхода последнего поступает разрешающий сигнал на другой вход декадного элемента И 4«4, при этом с выхода последнего, разрешающий сигнал поступает на второй вход следуккдего декадного элемента И и т.д. После отработки счетной декадой 1&1 кода, совпадающего с

кодом, поступающим с информационных BfjixoAOB задающего блока 3 на вторые входы элемента сравнения, с выхода последнего сигнал поступает на первый вход декадного элементна И 4±1, на второй вход которого разрешающий сигнал поступает с выхода декадного элемента И . Далее сигнал с выхода декадного элемента И постует на вход элемента НЕ 6, сигнал с выхода которого запрещает поступление сигналов со входной шины 11 череэ элемент И 5, возвращает триггер 9 в исходное состояние и поступает на первый вход элемента ИЗ.

При этом, в случае, если на второй вход элемента И 8 поступает разрешающий сигнал с выхода 15 эаданиаего блока 3, то этот сигнал, проходя через элемент ИЛИ 7, возвращает всё счетные декады в нулевое состояние и осуществляет стровирование кода установки в задающем блоке 3. После установки счетных декад в нулевое состояние, на входе и выходе декадного элемента И появляется запрещающий сигнал, на выходе элемента НЕ б появляется сигнал, разрешающий прохождение сигналов со входной шины 11 через элемент и 5. С приходом переднего фронта первого импульса, прошедшего через элемент И 5, описанный процесс работы устройства повторяется,

В случае, если на второй вход элемента И 8 поступает запрещающий сигнал, то, после появления разрешающего сигнала с выхода элемента И , последний,через элемент НЕ 6, запрещает прохождение сигналов со входной шины 11 через элемент И 5и возвращает триггер 9 в исходное состояние, В этом состоянии устройство находится до тех пор, пока на второй вход элемента И 8 не поступит разрешанииий сигнал с выхода 15 задающего блока 3, при этом в блоке 10 индикации высвечивается число, соответствующее числу импульсов в пачке, сформированной на выходе элемента И5. На выходе триггера 9 формируется временной интервёш, соответствующий времени с момента поступления переднего фронта первого импульса, прошедшего через 31лемент И 5 до момента прихода переднего фронта импульса с выхода декадного элемента И 4е1. На входе элемента НЕ б формируется одиночный импульс, который появляется в момент прихода переднего фронта импульса с выхода декадного элемента И 4. ,

В первом и втором секторах временных диаграмм (фиг, 2) показана работа устройства в режиме одиночного запуска, а в третьем-пятом - работа устройства в непрерывном режиме с автоматическим изменением кода установки, поступающим с информационных выходов задающего блока 3 на входы элементов 2- 1-2«:5 сравнения.

Элементы сравнения и деКсщные элементы с соответствующими связями выполняют функцию ЦИФРОВО1-О компаратора, поэтйму в предлагаемом устройстве цифровой компаратор может быть реализова.н любым другим известным способом.

0

Формула изобретения

Счетное устройство, содержащее

5 входную шину, П последовательно соединенных счетных декад, П элементов сравнения, первые входы которых соединены с выходами соответствующих счетных декад, задающий блок, информационные выходы которого сое0динены со вторыми входами соответствующих элементов сравнения, П-1 декадных элементов И, первые входы которых соединены с выходами соответствуйщих элементов сравнения, от5личающееся тем, что, с Целью расширения функциональных возможностей, в него введены бдок индикации, два элемента И, триггер, элемент НЕ и элемент ИЛИ, выход ко0торого соединен со входгми сброса счетных декад и с первым входом задающего блока, первый и второй управляющие выходы которого соединены соответственно с первыми входами эле5мента ИЛИ и первого элемента И,второй вход которого соединен с выходом первого декадного элемента И,со входом элемента НЕ и с первым входом триггера, второй вход которого соединен со счетным входом первой

0 счетной декады и с выходом второго элемента И, первый и второй входы которого соединены соответственно со входной шиной и с выходом элемента НЕ, второй вход, элемента ИЛИ соеди5нен с выходом первого элемента И, выход каждого декадного элемента И, кроме первого, соединен со вторым входом предыдущего декадного але.мента И,-второй вход последнего де0кадного элемента И соединен с выходом последнего элемента сравнения, входы блока индикации соединены с выходами счетных декгщ, второй и третий входы задающего блока соеди5нены с шинами управления.

Источники информации, принятые во внимание при экспертизе

1.Авторское Свидетельство СССР 372709, кл. Н 03 К 25/04, 1971.

0

2.Авторское свидетельство СССР 514440, кл. Н 03 К 23/00, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный декадный счетчик импульсов | 1976 |

|

SU603126A1 |

| Устройство для измерения отношения частот | 1988 |

|

SU1661664A1 |

| Делитель частоты с изменяемым коэффициентом деления | 1979 |

|

SU783996A1 |

| Цифроаналоговый измеритель средней частоты | 1991 |

|

SU1775678A1 |

| Устройство для программного счета изделий | 1983 |

|

SU1113824A1 |

| Устройство для формирования импульсных последовательностей | 1977 |

|

SU669478A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1140248A1 |

| Устройство проверки счетчиков | 1982 |

|

SU1051728A1 |

| Счетчик импульсов с визуальной индикацией | 1978 |

|

SU767973A1 |

| Устройство цифровой индикации положения сосуда шахтной подъемной машины | 1989 |

|

SU1745659A1 |

Авторы

Даты

1981-12-23—Публикация

1980-04-16—Подача