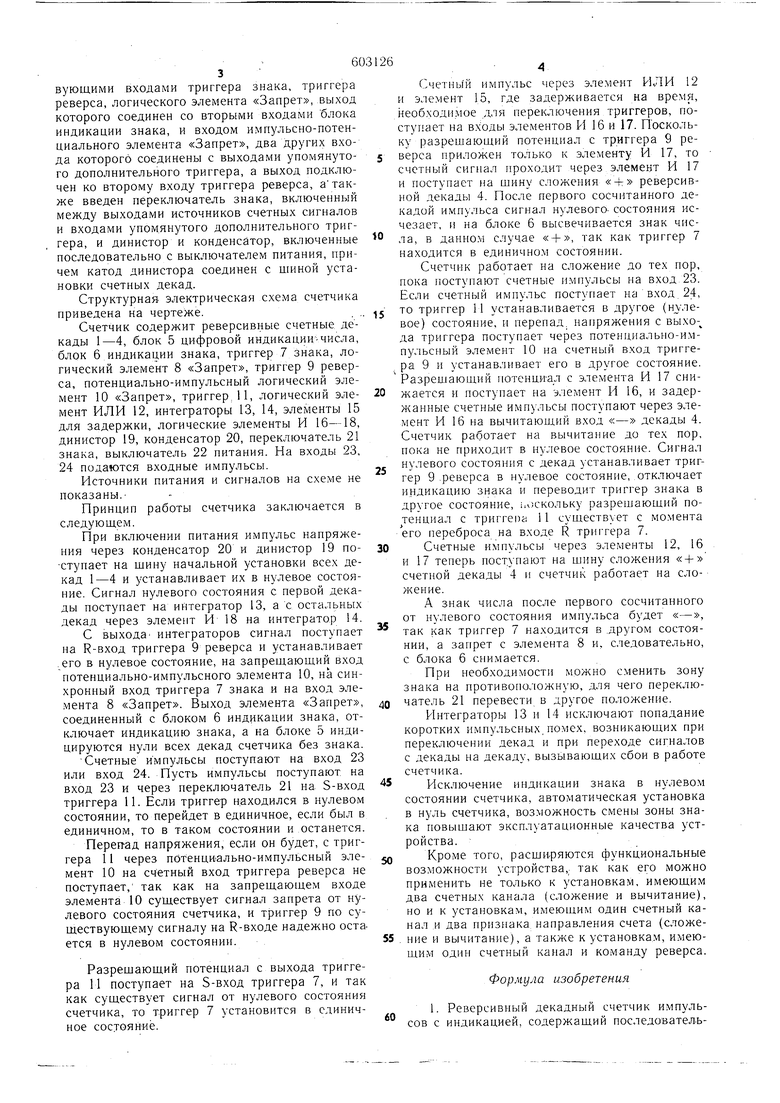

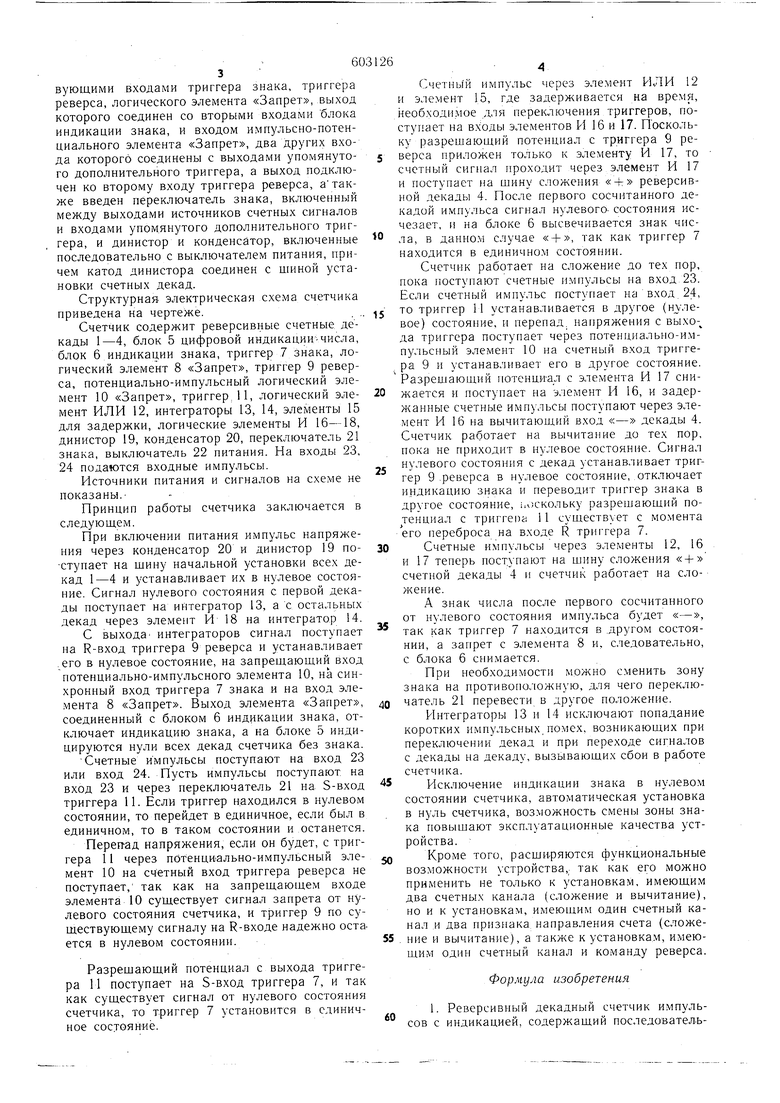

(54) РЕВЕРСИВНЫЙ ДЕКАДНЫЙ СЧЕТЧИК ИМПУЛЬСОВ вующими входами триггера знака, триггера реверса, логического элемента «Запрет, выход которого соединен со вторыми входами блока индикации знака, и входом импульсно-потенциального элемента «Запрет, два других входа которого соединены с выходами упомянутого дополнительного триггера, а выход подключен ко второму входу триггера реверса, атакже введен переключатель знака, включенный между выходами источников счетных сигналов и входами упомянутого дополнительного триггера, и динистор и конденсатор, включенные последовательно с выключателем питания, причем катод динистора соединен с тиной установки счетных декад. Структурная электрическая схема счетчика приведена на чертеже., Счетчик содержит реверсивные счетные декады 1-4, блок 5 цифровой индикации-числа, блок 6 индикации знака, триггер 7 знака, логический элемент 8 «Запрет, триггер 9 реверса, потенциально-импульсный логический элемент 10 «Запрет, триггер J1, логический элемент ИЛИ 12, интеграторы 13, 14, элементы 15 для задержки, логические элементы И 16-18, динистор 19, конденсатор 20, переключатель 21 знака, выключатель 22 питания. На входы 23, 24 подаются входные импульсы. Источники питания и сигналов на схеме не показаны.Принцип работы счетчика заключается в следующем. При включении питания импульс напряжения через конденсатор 20 и динистор 19 поступает на шину начальной установки всех декад 1-4 и устанавливает их в нулевое состояние. Сигнал нулевого состояния с первой декады поступает на интегратор 13, ас остальных декад через элемент И 18 на интегратор 14. С выхода- интеграторов сигнал поступает на R-вход триггера 9 реверса и устанавливает .его в нулевое состояние, на запрещающий вход потенциально-импульсного элемента 10, на синхронный вход триггера 7 знака и на вход эле.мента В «Запрет. Выход элемента «Запрет, соединенный с блоком 6 индикации знака, отключает индикацию знака, а на блоке 5 индицируются нули всех декад счетчика без знака. Счетные импульсы поступают на вход 23 или вход 24. Пусть импульсы поступают на вход 23 и через переключатель 21 на S-вход триггера И. Если триггер находился в нулевом состоянии, то перейдет в единичное, если был в единичном, то в таком состоянии и останется. Переп-ад напряжения, если он будет, с триггера 11 через потенци ально-импульсный элемент 10 на счетный вход триггера реверса не поступает, так как на запрещающем входе элемента 10 существует сигнал запрета от нулевого состояния счетчика, и триггер 9 по существующему сигналу на R-входе надежно остается в нулевом состоянии. Разрещающий потенциал с выхода триггера 11 поступает на S-вход триггера 7, и так как существует сигнал от нулевого состояния счетчика, то триггер 7 установится в единичное состояние. Счетный импульс через элемент ИЛИ 12 и элемент 15, где задерживается на время, необходимое для переключения триггеров, поступает на входы элементов И 16 и 17. Поскольку разрешающий потенциал с триггера 9 реверса приложен только к элементу И 17, то счетный сигнал проходит через элемент И 17 и поступает на тину сложе П1я «-ь реверсивной декады 4. После первого сосчитанного декадой импульса сигнал нулевого- состояния исчезает, и на блоке 6 высвечивается знак числа, в данном случае « + , так как триггер 7 находится в единичном состоянии. Счетчик работает на сложение до тех пор, пока поступают счетные импульсы на вход 23. Если счетный импульс поступает на вход 24, то триггер 11 устанавливается в другое (нулевое) состояние, и перепад, напряжения с выхода триггера поступает через потенциальпо-импульспый элемент 10 на счетный вход триггера 9 и устанавливает его в другое состояние. Разрешающий потенци-ал с элемента И 17 снижается и поступает на элемент И 16, и задержанные счетные импульсы поступают через элемент И 16 на вычитаюихий вход «- декады 4. Счетчик работает на вычитание до тех пор, пока не приходит в нулевое состояние. Сигнал нулевого состояния с декад устанавливает триггер 9 .реверса в нулевое состояние, отключает индикацию знака и переводит триггер знака в другое состояние, поскольку разрешающий по енциал с триггера 11 существует с мо.мента его переброса на входе R триггера 7. Счетные импульсы через элементы 12, 16 и 17 теперь поступают на шину сложения «-ь счетной декады 4 и счетчик работает на сложение. А знак числа после первого сосчитанного от нулевого состояния импульса будет «-, так как триггер 7 находится в .другом состоянии, а запрет с эле.мента 8 и, следовательно, с блока 6 спи.мается. При необходимости можно сменить зону знака на противоположную, для чего переключатель 21 перевести в другое положение. Интеграторы 13 и 14 исключают попадание коротких импульсных, помех, возникающих при переключении декад и при переходе сигналов с декады на декаду, вызьшающих сбои в работе счетчика. Исключение индикации знака в нулевом состоянии счетчика, автоматическая установка в нуль счетчика, возможность смены зоны знака повыщают эксплуатационные качества устройства. Кроме того, расши-ряются функциональные возможности устройства, так как его можно применить не только к установкам, имеющим два счетных канала (сложение и вычитание), но и к установкам, имеющим один счетный канал и два признака направления счета (сложение и вычитание), а также к установкам, имеющим один счетный канал и команду реверса. Формула изобретения 1. Реверсивный декадный счетчик импульсов с индикацией, содержащий последовательно соединенные счетные декады, триггер реверса, выходы которого через логические элементы И соединены со входами первой счетной декады, триггер знака, выходы которого соединены с первыми входами блока индикации знака, а входы подключены к выходам дополнительного триггера, входы которого подключены к источникам счетных сигналов, логический элемент И, входы которого соединены с входами дополнительного триггера, а выход через элемент для задержки импульсов соединен со вторыми входами упомянутых логических элементов И, и блок индикации числа, входь; которого соединены с соответствующими выходами счетных декад, отличающийся тем, что, с целью повышения надежности и точности индикации, в него введены логический элемент «Запрет, импульсно-потенциальный логический элемент «Запрет, два интегратора и дополнительный логический элемент И, причем входы дополнительного логического элемента И соединены с выходами счетных декад, кроме первой, его выход и выход первой счетной декады через интеграторы соединены с соответствующими входами триггера знака, триггера реверса, логического элемента «Запрет, выход которого соединен со вторыми входами блока индикации знака, и входом импульсно-потенциального элемента «Запрет, два других входа которого соединены с выходами упомянутого дополнительного триггера, а выход подключен ко второму входу триггера реверса.

2.Счетчик по п. 1, отличающийся тем, что, с целью смены знака счета, в него введен переключатель знака, включенный между выходами источников счетных сигналов и входами упомянутого дополнительного триггера.

3.Счетчик по пп. 1, 2, отличающийся тем, что, с целью автоматической установки счетчика в нулевое положение при включении питания, в него введены динистор и конденсатор, включенные последовательн6 с выключателем питания, причем катод динистора соединен с щиной установки счетных декад.

Источники информации, принятые во внимание при экспертизе:

0 1. Авторское свидетельство СССР № 463235, кл. Н 03 К 29/00, 1974.

2. Авторское свидетельство СССР № 265589, кл. G 01 М 3/00, 1963.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегратор с контролем | 1975 |

|

SU540269A1 |

| Интегратор | 1978 |

|

SU748438A1 |

| Измеритель относительных значенийРАзНОСТи СКОРОСТЕй | 1976 |

|

SU815631A2 |

| РЕВЕРСИВНЫЙ СЧЕТЧИК С ИНДИКАЦИЕЙ | 1966 |

|

SU215621A1 |

| ЦИФРОВОЙ КОМПЕНСАТОР ПЕРЕМЕННОГО ТОКА С ДИСКРЕТНЫМ УРАВНОВЕШИВАНИЕМ | 1967 |

|

SU197751A1 |

| Фазоимпульсный реверсивный счетчик | 1981 |

|

SU951714A1 |

| РЕВЕРСИВНАЯ ПЕРЕСЧЕТНАЯ ДЕКАДА | 1969 |

|

SU238249A1 |

| Устройство для позиционного управления | 1983 |

|

SU1124257A1 |

| ЦИФРОВОЙ СЛЕДЯЩИЙ КОМПЕНСАТОР | 1967 |

|

SU205138A1 |

| Цифровой измеритель относительных значений разности скоростей | 1982 |

|

SU1064201A2 |

Авторы

Даты

1978-04-15—Публикация

1976-03-29—Подача