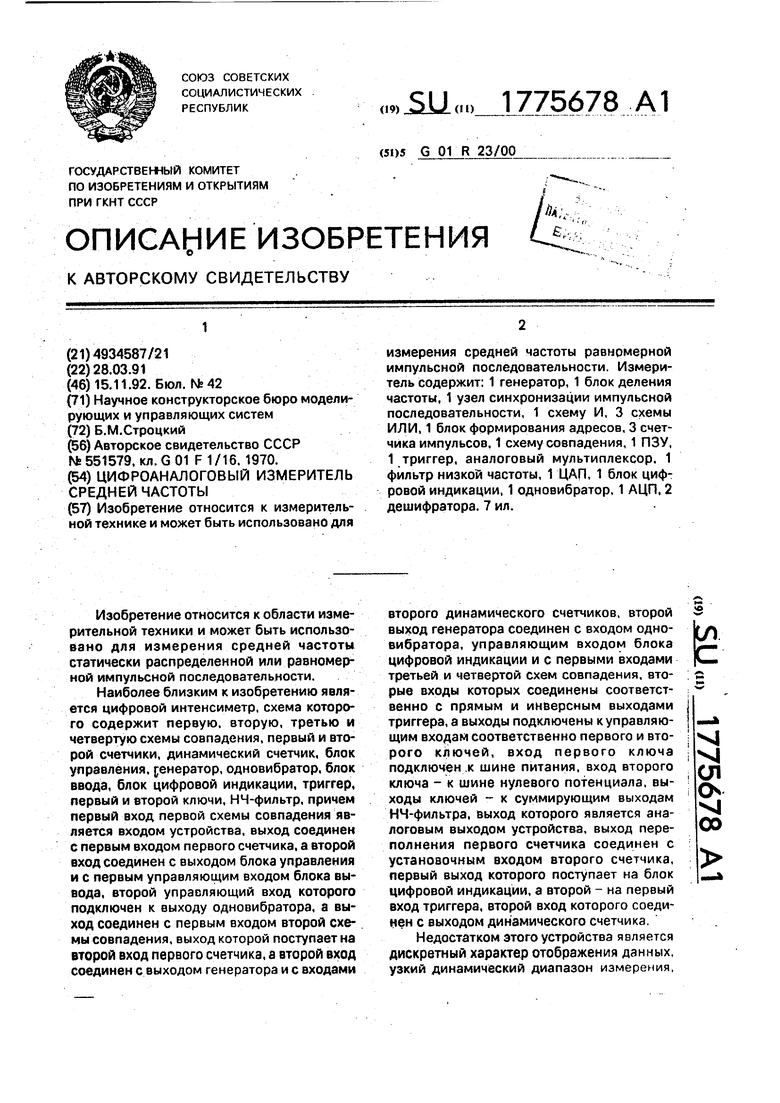

Изобретение относится к области измерительной техники и может быть использовано для измерения средней частоты статически распределенной или равномерной импульсной последовательности.

Наиболее близким к изобретению является цифровой интенсиметр, схема которого содержит первую, вторую, третью и четвертую схемы совпадения, первый и второй счетчики, динамический счетчик, блок управления, генератор, одновибратор, блок ввода, блок цифровой индикации, триггер, первый и второй ключи, Н Ч-фильтр, причем первый вход первой схемы совпадения является входом устройства, выход соединен с первым входом первого счетчика, а второй вход соединен с выходом блока управления и с первым управляющим входом блока вывода, второй управляющий вход которого подключен к выходу одновибратора, а выход соединен с первым входом второй схемы совпадения, выход которой поступает на второй вход первого счетчика, а второй вход соединен с выходом генератора и с входами

второго динамического счетчиков, второй выход генератора соединен с входом одно- вибратора, управляющим входом блока цифровой индикации и с первыми входами третьей и четвертой схем совпадения, вторые входы которых соединены соответственно с прямым и инверсным выходами триггера, а выходы подключены к управляющим входам соответственно первого и второго ключей, вход первого ключа подключен к шине питания, вход второго ключа - к шине нулевого потенциала, выходы ключей - к суммирующим выходам НЧ-фильтра, выход которого является аналоговым выходом устройства, выход переполнения первого счетчика соединен с установочным входом второго счетчика, первый выход которого поступает на блок цифровой индикации, а второй - на первый вход триггера, второй вход которого соединен с выходом динамического счетчика.

Недостатком этого устройства является дискретный характер отображения данных, узкий динамический диапазон измерения,

у

Ј

VI

Я

Ov xj 00

большая погрешность аналогового выхода и длительный характер установления переходных процессов при динамических измерениях из-за больших значений постоянной времени основного счетчика и НЧ4фильтра.

Целью изобретения является повышение быстродействия и расширение динамического диапазона намерений устройства.

Указанная цель достигается тем, что в устройство, содержаа ее первый и второй счетчики, генератор, триггер, блок цифровой индикации, схему совпадения и одно- вибратор дополнительно заедены блок деления частоты, цифроаналоговый преобразователь, узел синхронизации импульсной последовательности, постоянное запоминающее устройство, первая и вторая схемы ИЛИ, многовходовая схема И, первый аналоговый мультиплексор, аналого-цифровой преобразователь, кодоуправ- ляемый фильтр низкой частоты и блок формирования адресов, в состав которого входят третья схема ИЛИ, третий счетчик, первый и второй дешифраторы, причем первый вход генератора соединен с входом блока деления частоты, а второй - с первым входом узла синхронизации импульсной последовательности, второй вход которогоо является входом устройства, третий соединен с выходом многовходовой схемы И, с первым входом первой схемы ИЛИ и с первым входом блока формирования адресов, а выход подключен к суммирующему входу первого счетчика, вычитающий вход которого соединен с выходом схемы совпадения и установочным входом второго счетчика, вход параллельной записи данных - с выходом постоянного запоминающего устройства, синхровход - с выходом первой схемы ИЛИ, параллельный выход данных - с входами многовходсвой схемы И, а старший разряд параллельного выхода данных подключен к первому входу схемы совпадения и к входу данных триггера, выход которого соединен с управляющим входом первого аналогового мультиплексора, выход которого подключен к входу кодоуп- равляемого фильтра низкой частоты, второй информационный вход - к шине общего потенциала, первый информационный вход - к выходу цифроаналогового преобразователя, вход которого соединен с вторым адресным выходом блока формирования адресов и с вторым адресным входом блока деления частоты, первый адресный вход которого соединен с адресным входом кодоуправля- емого фильтра низкой частоты, входом управления запятой блока цифровой

индикации и с первым адресным выходом блока формирования адресов, а выход подключен к второму входу схемы совпадения к синхровходу триггера и к счетному входу

второго счетчика, выход переполнения которого соединен с первым входом второй схемы ИЛИ, агорой вход которой является установочным входом устройства, третий соединен с выходом начала поиска поддиа0 назона блока формирования адресов, а выход подключен к установочному входу блока формирования адресов и, через одновибра- тор, - ко второму входу первой схемы ИЛИ и к установочному входу кодоуправляемого

5 фильтра низкой частоты, выход которого является аналоговым выходом устройства и через аналого-цифровой преобразователь соединен с информационным входом блока цифровой индикации и с входом данных

0 блока формирования адресов, в структуре которого вход данных подключен к входу первого дешифратора, третий выход которого является выходом начала поиска поддиапазона блока, второй - вторым

5 адресным выходом блока, а первый поступает на второй вход третьей схемы ИЛИ, первый вход которой является первым входом блока, а выход подключен k счетному входу третьего счетчика, установочный вход

0 которого является установочным входом блока, а параллельный выход соединен с входами второго дешифратора, выход которого является первым адресным выходом блока формирования адресов.

5 Существенными отличительными признаками заявляемого устройства в сравнении с прототипом являются введенные в его состав блок деления частоты, цифроаналоговый преобразователь, узел синхро0 низации импульсной последовательности, постоянное запоминающее устройство, первая и вторая схемы ИЛИ, многовходовая схема И, первый аналоговый мультиплексор, аналого-цифровой преоб5 разователь, кодоуправляемый фильтр низ- кой частоты и блок формирования адресов, в состав которого входят третья схема ИЛИ, третий счетчик, первый и второй дешифраторы. Наличие отличительных при0 знаков обуславливает соответствие заявляемого технического решения критерию новизна, т.к. использование этих эле- ментов совместно с их связями дает положительный эфэфект - повышение быс5 тродействия и расширение динамического диапазона измерений.

Заявляемое техническое решение соответствует также критерию существенные отличия поскольку не обнаружено решений с признаками сходными с признаками, отличающими заявляемое техническое решение от прототипа.

Заявляемому техническому решению измерителя средней частоты предшествуют следующие методические предпосылки.

1.Методическая погрешность измерения среднего случайного процесса определяется постоянной времени интегратора, которая быстро возрастает с ужесточением требований по точности.

2.Измерение среднего значения импульсной последовательности в широком динамическом диапазоне требует для улучшения динамических характеристик изменения постоянной времени интегратора оптимальным образом, причем критерием оптимал ьности я вл яется со бл юдение требо- ваний по величине методической погрешности процедуры измерения.

3.Разработка измерителей среднего значения с широким динамическим диапазоном и близким к оптимальному значению постоянной времени интегратора требует больших аппаратных затрат кзк при аналоговой, так и при цифровой реализации.

4.Одной из основных характеристик систем следя щего ти п а я вл яется ее pea кция на внешнее ступенчатое воздействие, поэтому в состав передаточной функции системы должны быть введены звенья дифференцирования сигнала.

5.Указанные в предыдущих пунктах ограничивающие факторы для измерения среднего значения случайной импульсной последовательности создают предпосылки для оптимальной реализации на базе аналого-цифровых схемных решений, которые позволяют при ограниченных аппаратных затратах изменять постоянную времени интегрирования с высоким уровнем дискретности, ввести первую производную в закон регулирования, получить итоговую информацию как в аналоговом, так и в дискретном виде, добиться умеренных аппаратных затрат для измерителей с низким значением методической погрешности.

Предварительный анализ ограничивающих факторов для измерителей среднего значения частоты позволяет перейти к описанию работы заявляемого устройства.

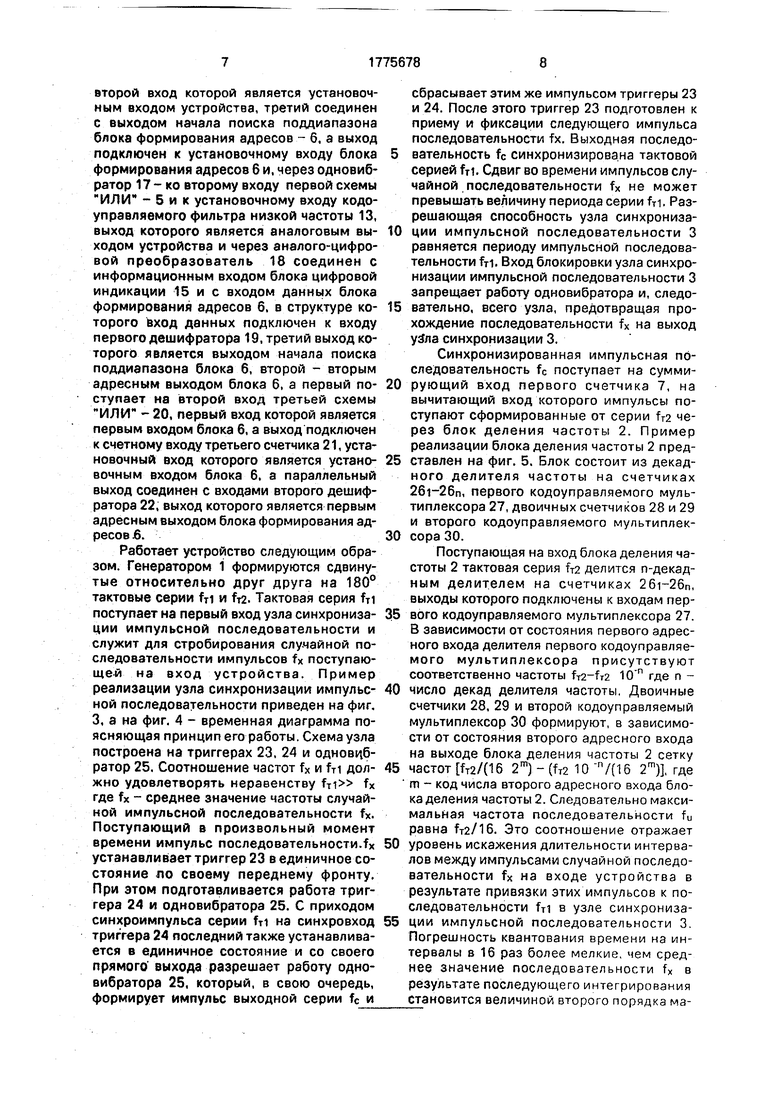

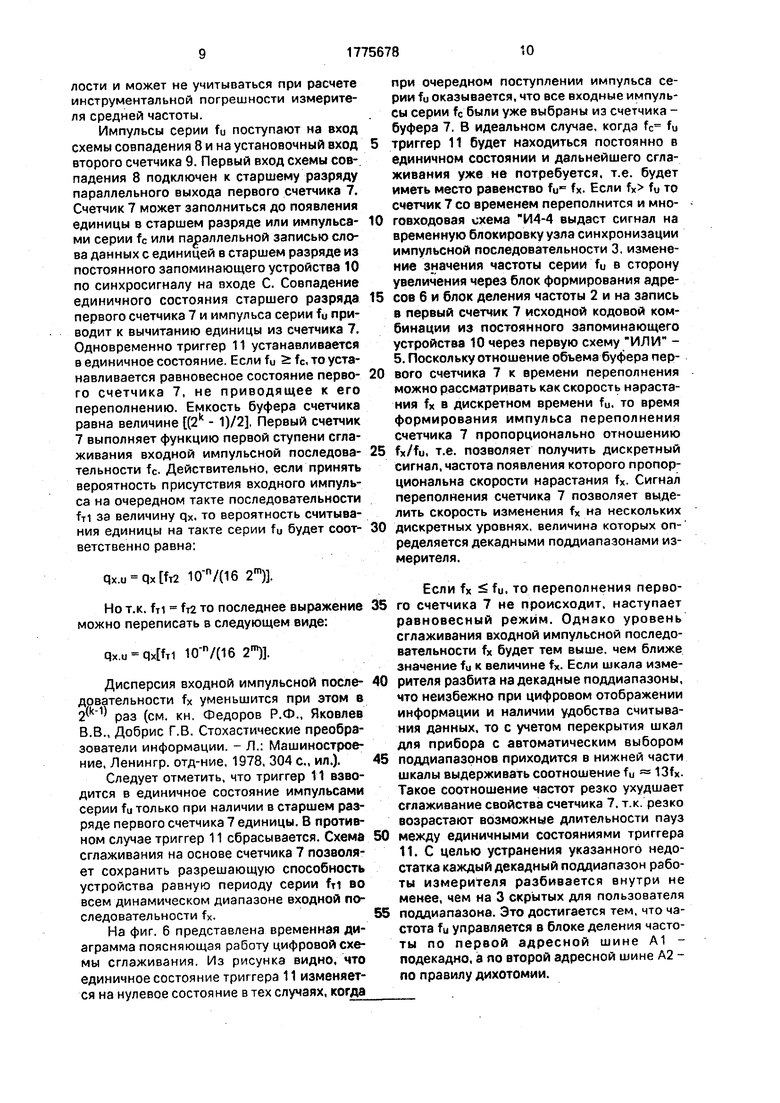

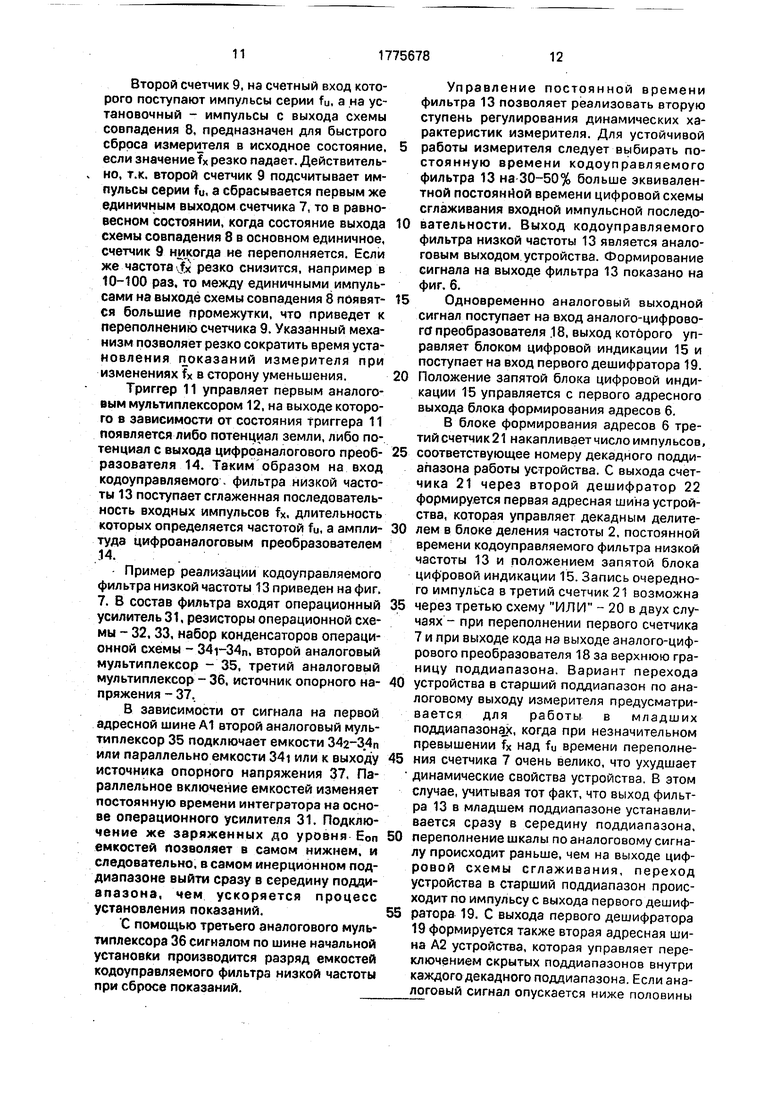

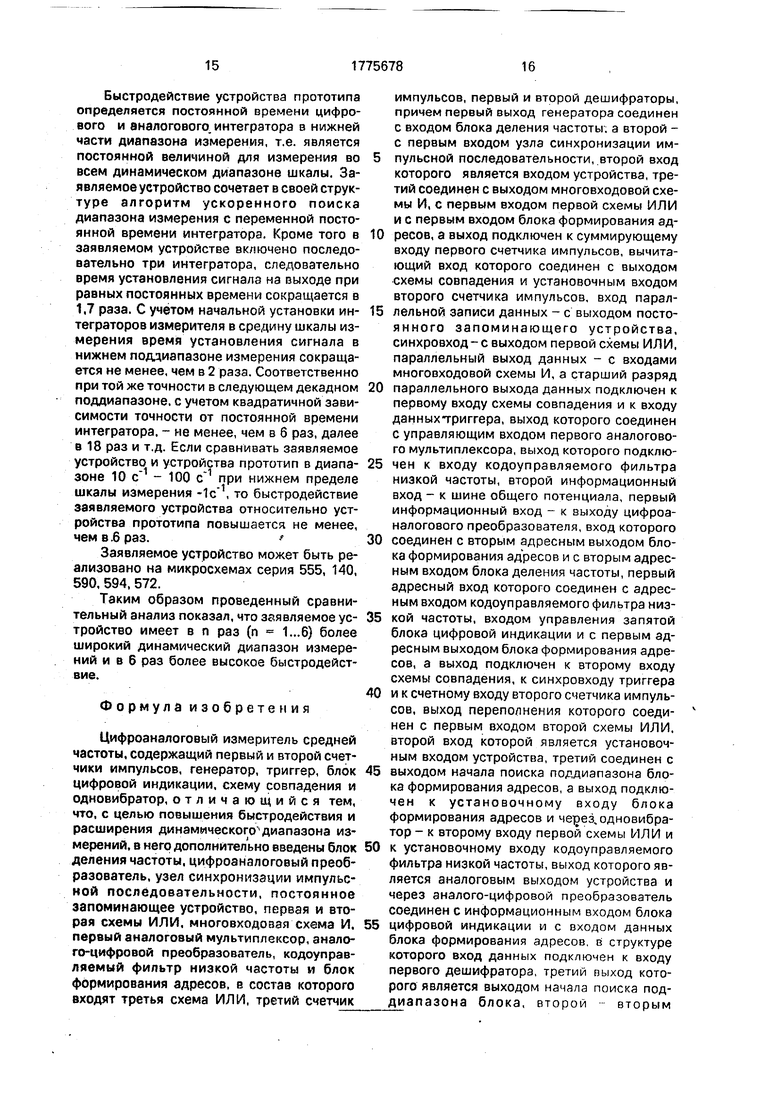

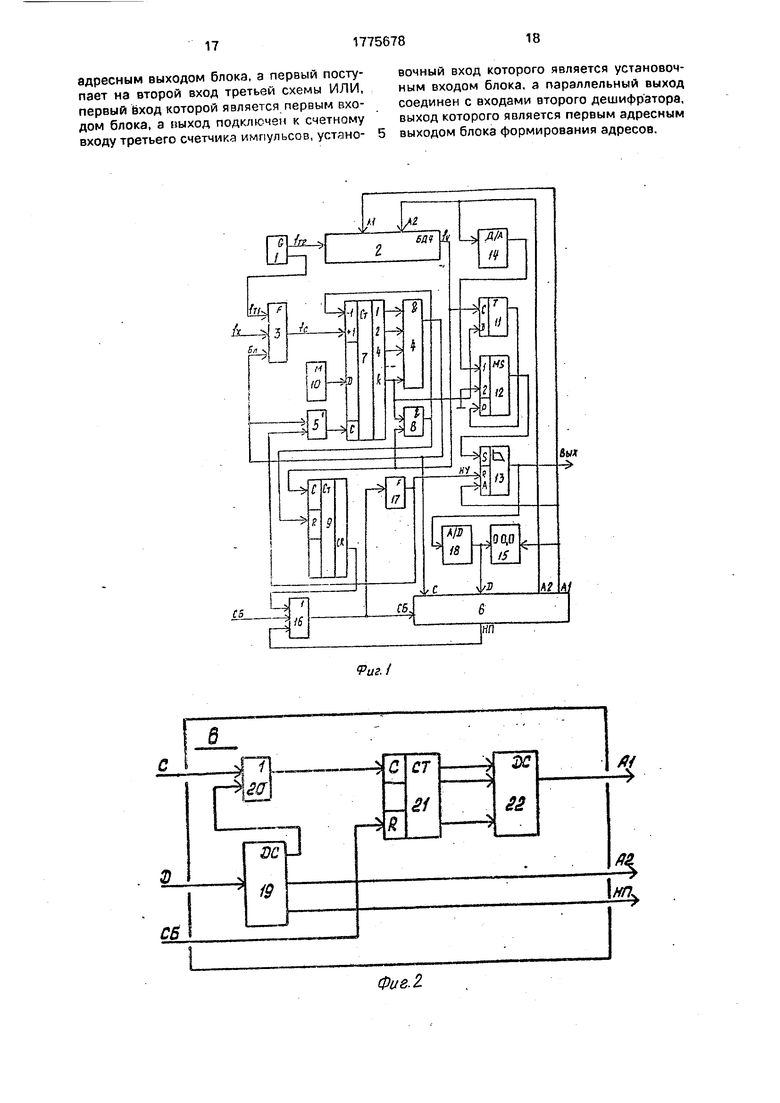

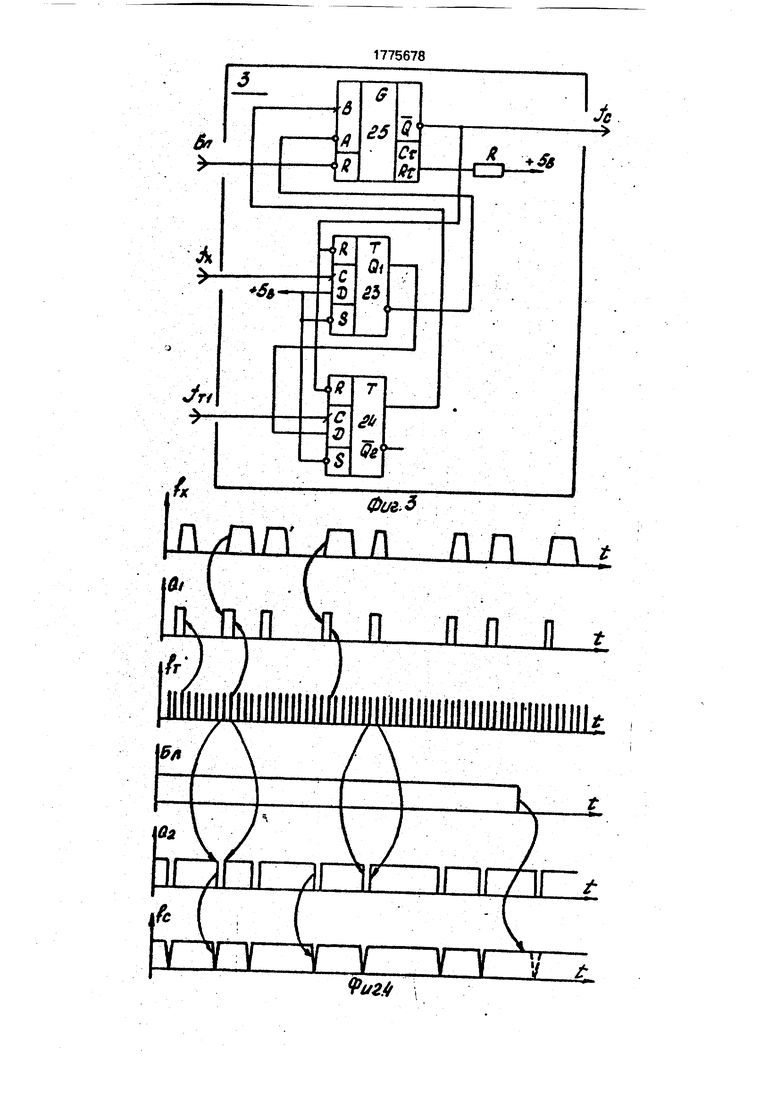

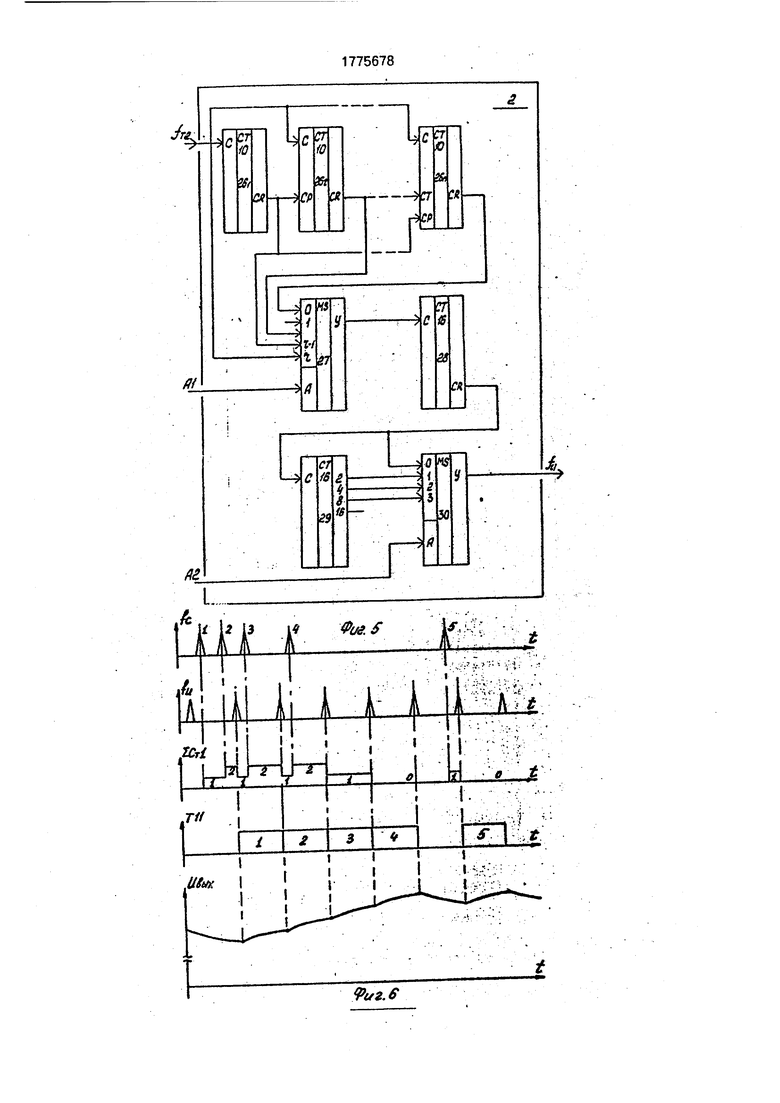

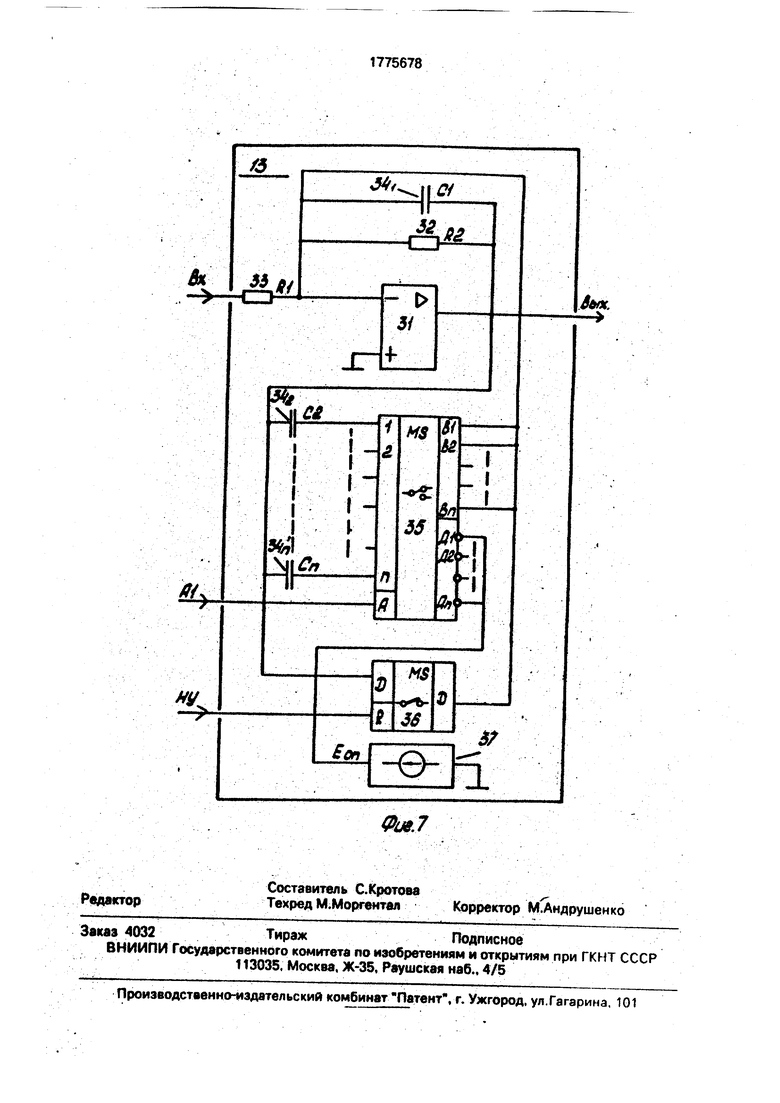

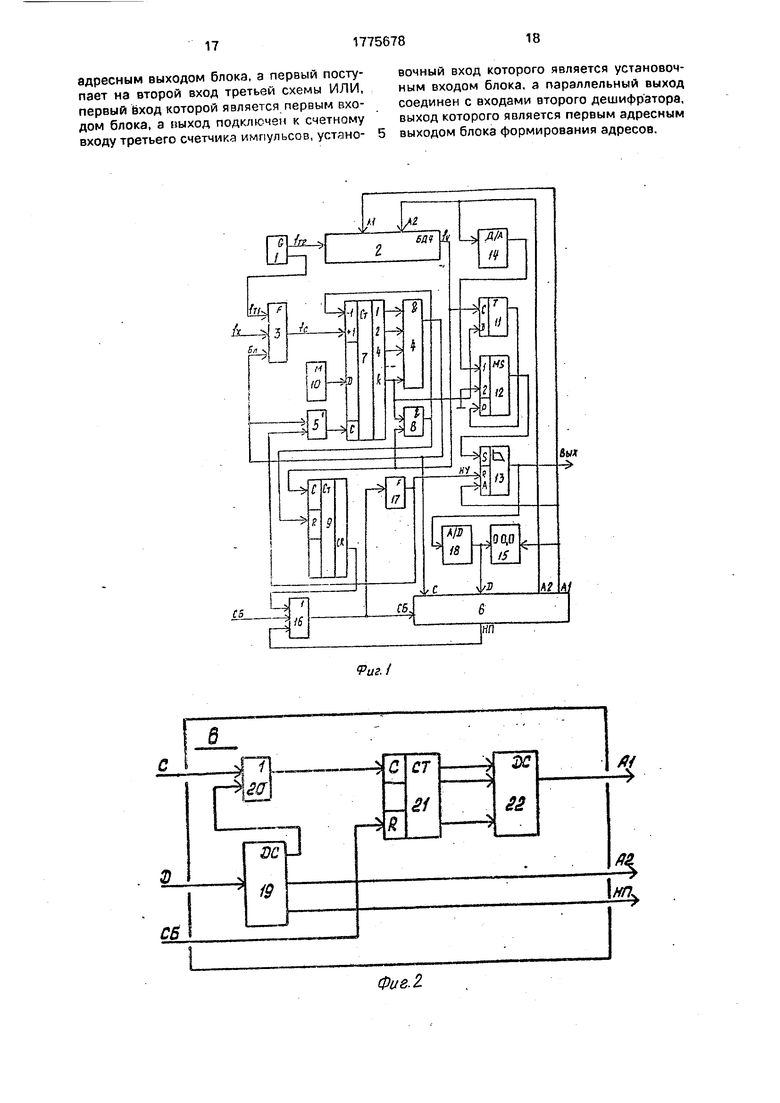

На фиг. 1 и фиг. 2 представлена схема заявляемого устройства, на фиг. 3 - пример схемной реализации узла синхронизации импульсной последовательности, а на фиг. 4 - временная диаграмма, поясняющая принцип его работы, на фиг. 5 и фиг. 7 - примеры схемной реализации соответственно блока деления частоты и кодоуправляемого фильтра низкой частоты, на фиг. 6

- временная диаграмма работы цифровой схемы сглаживания.

В состав устройства входят генератор 1, блок деления частоты 2, узел синхрониза5 ции импульсной последовательности 3. многовходовая схема И 4, первая схема ИЛИ 5. блок формирования адресов 6, первый счетчик 7, схема совпадения 8, второй счетчик 9, постоянное запоминающее

0 устройство 10, триггер 11, первый аналоговый мультиплексор 12, кодоуправляемый фильтр низкой частоты 13, цифроаналого- вый преобразователь 14, блок цифровой индикации 15, вторая схема ИЛИ 16,

5 одновибратор 17, аналого-цифровой преобразователь 18, первый дешифратор 19, третья схема ИЛИ 20. третий счетчик 21 и второй дешифратор 22.

Первый выход генератора 1 соединен с

0 входом блока деления частоты 2, а второй - с первым входом узла синхронизации импульсной последовательности 3, второй вход которой является входом устройства, третий соединен с выходом многовходовой

5 схемы И - 4, с первым входом первой схемы ИЛИ - 5 и с первым входом блока формирования адресов б, а выход подключен к суммирующему входу первого счетчика 7. вычитающий вход которого соединен с

0 выходом схемы совпадения 8 и установочным входом второго счетчика 9, вход параллельной записи данных - с выходом постоянного запоминающего устройства 10, синхровход - с выходом первой схемы

5 ИЛИ - 5, параллельный выход данных - с входами многовходовой схемы И - 4, а старший разряд параллельного выхода данных подключен к первому входу схемы совпадения 8 и к входу данных триггера 11,

0 выход которого соединен с управляющим входом первого аналогового мультиплексора 12, выход которого подключен к входу кодоуправляемого фильтра низкой частоты 13, второй информационный вход к шине

5 общего потенциала, первый информационный вход - к выходу цифроаналогового преобразователя 14, вход которого соединен с вторым адресным выходом блока формирования адресов бис вторым адресным вхо0 дом блока деления частоты- 2, первый адресный вход которого соединен с адресным входом кодоуправляемого фильтра низкой частоты 13, входом управления запятой блока цифровой индикации 15 и с первым

5 адресным выходом блока формирования адресов 6, а выход подключен к второму входу схемы совпадения 8, к синхровходу триггера 11 и к счетному входу второго счетчика 9, выход переполнения которого соединен с

первым входом второй схемы ИЛИ -- 16,

второй вход которой является установочным входом устройства, третий соединен с выходом начала поиска поддиапазона блока формирования адресов - 6, а выход подключен к установочному входу блока формирования адресов 6 и. через одновиб- ратор 17 - ко второму входу первой схемы ИЛИ - 5 и к установочному входу кодо- управляемого фильтра низкой частоты 13, выход которого является аналоговым вы- ходом устройства и через аналого-цифровой преобразователь 18 соединен с информационным входом блока цифровой индикации 15 и с входом данных блока формирования адресов б, в структуре ко- торого вход данных подключен к входу первого дешифратора 19, третий выход которого является выходом начала поиска поддиапазона блока 6, второй - вторым адресным выходом блока 6, а первый по- ступает на второй вход третьей схемы ИЛИ - 20, первый вход которой является первым входом блока 6, а выход подключен к счетному входу третьего счетчика 21, установочный вход которого является устано- вочным входом блока 6, а параллельный выход соединен с входами второго дешифратора 22, выход которого является первым адресным выходом блока формирования адресов .6,

Работает устройство следующим образом. Генератором 1 формируются сдвинутые относительно друг друга на 180° тактовые серии и fa. Тактовая серия fTi поступает на первый вход узла синхрониза- ции импульсной последовательности и служит для стробирования случайной последовательности импульсов fx поступающей на вход устройства. Пример реализации узла синхронизации импульс- ной последовательности приведен на фиг. 3, а на фиг. 4 - временная диаграмма поясняющая принцип его работы. Схема узла построена на триггерах 23, 24 и однови.6- ратор 25. Соотношение частот fx и fri дол- жно удовлетворять неравенству fri fx где fx - среднее значение частоты случайной импульсной последовательности fx. Поступающий в произвольный момент времени импульс последовательности.fx устанавливает триггер 23 в единичное состояние ло своему переднему фронту. При этом подготавливается работа триггера 24 и одновибратора 25. С приходом синхроимпульса серии fri на синхровход триггера 24 последний также устанавливается в единичное состояние и со своего прямого выхода разрешает работу одно- вибратора 25, который, в свою очередь, формирует импульс выходной серии fc и

сбрасывает этим же импульсом триггеры 23 и 24. После этого триггер 23 подготовлен к приему и фиксации следующего импульса последовательности fx. Выходная последовательность fc синхронизирована тактовой серией tVi. Сдвиг во времени импульсов случайной последовательности fx не может превышать величину периода серии fTi. Разрешающая способность узла синхронизации импульсной последовательности 3 равняется периоду импульсной последовательности tYi. Вход блокировки узла синхронизации импульсной последовательности 3 запрещает работу одновибратора и, следовательно, всего узла, предотвращая прохождение последовательности fx на выход синхронизации 3.

Синхронизированная импульсная последовательность fc поступает на суммирующий вход первого счетчика 7, на вычитающий вход которого импульсы поступают сформированные от серии fT2 через блок деления частоты 2. Пример реализации блока деления частоты 2 представлен на фиг. 5. Блок состоит из декадного делителя частоты на счетчиках 26i-26n, первого кодоуправляемого мультиплексора 27, двоичных счетчиков 28 и 29 и второго кодоуправляемого мультиплексора 30.

Поступающая на вход блока деления частоты 2 тактовая серия fa делится п-декад- ным делителем на счетчиках 26i-26n, выходы которого подключены к входам первого кодоуправляемого мультиплексора 27. В зависимости от состояния первого адресного входа делителя первого кодоуправляемого мультиплексора присутствуют соответственно частоты fa-fa где п - число декад делителя частоты. Двоичные счетчики 28, 29 и второй кодоуправляемый мультиплексор 30 формируют, в зависимости от состояния второго адресного входа на выходе блока деления частоты 2 сетку частот fr2/(16 2m) - (тт2 10 (16 2m), где т - код числа второго адресного входа блока деления частоты 2. Следовательно максимальная частота последовательности fu равна fr2/16. Это соотношение отражает уровень искажения длительности интервалов между импульсами случайной последовательности fx на входе устройства в результате привязки этих импульсов к последовательности fri в узле синхронизации импульсной последовательности 3. Погрешность квантования времени на интервалы в 16 раз более мелкие, чем среднее значение последовательности fx в результате последующего интегрирования становится величиной второго порядка малости и может не учитываться при расчете инструментальной погрешности измерителя средней частоты.

Импульсы серии fu поступают на вход схемы совпадения 8 и на установочный вход второго счетчика 9. Первый вход схемы совпадения 8 подключен к старшему разряду параллельного выхода первого счетчика 7. Счетчик 7 может заполниться до появления единицы в старшем разряде или импульса- ми серии fc или параллельной записью слова данных с единицей в старшем разряде из постоянного запоминающего устройства 10 по синхросигналу на входе С. Совпадение единичного состояния старшего разряда первого счетчика 7 и импульса серии fu приводит к вычитанию единицы из счетчика 7. Одновременно триггер 11 устанавливается в единичное состояние. Если fu fc, то устанавливается равновесное состояние перво- го счетчика 7, не приводящее к его переполнению. Емкость буфера счетчика равна величине (2k - 1)/2, Первый счетчик 7 выполняет функцию первой ступени сглаживания входной импульсной последова- тельности fc. Действительно, если принять вероятность присутствия входного импульса на очередном такте последовательности fri за величину qx. то вероятность считывания единицы на такте серии fu будет соот- ветственно равна:

qx.u 10 п/(16 2m)}.

Но т.к. fri fr2 то последнее выражение можно переписать в следующем виде:

qx.u Ю п/(16 ).

Дисперсия входной импульсной после- довательности fx уменьшится при этом в раз (см. кн. Федоров Р.Ф., Яковлев В.В., Добрис Г.В. Стохастические преобразователи информации. - Л.: Машиностроение, Ленингр. отд-ние, 1978, 304 с., ил.).

Следует отметить, что триггер 11 взводится в единичное состояние импульсами серии fu только при наличии в старшем разряде первого счетчика 7 единицы. В противном случае триггер 11 сбрасывается. Схема сглаживания на основе счетчика 7 позволяет сохранить разрешающую способность устройства равную периоду серии fri во всем динамическом диапазоне входной последовательности fx.

На фиг. 6 представлена временная диаграмма поясняющая работу цифровой схемы сглаживания. Из рисунка видно, что единичное состояние триггера 11 изменяется на нулевое состояние в тех случаях, когда

при очередном поступлении импульса серии fu оказывается, что все входные импульсы серии fc были уже выбраны из счетчика - буфера 7. В идеальном случае, когда fc fu триггер 11 будет находиться постоянно в единичном состоянии и дальнейшего сглаживания уже не потребуется, т.е. будет иметь место равенство fu- fx. Если fx fu то счетчик 7 со временем переполнится и мно- говходовая охема И4-4 выдаст сигнал на временную блокировку узла синхронизации импульсной последовательности 3, изменение значения частоты серии fu в сторону увеличения через блок формирования адресов 6 и блок деления частоты 2 и на запись в первый счетчик 7 исходной кодовой комбинации из постоянного запоминающего устройства 10 через первую схему ИЛИ - 5. Поскольку отношение объема буфера первого счетчика 7 к времени переполнения можно рассматривать как скорость нарастания fx в дискретном времени fu. то время формирования импульса переполнения счетчика 7 пропорционально отношению fx/fu, т.е. позволяет получить дискретный сигнал, частота появления которого пропорциональна скорости нарастания fx. Сигнал переполнения счетчика 7 позволяет выделить скорость изменения fx на нескольких дискретных уровнях, величина которых определяется декадными поддиапазонами измерителя.

Если fx fu. то переполнения первого счетчика 7 не происходит, наступает равновесный режим. Однако уровень сглаживания входной импульсной последовательности fx будет тем выше, чем ближе значение fu к величине fx. Если шкала измерителя разбита на декадные поддиапазоны, что неизбежно при цифровом отображении информации и наличии удобства считывания данных, то с учетом перекрытия шкал для прибора с автоматическим выбором поддиапазонов приходится в нижней части шкалы выдерживать соотношение fu 13fx. Такое соотношение частот резко ухудшает сглаживание свойства счетчика 7. т.к. резко возрастают возможные длительности пауз между единичными состояниями триггера 11. С целью устранения указанного недостатка каждый декадный поддиапазон работы измерителя разбивается внутри не менее, чем на 3 скрытых для пользователя поддиапазона. Это достигается тем, что частота fu управляется в блоке деления частоты по первой адресной шине А1 - подекадно, а ло второй адресной шине А2 - по правилу дихотомии.

Второй счетчик 9, на счетный вход которого поступают импульсы серии fu, а на установочный - импульсы с выхода схемы совпадения 8, предназначен для быстрого сброса измерителя в исходное состояние, если значение 7х резко падает. Действительно, т.к. второй счетчик 9 подсчитывает импульсы серии fu, а сбрасывается первым же единичным выходом счетчика 7, то в равновесном состоянии, когда состояние выхода схемы совпадения 8 в основном единичное, счетчик 9 никогда не переполняется. Если же частота vf.x резко снизится, например в 10-100 раз, то между единичными импульсами на выходе схемы совпадения 8 появятся большие промежутки, что приведет к переполнению счетчика 9. Указанный механизм позволяет резко сократить время уста- новления показаний измерителя при изменениях х в сторону уменьшения.

Триггер 11 управляет первым аналоговым мультиплексором 12, на выходе которого в зависимости от состояния триггера 11 появляется либо потенциал земли, либо потенциал с выхода цифроаналогового преобразователя 14. Таким образом на вход кодоуправляемого - фильтра низкой частоты 13 поступает сглаженная последовательность входных импульсов fx, длительность которых определяется частотой fu, а амплитуда цифроаналоговым преобразователем .14.

- Пример реализации кодоуправляемого фильтра низкой частоты 13 приведен на фиг, 7. В состав фильтра входят операционный усилитель 31, резисторы операционной схемы - 32, 33, набор конденсаторов операционной схемы - 34i-34n. второй аналоговый мультиплексор - 35, третий аналоговый мультиплексор - 36, источник опорного напряжения - 37.

В зависимости от сигнала на первой адресной шине А1 второй аналоговый мультиплексор 35 подключает емкости 34а-34п или параллельно емкости 341 или к выходу источника опорного напряжения 37, Параллельное включение емкостей изменяет постоянную времени интегратора на основе операционного усилителя 31. Подключение же заряженных до уровня Еоп емкостей позволяет в самом нижнем, и следовательно, в самом инерционном поддиапазоне выйти сразу в середину поддиапазона, чем ускоряется процесс установления показаний.

С помощью третьего аналогового мультиплексора 36 сигналом по шине начальной установки производится разряд емкостей кодоуправляемого фильтра низкой частоты при сбросе показаний.

Управление постоянной времени фильтра 13 позволяет реализовать вторую ступень регулирования динамических характеристик измерителя. Для устойчивой

работы измерителя следует выбирать постоянную времени кодоуправляемого фильтра 13 на 30-50% больше эквивалентной постоянйой времени цифровой схемы сглаживания входной импульсной последо0 вательности. Выход кодоуправляемого фильтра низкой частоты 13 является аналоговым выходом устройства. Формирование сигнала на выходе фильтра 13 показано на фиг, 6.

5 Одновременно аналоговый выходной сигнал поступает на вход аналого-цифрового преобразователя .18, выход которого управляет блоком цифровой индикации 15 и поступает на вход первого дешифратора 19.

0 Положение запятой блока цифровой индикации 15 управляется с первого адресного выхода блока формирования адресов 6.

В блоке формирования адресов 6 третий счетчик 21 накапливает число импульсов,

5 соответствующее номеру декадного поддиапазона работы устройства. С выхода счетчика 21 через второй дешифратор 22 формируется первая адресная шина устройства, которая управляет декадным делите0 лем в блоке деления частоты 2, постоянной времени кодоуправляемого фильтра низкой частоты 13 и положением запятой блока цифровой индикации 15. Запись очередного импульса в третий счетчик 21 возможна

5 через третью схему ИЛИ - 20 в двух случаях - при переполнении первого счетчика 7 и при выходе кода на выходе аналого-цифрового преобразователя 18 за верхнюю границу поддиапазона. Вариант перехода

0 устройства в старший поддиапазон по аналоговому выходу измерителя предусматривается для работы в младших поддиапазонах, когда при незначительном превышении fx над fu времени лереполне5 ния счетчика 7 очень велико, что ухудшает 1 динамические свойства устройства. В этом случае, учитывая тот факт, что выход фильтра 13 в младшем поддиапазоне устанавливается сразу в середину поддиапазона,

0 переполнение шкалы по аналоговому сигналу происходит раньше, чем на выходе цифровой схемы сглаживания, переход устройства в старший поддиапазон происходит по импульсу с выхода первого дешиф5 ратора 19. С выхода первого дешифратора 19 формируется также вторая адресная шина А2 устройства, которая управляет переключением скрытых поддиапазонов внутри каждого декадного поддиапазона. Если аналоговый сигнал опускается ниже половины

поддиапазона, то частота серии уменьшается вдвое, при этом, чтобы сохранить линей- ность шкалы внутри декадного поддиапазона вдвое уменьшается амплитуда опорного напряжения на выходе цифро- аналогового преобразователя 14. Если сигнал на выходе измерителя падает ниже четверти поддиапазона, то fu уменьшается еще вдвое, и аналогично амплитуда напряжения на выходе цифроаналогового преоб- разователя 14. Управление двоичным делителем блока деления частоты 2 и циф- роаналоговым преобразователем 14 осуществляется по адресной шине А2.

Следует отметить, что первоначальное положение аналогового выхода внутри каждого Лоддиапазона равно или превышает половину диапазона, вследствие предварительного заряда конденсаторов, поэтому внутри декадного поддиапазона возможно только понижение частоты fu, что исключает появление неустойчивого режима работы.

С выхода первого дешифратора Сформируется также сигнал начала поиска, кото- рый вырабатывается при снижении сигнала на выходе до уровня нижней границы поддиапазона. Сигнал начала поиска блока формирования адресов 6 объединяется на второй схеме ИЛИ 16с сигналом внешне- го сброса и сигналом переполнения второго счетчика 9. В результате на выходе второй схемы ИЛИ - 16 формируется общий сигнал сброса, по которому осуществляется сброс третьего счетчика 21 в блоке форми- рования адресов 6, т.е. устройство устанавливается в младший декадный поддиапазон. Через одновибратор 17 производится установка начального кода в первый счетчик 7 и разряд неотключаемой емкости 33 кодоуправляемого фильтра, низкой частоты 13 для сброса в ноль показаний блока цифровой индикации 15.

Работа устройства после включения питания по состоянию инерционного аналоге- вого выхода всегда начинается с формирования импульса на выходе начала поиска блока формирования адресов 6. Этим импульсом по цепи сброса и начальной установки осуществляется первона- чальная установка первого счетчика 7 и третьего счетчика 21, состояние которых определяет дальнейшую работу измерителя. Сброс третьего счетчика 21 означает положение работы устройства в младшем декадном поддиапазоне. При этом величина принимает наименьшее значение. Если fx fui,To происходит переполнение счетчика 7 или переполнение аналоговой шкалы и в счетчик 21 записывается единица.

При этом величина fu увеличивается в 10 раз. Аналогично происходят переходы в следующие поддиапазоны. Наконец, если fx fu.n, то в n-ом декадном поддиапазоне наступает динамическое равновесие состояния счетчика 7. Далее происходит снижение значения fu в 2 или 4 раза, если состояние аналогового выхода не превышает соответственно половины или четверти поддиапазона. Окончательно завершается поиск поддиапазона при выполнении условия: fu fx 5: fu/2. Входная импульсная последовательность в устройстве сглаживается тремя ступенями интегрирования: цифровой схемой сглаживания, аналоговым фильтром низкой частоты и схемой аналого-цифрового преобразователя.

При повышении частоты fx сначала будет производиться наращивание величины fu внутри декадного поддиапазона, а затем переход в старший поддиапазон.

При понижении частоты fx ниже нижнего значения поддиапазона происходит сброс номера поддиапазона в нулевое состояние, а затем новый поиск по изложенной выше схеме.

Для выявления преимуществ заявляемого устройства перед устройством прототипом сравним их по быстродействию и величине динамического диапазона. Динамический диапазон измерителя средней частоты определяется допустимым уровнем относительной погрешности в нижней части шкалы измерения. В устройстве прототипа имеется одна линейная измерительная шкала, а в заявляемом устройстве - п декадных линейных шкал. Если определить допустимый уровень относительной погрешности для устройства прототипа и заявляемого устройства одинаковым, то будет иметь место расширение динамического диапазона заявляемого устройства в п раз. Кроме того, высокая разрешающая способность заявляемого устройства по парным импульсам позволяет поднять верхний уровень шкалы измерения в зависимости от используемой серии микросхем до 10 МГц. Причем высокая разрешающая способность измерителя средней частоты по парным импульсам сохраняется во всем диапазоне измерений. Кроме того многоступенчатая схема изменения постоянной времени измерителя и ускоренный алгоритм поиска зоны нахождения среднего входной последовательности fx делают возможным при удовлетворительных динамических характеристиках увеличив постоянную времени интегратора расширить диапазон измерения вниз до уровня 0,1 с .

Быстродействие устройства прототипа определяется постоянной времени цифрового и аналогового, интегратора в нижней части диапазона измерения, т.е. является постоянной величиной для измерения во всем динамическом диапазоне шкалы. Заявляемое устройство сочетает в своей структуре алгоритм ускоренного поиска диапазона измерения с переменной постоянной времени интегратора. Кроме того в заявляемом устройстве включено последовательно три интегратора, следовательно время установления сигнала на выходе при равных постоянных времени сокращается в 1,7 раза. С учетом начальной установки интеграторов измерителя в средину шкалы измерения время установления сигнала в нижнем поддиапазоне измерения сокращается не менее, чем в 2 раза. Соответственно при той же точности в следующем декадном поддиапазоне, с уметом квадратичной зависимости точности от постоянной времени интегратора, - не менее, чем в 6 раз, далее в 18 раз и т.д. Если сравнивать заявляемое устройство и устройства прототип в диапазоне 10 - 100 при нижнем пределе шкалы измерения , то быстродействие заявляемого устройства относительно устройства прототипа повышается не менее, чем в .6 раз.

Заявляемое устройство может быть реализовано на микросхемах серия 555, 140, 590, 594, 572.

Таким образом проведенный сравнительный анализ показал, что заявляемое устройство имеет в п раз (n 1...6) более широкий динамический диапазон измерений и в 6 раз более высокое быстродействие.

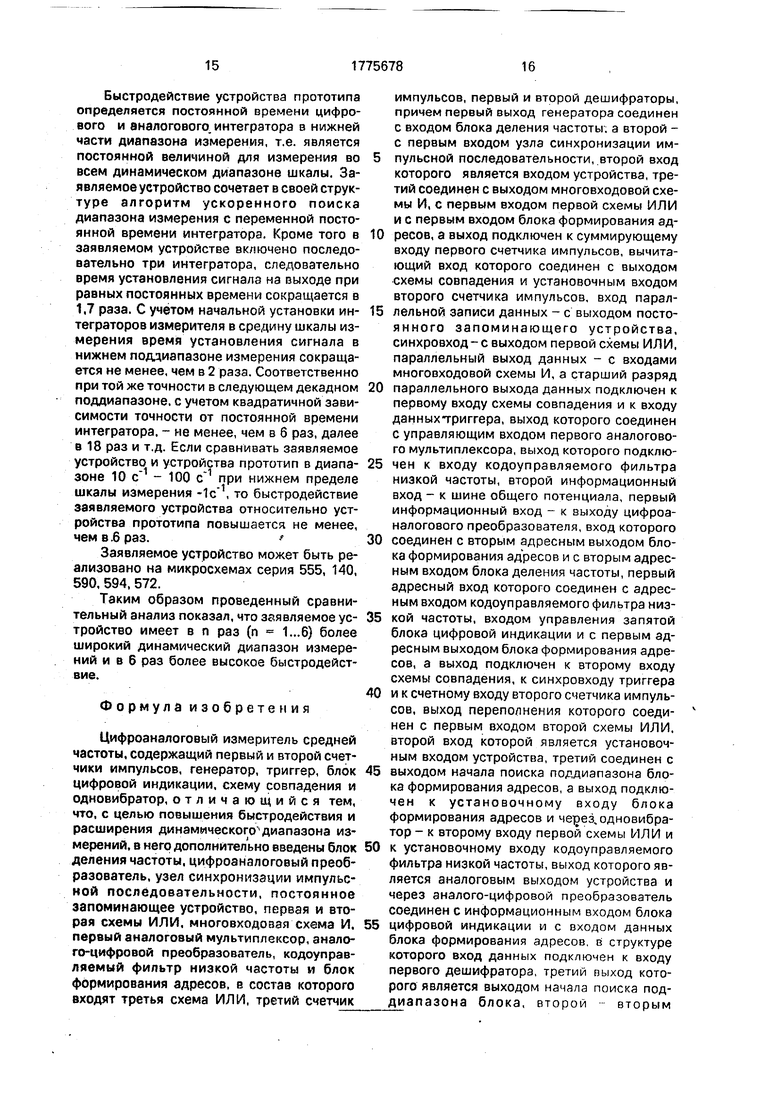

Формула изобретения

Цифроаналоговый измеритель средней частоты, содержащий первый и второй счетчики импульсов, генератор, триггер, блок цифровой индикации, схему совпадения и одновибратор, отличающийся тем, что, с целью повышения быстродействия и расширения динамического диапазона измерений, в него дополнительно введены блок деления частоты, цифроаналоговый преобразователь, узел синхронизации импульсной последовательности, постоянное запоминающее устройство, первая и вторая схемы ИЛИ, многовходовая схема И. первый аналоговый мультиплексор, аналого-цифровой преобразователь, кодоуправ- ляемый фильтр низкой частоты и блок формирования адресов, в состав которого входят третья схема ИЛИ, третий счетчик

импульсов, первый и второй дешифраторы, причем первый выход генератора соединен с входом блока деления частоты, а второй - с первым входом узла синхронизации импульсной последовательности, второй вход которого является входом устройства, третий соединен с выходом многовходовой схемы И, с первым входом первой схемы ИЛИ и с первым входом блока формирования ад0 ресов, а выход подключен к суммирующему входу первого счетчика импульсов, вычитающий вход которого соединен с выходом схемы совпадения и установочным входом второго счетчика импульсов, вход парал5 лельной записи данных - с выходом посто- янного запоминающего устройства, синхровход - с выходом первой схемы ИЛИ, параллельный выход данных - с входами многовходовой схемы И, а старший разряд

0 параллельного выхода данных подключен к первому входу схемы совпадения и к входу данныхтриггера, выход которого соединен с управляющим входом первого аналогового мультиплексора, выход которого подклю5 чен к входу кодоуправляемого фильтра низкой частоты, второй информационный вход - к шине общего потенциала, первый информационный вход - к выходу цифроа- налогового преобразователя, вход которого

0 соединен с вторым адресным выходом блока формирования адресов и с вторым адресным входом блока деления частоты, первый адресный вход которого соединен с адресным входом кодоуправляемого фильтра низ5 кой частоты, входом управления запятой блока цифровой индикации и с первым адресным выходом блока формирования адресов, а выход подключен к второму входу схемы совпадения, к синхровходу триггера

0 и к счетному входу второго счетчика импульсов, выход переполнения которого соединен с первым входом второй схемы ИЛИ. второй вход которой является установочным входом устройства, третий соединен с

5 выходом начала поиска поддиапазона блока формирования адресов, а выход подключен к установочному входу блока формирования адресов и , одновибратор - к второму входу первой схемы ИЛИ и

0 к установочному входу кодоуправляемого фильтра низкой частоты, выход которого является аналоговым выходом устройства и через аналого-цифровой преобразователь соединен с информационным входом блока

5 цифровой индикации и с входом данных блока формирования адресов в структуре которого вход данных подключен к входу первого дешифратора, третий выход которого является выходом начала поиска поддиапазона блока, второй вторым

адресным выходом блока, а первый поступает на второй вход третьей схемы ИЛИ, первый вход которой является первым входом блока, а выход подключен к счетному

вочный вход которого является установ ным входом блока, а параллельный вы соединен с входами второго дешифрато выход которого является первым адресн

входу третьего счетчика импульсов, устано- 5 выходом блока формирования адресов.

вочный вход которого является установочным входом блока, а параллельный выход соединен с входами второго дешифратора, выход которого является первым адресным

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИССЛЕДОВАНИЯ АМПЛИТУДНО-ЧАСТОТНЫХ ХАРАКТЕРИСТИК ЧЕТЫРЕХПОЛЮСНИКА | 1992 |

|

RU2065667C1 |

| Анализатор кодовых последовательностей импульсов (его варианты) | 1984 |

|

SU1238243A1 |

| Устройство для регистрации сигналов | 1991 |

|

SU1774272A1 |

| Измеритель частоты | 1989 |

|

SU1691768A1 |

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

| Многоканальное устройство для регистрации и индикации аварийных ситуаций | 1990 |

|

SU1796907A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| Многоканальный программируемый генератор импульсов | 1986 |

|

SU1374413A1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

Изобретение относится к измерительной технике и может быть использовано для измерения средней частоты равномерной импульсной последовательности. Измеритель содержит: 1 генератор, 1 блок деления частоты, 1 узел синхронизации импульсной последовательности, 1 схему И, 3 схемы ИЛИ, 1 блок формирования адресов, 3 счетчика импульсов, 1 схему совпадения, 1 ПЗУ, 1 триггер, аналоговый мультиплексор. 1 фильтр низкой частоты, 1 ЦАП, 1 блок цифровой индикации, 1 одновибратор, 1 АЦП, 2 дешифратора. 7 ил.

Фие.2.

П /ЛГУ /1 Л Л П П t

т т гп/ л у

ft/г. ,

Фиъ$

г tf

и. 1-Ч-ч1-ч

.I

H

г -у v

f

VI

.I

H

V

.% Л с г ;

8А99Ш

| Цифровой интенсиметр | 1974 |

|

SU551579A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Кинематографический аппарат | 1923 |

|

SU1970A1 |

Авторы

Даты

1992-11-15—Публикация

1991-03-28—Подача