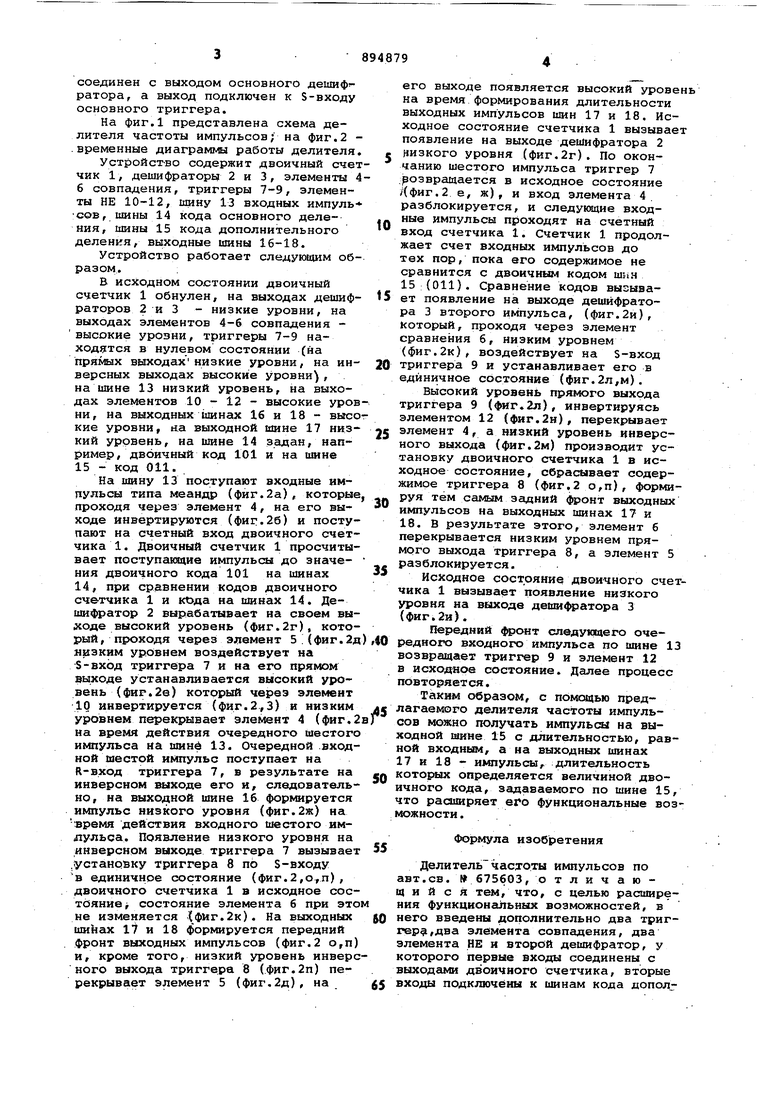

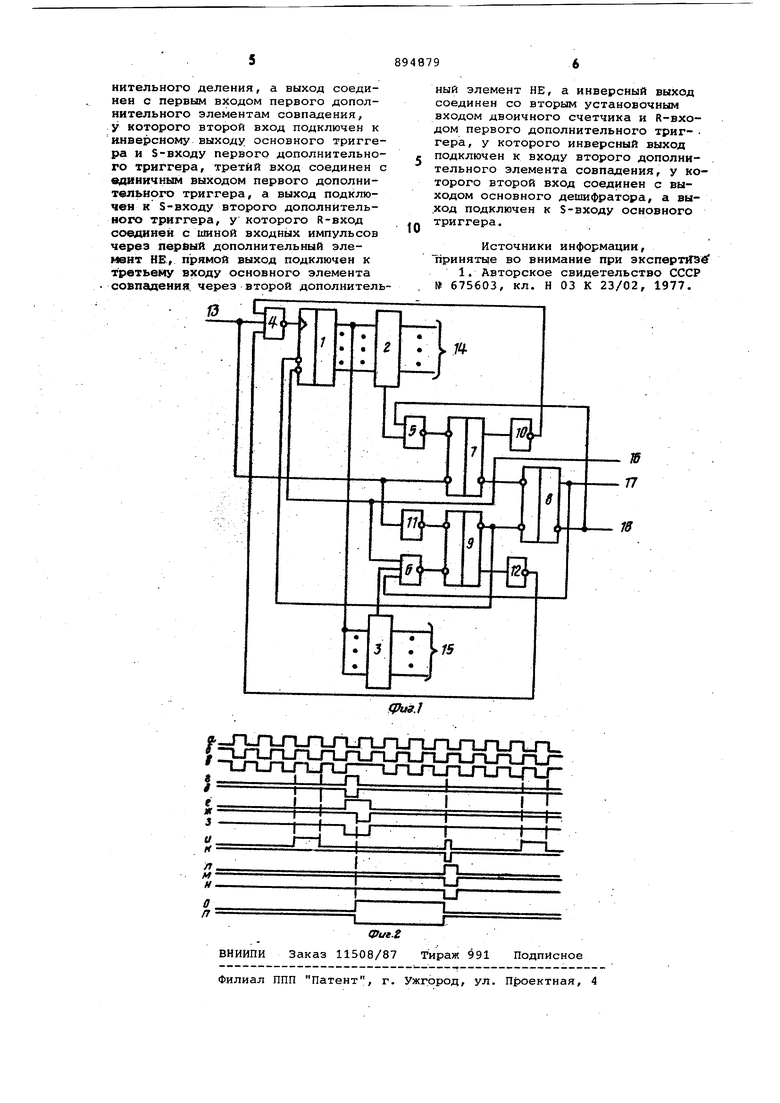

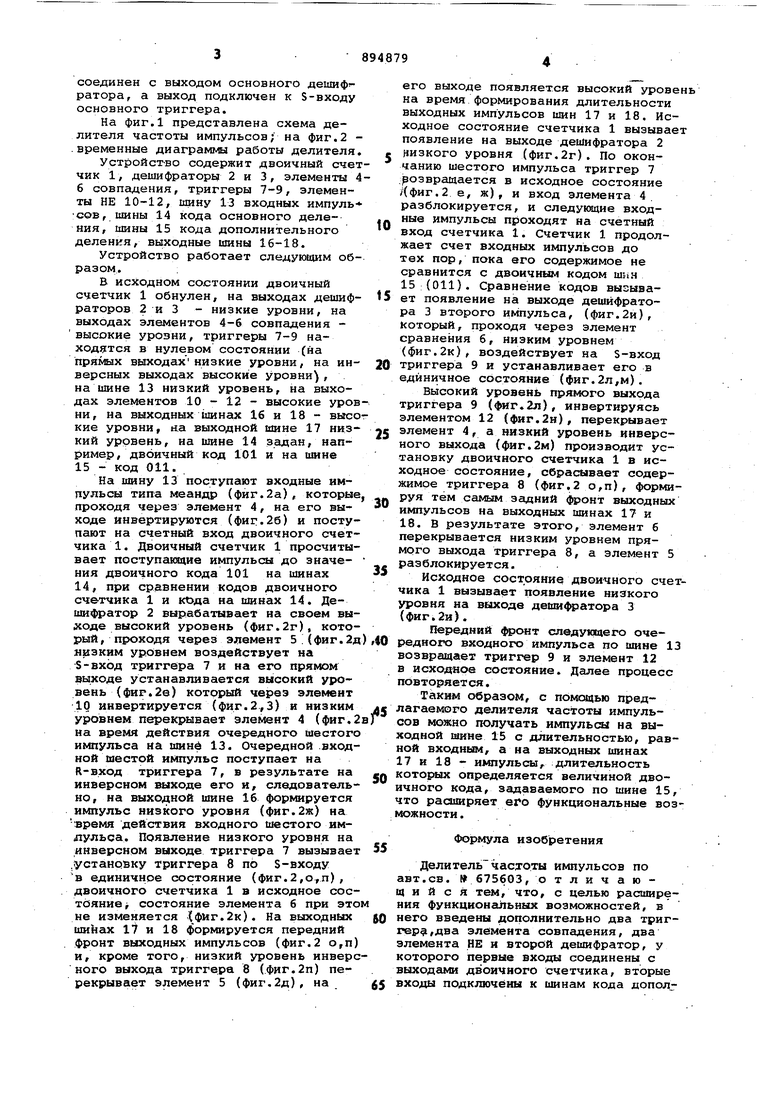

Изобретение относится к вычислительной технике и может быть исполь зовано в цифровых и управляющих уст Е ойствах. По основному авт.св. № 675603 известен делитель частоты импульсов содержащий двоичный счетчик, подсое динённый счетным входом к шине вход ных импул1зсЬв через элемент совпадения , у которого второй вход подключен через элемент НЕ к единичному выходу триггера, у которого инверсный выход соединен с установочным входом двоичного счетчика, а R-вход подключен к шине входных импульсов, выходы двоичного счетчика соединены со входами дешифратора, другие входы которого подключены к шинам кода основного деления.| Недостаток известного делителяограниченные функциональные возможности в связи с тем, что длительность выходных импульсов равна толь ко длительности входных. Цель изобретения - расширение функциональных возможностей за счет получения регулируемой длительности выходных сигналов. Поставленная цель достигается тем,что в делитель частоты импульсов введены дополнительно два триггера, два элемента совпадения, два элемента НЕ и второй дешифратор, у которого первые входы соединены с выходами двоичного счетчика, вторые входы подключены к шинам кода дополнительного деления, а выход соединен с первым входом первого дополнительного элемента совпадения, у которого второй вход подключен к инверсному выходу основного триггера и S-входу первого дополнительного триггера, третий вход соединен с единичным выходом первого дополнительного триггера, а вь1ход подключен к S-входу дополнительного триггера, у которого -К-вход соединен с шиной входных импульсов через первый дополнительный элемент НЕ, прямой выход подключен к третьему входу основного элемента совпадения через второй дополнительный элемент НЕ, а инверсный выход соединен со вторым установочным входом двоичного счетчика и с R-входом первого дополнительного триггера, у которого инверсный выход подключен к входу второго дополнительного элемента совпадения, у которого второй вход соединен с выходом основного дешиф ратора, а выход подключен к S-входу основного триггера, На фиг.1 представлена схема делителя частоты импульсов; на фиг.2 .временные диаграммы работы делителя. Устройст-во содержит двоичный счет чик 1, дешифраторы 2 и 3, элементы 4 6 совпадения, триггеры 7-9, элементы НЕ 10-12, шину 13 входных импуль сов, шины 14 кода основного деления, шины 15 кода дополнительного деления, выходные шины 16-18. Устройство работает следующим образом. : В исходном состоянии двоичный счетчик 1 обнулен, на выходах дешифраторов 2 и 3 - низкие уровни, на выходах элементов 4-6 совпадения высокие уровни, триггеры 7-9 находится в нулевом состоянии (на npHNMX выходахнизкие уровни, на инвареных выходах высокие уровни), на шине 13 низкий уровень, на выходах элементов 10 - 12 - высокие уров ни, на выходных шинах 16 и 18 - высо кие уровни, tia выходной шине 17 низкий уровень, на шине 14 задан, например, двоичный код 101 и на шине 15 - код 011. На шину 13 поступают входные импульсы типа меандр (фиг.2а), которые проходя через элемент 4, на его выходе инвертируются (фиг.26) и поступают на счетный вход двоичного счетчика 1. Двоичный счетчик 1 просчитывает поступакяцие импульсы до значения двоичного кода 101 на шинах 14, при сравнении кодов двоичного счетчика 1 и кода на шинах 14. Дешифратор 2 вырабатывает на своем выходе высокий уровень (фиг.2г), который, проходя через элемент 5 . (фиг.2д яизким уровнем воздействует на S-вхЬд триггера 7 и на его прямом выходе устанавливается высокий уровень (фиг.2е) который через элемент 10 инвертируется (фиг.2,3) и низким уровнем перекрывает элемент 4 (фиг.2 на время действия очередного шестого импульса на шине 13. Очередной входной шестой импульс поступает на R-вход триггера 7, в результате на инверсном выходе его и, следовательно, на выходной шине 16 формируется импульс низкого уровня (фиг.2зк) на время действия входного шестого имлульса. Появление низкого уровня на инверсном выходе триггера 7 вызывает .установку триггера 8 по S-входу в единичное состояние (фиг.2,о,п), двоичного счетчика 1 в исходное состояние j состояние элемента б при это не изменяется (фиг.2к). На выходных шийах 17 и 18 формируется передний фронт выходных импульсов (фиг.2 о,п и, кроме того, низкий уровень инвер ного выхода триггера 8 (фиг.2п) перекрывает элемент 5 (фиг.2д), на его выходе появляется высокий уровень на время формирования длительности выходных импульсов шин 17 и 18. Исходное состояние счетчика 1 вызывает появление на выходе дешифратора 2 низкого уровня (фиг.2г). По окончанию шестого импульса триггер 7 .розвраиается в исходное состояние /(фиг.2 е, ж), и вход элемента 4 разблокируется, и следукнцие входные импульсы проходят на счетный вход счетчика 1. Счетчик 1 продолжает счет входных импульсов до тех пор, пока его содержимое не сравнится с двоичным кодом шин 15 (011). Сравнение кодов вызывает появление на выходе дешифратора 3 второго импульса, (фиг.2и), который, проходя через элемент сравнения б, низким уровнем (фиг.2к), воздействует на S-вход триггера 9 и устанавливает его в едйничное состояние (фиг.2л,м). Высокий уровень прямого выхода триггера 9 (фиг.2л), инвертируясь элементом 12 (фиг.2н), перекрывает элемент 4, а низкий уровень инверсного выхода (фиг.2м) производит установку двоичного счетчика 1 в исходное состояние, сбрасывает содержимое триггера 8 (фиг.2 о,п), формируя тем самым задний фронт выходных импульсов на выходных шинах 17 и 18. В результате этого, элемент б перекрывается низким уровнем прямого выхода триггера 8, а элемент 5 разблокируется. Исходное состояние двоичного счетчика 1 вызывает появление низкого уровня на выходе дешифратора 3 (фиг.2и). Передний онт следующего очередного входного импульса по шине 13 возвращает триггер 9 и элемент 12 в исходное состояние. Далее процесс повторяется. Таким образом, с помощью предлагаемого делителя частоты импульсов можно получать импульсы на выходной шине 15 с длительностью, равной входным, а на выходных шинах 17 и 18 - импульсы, длительность определяется величиной двоичного кода, задаваемого по шине 15, что расширяет его функциональные возможности. Формула изобретения делитель частоты импульсов по авт.св. №675603, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены дополнительно два триггеру, два элемента совпадения, два элемента НЕ и второй дешифратор, у которого первые входы соединены с выходами двоичного счетчика, вторые входы подключены к шинам кода дополг

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следования импульсов с регулируемой длительностью импульсов | 1980 |

|

SU924868A1 |

| Формирователь задержанных импульсов | 1980 |

|

SU924839A1 |

| Делитель частоты с дискретной регулировкой длительности импульсов | 1984 |

|

SU1226662A1 |

| Делитель частоты следования им-пульСОВ C пЕРЕМЕННыМ КОэффициЕНТОМ дЕлЕНия | 1979 |

|

SU839065A1 |

| Устройство выделения одиночного @ -го импульса | 1981 |

|

SU1001454A1 |

| Формирователь задержанных импульсов | 1984 |

|

SU1175019A1 |

| Управляемый делитель частоты | 1983 |

|

SU1138943A2 |

| Управляемый формирователь импульсов | 1984 |

|

SU1211859A1 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1322471A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1982 |

|

SU1115239A2 |

Авторы

Даты

1981-12-30—Публикация

1980-03-03—Подача