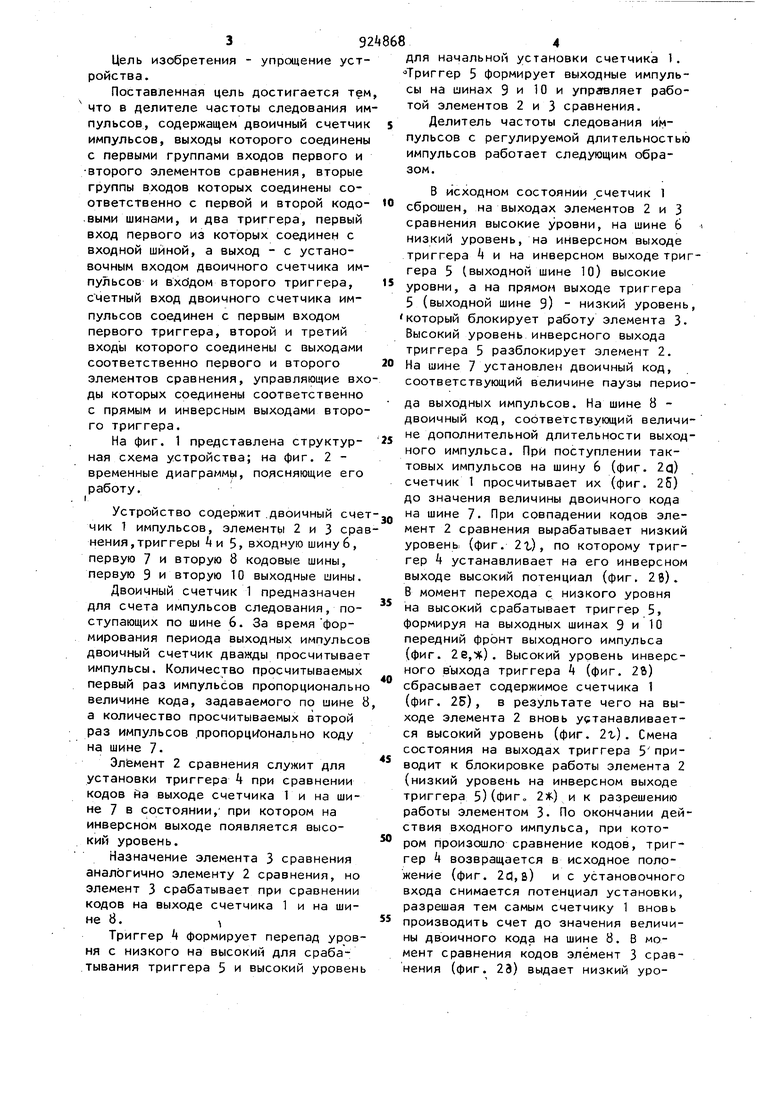

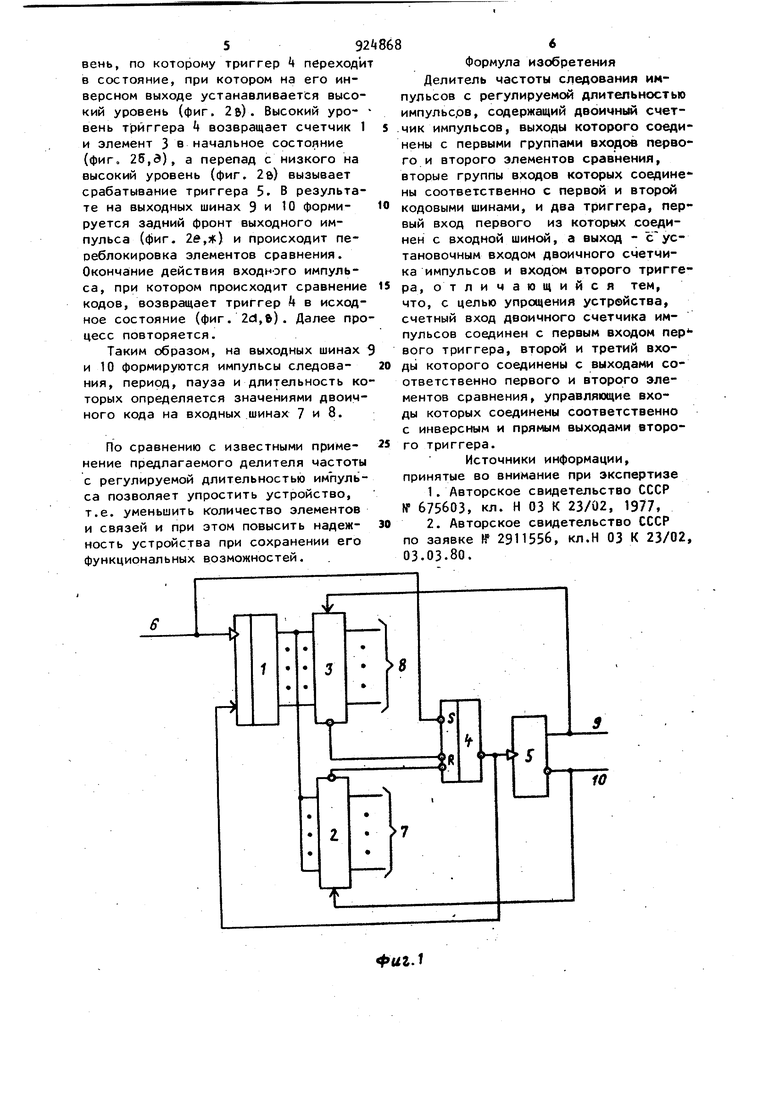

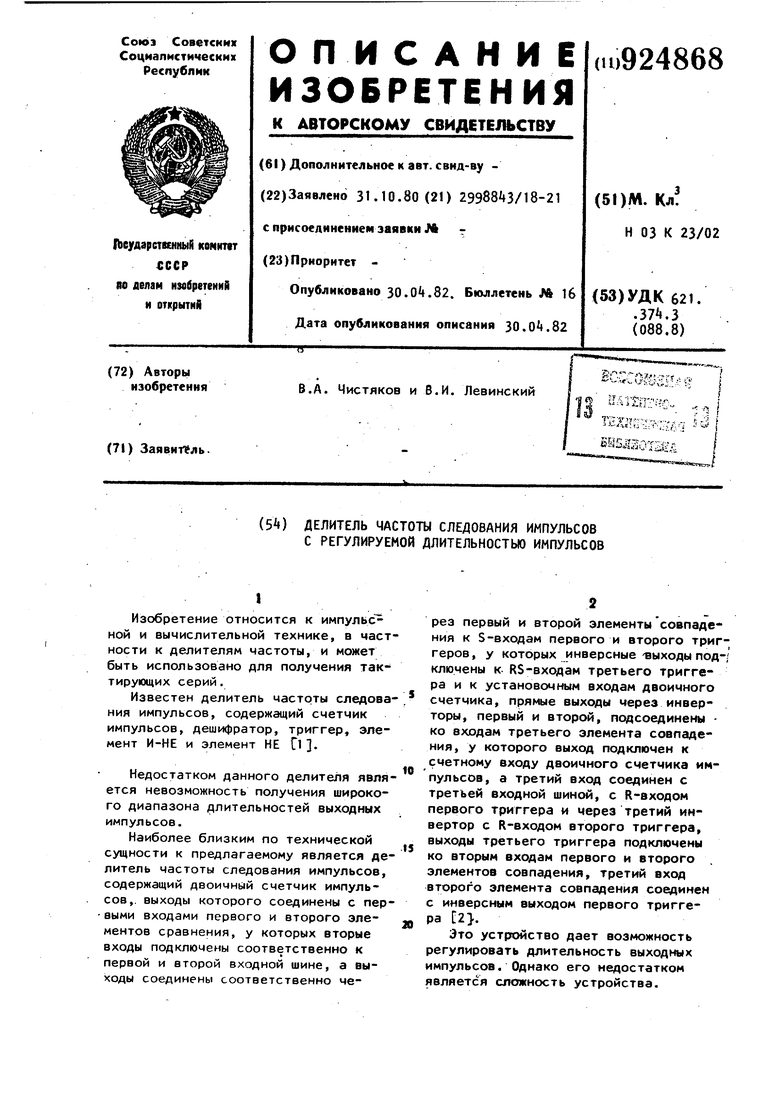

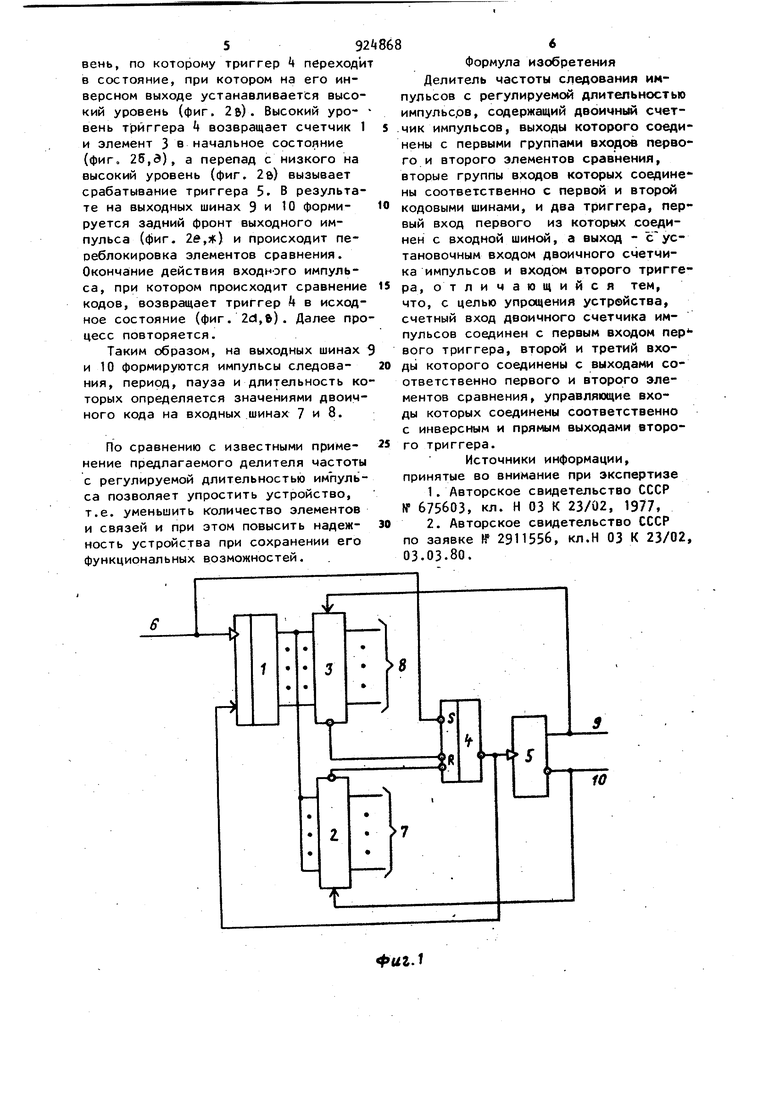

Изобретение относится к импульсной и вычислительной технике, в част ности к делителям частоты, и может быть использовано для получения тактирующих серий. Известен делитель частоты следова ния импульсов, содержащий счетчик импульсов, дешифратор, триггер, элемент И-НЕ и элемент НЕ D. Недостатком данного делителя явля ется невозможность получения широкого диапазона длительностей выходных импульсов. Наиболее близким по технической сущности к предлагаемому является де литель частоты следования импульсов, содержащий двоичный счетчик импульсов,, выходы которого соединены с пер выми входами первого и второго элементов сравнения, у которых вторые входы подключены соответственно к первой и второй входной шине, а выходы соединены соответственно через первый и второй элементы совпадения к S-входам первого и второго триггеров, у которых инверсные-выходы под-/ ключены к RS-входам третьего триггера и к установочным входам двоичного счетчика, прямые выходы через инверторы, первый и второй, подсоединены ко входам третьего элемента совпадения, у которого выход подключен к счетному входу двоичного счетчика импульсов, а третий вход соединен с третьей входной шиной, с R-входом первого триггера и через третий инвертор с R-входом второго триггера, выходы третьего триггера подключены ко вторым входам первого и второго элементов совпадения, третий вход второго элемента совпадения соединен с инверсным выходом первого триггера 2. Это устройство дает возможность регулировать длительность выходных импульсов. Однако его недостатком является сложность устройства. Цель изобретения - упрощение устройства. Поставленная цель достигается тем что в делителе частоты следования им пульсов, содержащем двоичный счетчик импульсов, выходы которого соединены с первыми группами входов первого и второго элементов сравнения, вторые группы входов которых соединены соответственно с первой и второй кодовыми шинами, и два триггера, первый вход первого из которых соединен с входной шиной, а выход - с установочным входом двоичного счетчика импульсов и входом второго триггера, счетный вход двоичного счетчика импульсов соединен с первым входом первого триггера, второй и третий входы которого соединены с выходами соответственно первого и второго элементов сравнения, управляющие вхо ды которых соединены соответственно с прямым и инверсным выходами второ го триггера. На фиг. 1 представлена структурная схема устройства; на фиг. 2 временные диаграмму, поясняющие его работу. Устройство содержит .двоичный сче чик 1 импульсов, элементы 2 и 3 сра нения, триггеры 4 и 5, входную шину 6, первую 7 и вторую 8 кодовые шины, первую 9 и вторую 10 выходные шины. Двоичный счетчик 1 предназначен для счета импульсов следования, поступающих по шине 6. За времяформирования периода выходных импульсо двоичный счетчик дважды просчитывае импульсы. Количество просчитываемых первый раз импульсов пропорциональн величине кода, задаваемого по шине а количество просчитываемых второй раз импульсов .пропорц| онально коду на шине 7. Элемент 2 сравнения служит для установки триггера k при сравнении кодов йа выходе счетчика 1 и на шине 7 в состоянии, при котором на инверсном выходе появляется высокий уровень. Назначение элемента 3 сравнения аналогично элементу 2 сравнения, но элемент 3 срабатывает при сравнении кодов на выходе счетчика 1 и на шине 8. Триггер 4 формирует перепад уров ня с низкого на высокий для срабатывания триггера 5 и высокий уровен для начальной установки счетчика 1. Триггер 5 формирует выходные импульсы на шинах 9 и 10 и упрагвляет работой элементов 2 и 3 сравнения. Делитель частоты следования импульсов с регулируемой длительностью импульсов работает следующим образом. В исходном состоянии счетчик 1 сброшен, на выходах элементов 2 и 3 сравнения высокие уровни, на шине 6 низкий уровень, на инверсном выходе триггера 4 и на инверсном выходе три:- гера 5 (выходной шине 10) высокие уровни, а на прямом выходе триггера 5 (выходной шине 9) низкий уровень, который блокирует работу элемента 3. Высокий уровень инверсного выхода триггера 5 разблокирует элемент 2. На шине 7 установлен двоичный код, соответствующий величине паузы периода выходных импульсов. На шине 8 двоичный код, соответствующий величине дополнительной длительности выходного импульса. При поступлении тактовых импульсов на шину 6 (фиг. 2с|) счетчик 1 просчитывает их (фиг. 25) до значения величины двоичного кода на шине 7- При совпадении кодов элемент 2 сравнения вырабатывает низкий уровень (фиг. 2г), по которому триггер 4 устанавливает на его инверсном выходе высокий потенциал (фиг. 28). В момент перехода с низкого уровня на высокий срабатывает триггер 5 формируя на выходных шинах 9 и 10 передний фронт выходного импульса (фиг. 2е,). Высокий уровень инверсного вь1хода триггера (фиг. 26) сбрасывает содержимое счетчика 1 (фиг. 25), в результате чего на выходе элемента 2 вновь устанавливается высокий уровень (фиг. 2г). Смена состояния на выходах триггера 5приводит к блокировке работы элемента 2 (низкий уровень на инверсном выходе триггера 5)(фиГо 2.) и к разрешению работы элементом 3. По окончании действия входного импульса, при котором произошло сравнение кодов, триггер возвращается в исходное положение (фиг. 2(3, в) и с установочного входа снимается потенциал установки, разрешая тем самым счетчику 1 вновь производить счет до значения величины двоичного кода на шине 8. В момент сравнения кодов элемент 3 сравнения (фиг. 23) выдает низкий уро53вень, по которому триггер «4 переход в состояние, при котором на его инверсном выходе устанавливается высо кий уровень (фиг. 2б). Высокий уровень триггера k возвращает счетчик и элемент 3 в начальное состояние (фиго 26,Э), а перепад с низкого на высокий уровень (фиг, 2е) вызывает срабатывание триггера 5. В результа те на выходных шинах 9 и 10 формируется задний фронт выходного импульса (фиг. 2е,лс) и происходит переблокировка элементов сравнения. Окончание действия входного импульса, при котором происходит сравнение кодов, возвращает триггер k в исходное состояние (фиг. 20,е). Далее про цесс повторяется. Таким образом, на выходных шинах и 10 формируются импульсы следования, период, пауза и длительность ко торых определяется значениями двоичного кода на входных шинах 7 и 8. По сравнению с известными применение предлагаемого делителя частоты с регулируемой длительностью импульса позволяет упростить устройство, т.е. уменьшить количество элементов и связей и при этом повысить надежность устройства при сохранении его функциональных возможностей. 8 Формула изобретения Делитель частоты следования импульсов с регулируемой длительностью импульсрв, содержащий двоичный счетчик импульсов, выходы которого соединены с первыми группами входов первого и второго элементов сравнения, вторые группы входов которых соединены соответственно с первой и второй кодовыми шинами, и два триггера, первый вход первого из которых соединен с входной шиной, а выход - сустановочным входом двоичного счетчика импульсов и входом второго триггера, отличающийся тем, что, с целью упрощения устройства, счетный вход двоичного счетчика импульсов соединен с первым входом пер вого триггера, второй и третий входы которого соединены с выходами соответственно первого и второго элементов сравнения, управляющие входы которых соединены соответственно с инверсным и прямым выходами второго триггера. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР 675603, кл, Н 03 К 23/02, 1977, 2,Авторское свидетельство СССР о заявке (f 2911556, кл,Н 03 К 23/02. 3,03.80.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты импульсов | 1980 |

|

SU894879A2 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1982 |

|

SU1115239A2 |

| Формирователь задержанных импульсов | 1980 |

|

SU924839A1 |

| Устройство выделения одиночного @ -го импульса | 1981 |

|

SU1001454A1 |

| Делитель частоты следования им-пульСОВ C пЕРЕМЕННыМ КОэффициЕНТОМ дЕлЕНия | 1979 |

|

SU839065A1 |

| Делитель частоты следования импульсов с регулируемой длительностью импульсов | 1984 |

|

SU1241468A2 |

| Устройство для селекции и формирования импульсов | 1981 |

|

SU995301A1 |

| Устройство тактовой синхронизации и выделения пачки импульсов | 1983 |

|

SU1185588A2 |

| Управляемый формирователь импульсов | 1984 |

|

SU1211859A1 |

| Делитель частоты с дискретной регулировкой длительности импульсов | 1984 |

|

SU1226662A1 |

StR

10

Фиг.1 а

Фиг.2. -

Авторы

Даты

1982-04-30—Публикация

1980-10-31—Подача