(54) ФОРМИРОВАТЕЛЬ ЗАДЕРЖАННЫХ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь задержанных импульсов | 1984 |

|

SU1175019A1 |

| Делитель частоты следования импульсов с регулируемой длительностью импульсов | 1980 |

|

SU924868A1 |

| Делитель частоты импульсов | 1980 |

|

SU894879A2 |

| Делитель частоты с дискретной регулировкой длительности импульсов | 1984 |

|

SU1226662A1 |

| Устройство тактовой синхронизации и выделения пачки импульсов | 1983 |

|

SU1185588A2 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1322471A1 |

| Управляемый формирователь импульсов | 1984 |

|

SU1211859A1 |

| Устройство для контроля счетчика | 1982 |

|

SU1048579A1 |

| Устройство выделения одиночного @ -го импульса | 1981 |

|

SU1001454A1 |

| Преобразователь кода в период повторения импульсов | 1987 |

|

SU1495997A1 |

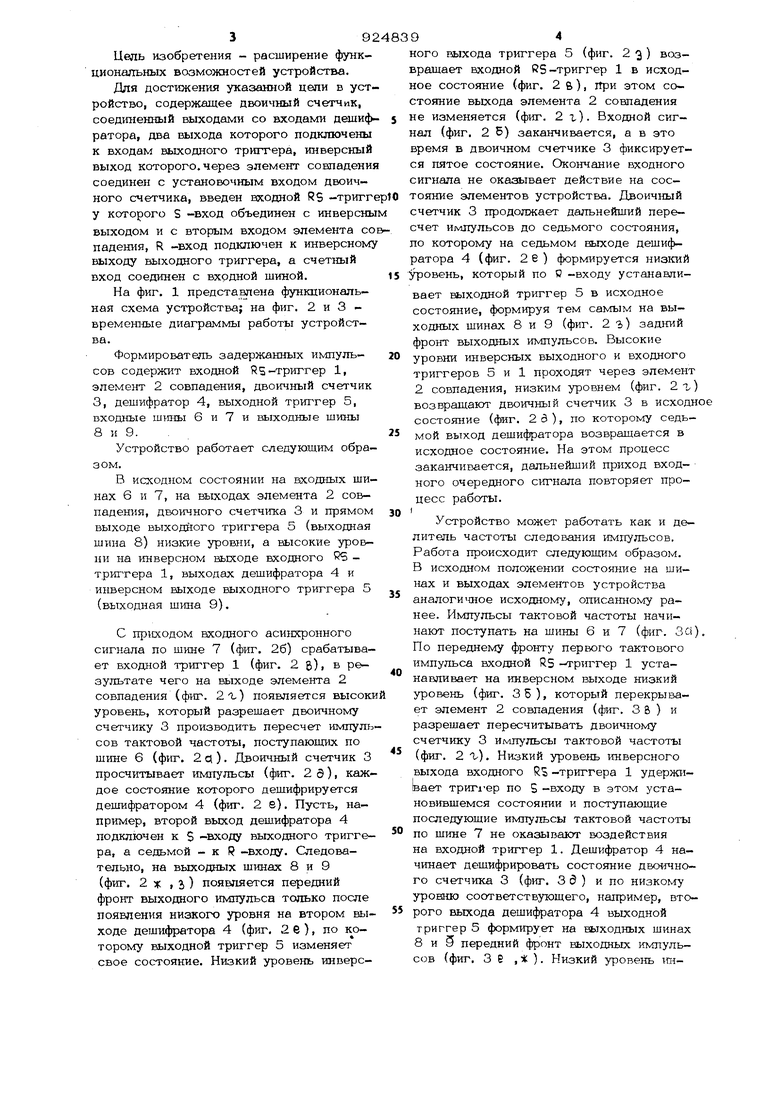

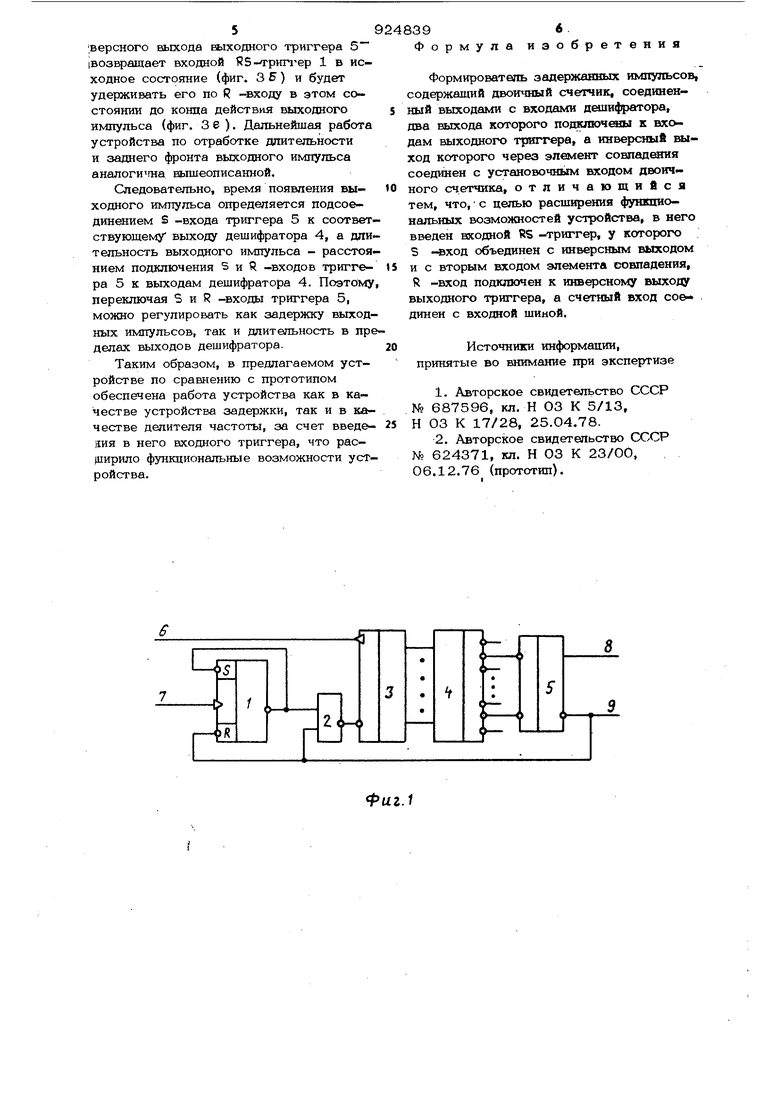

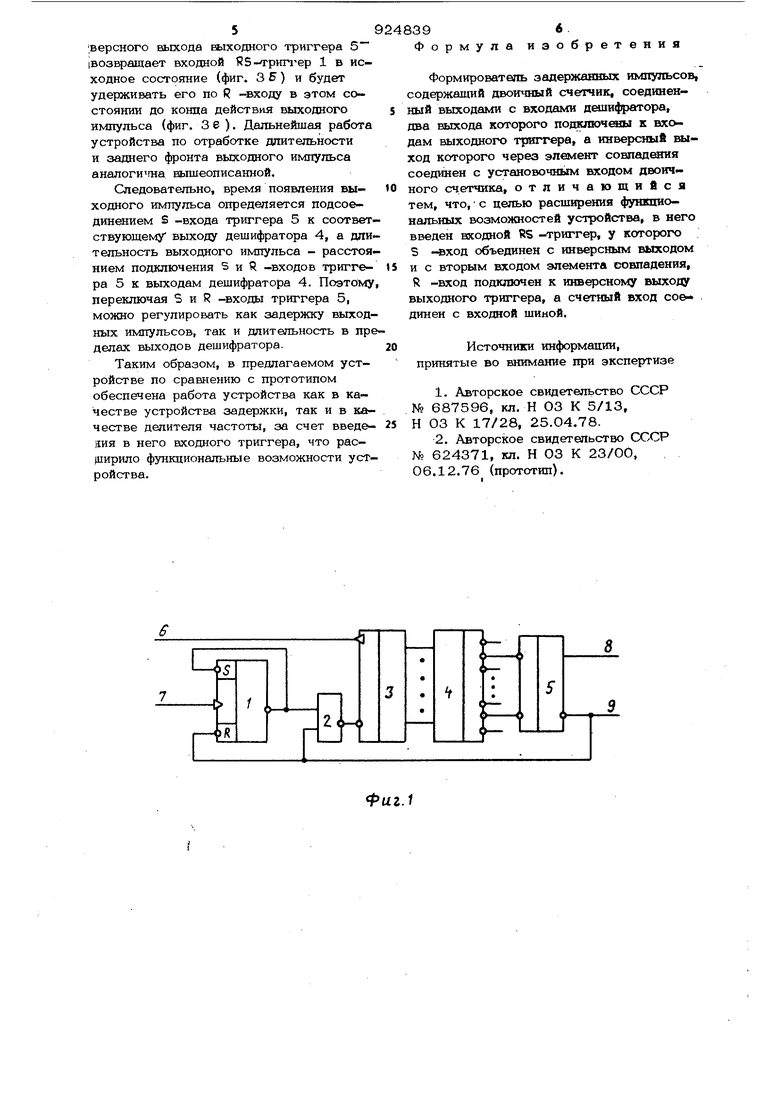

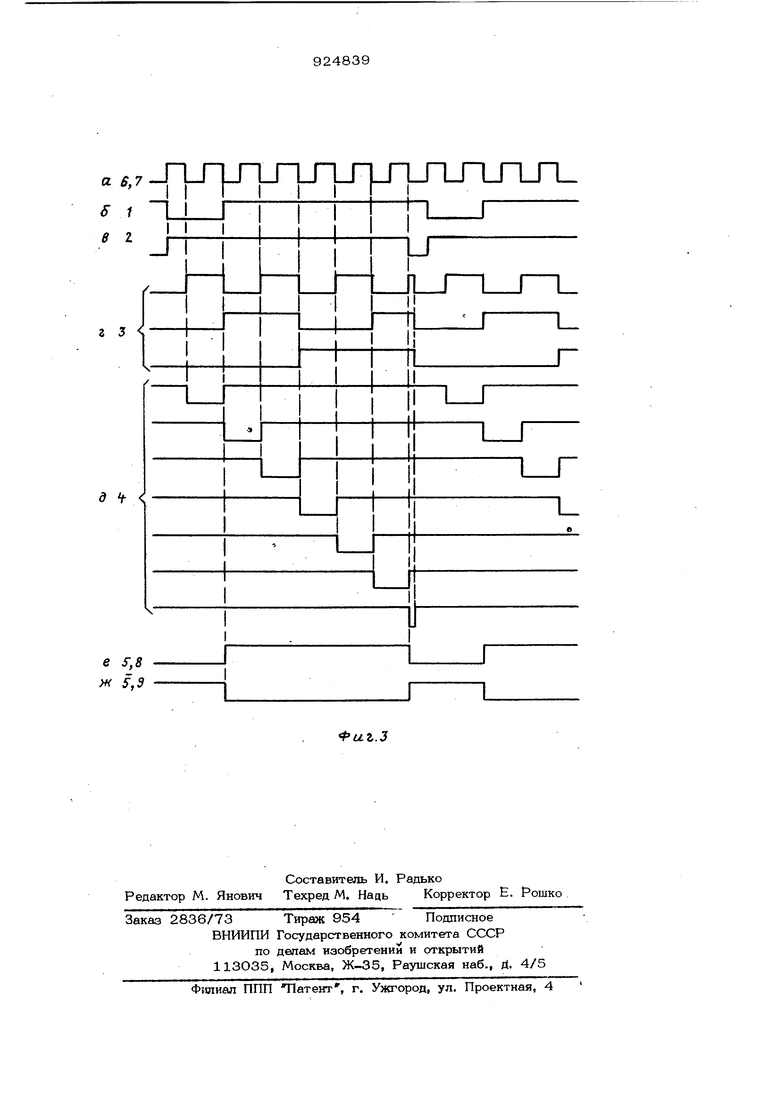

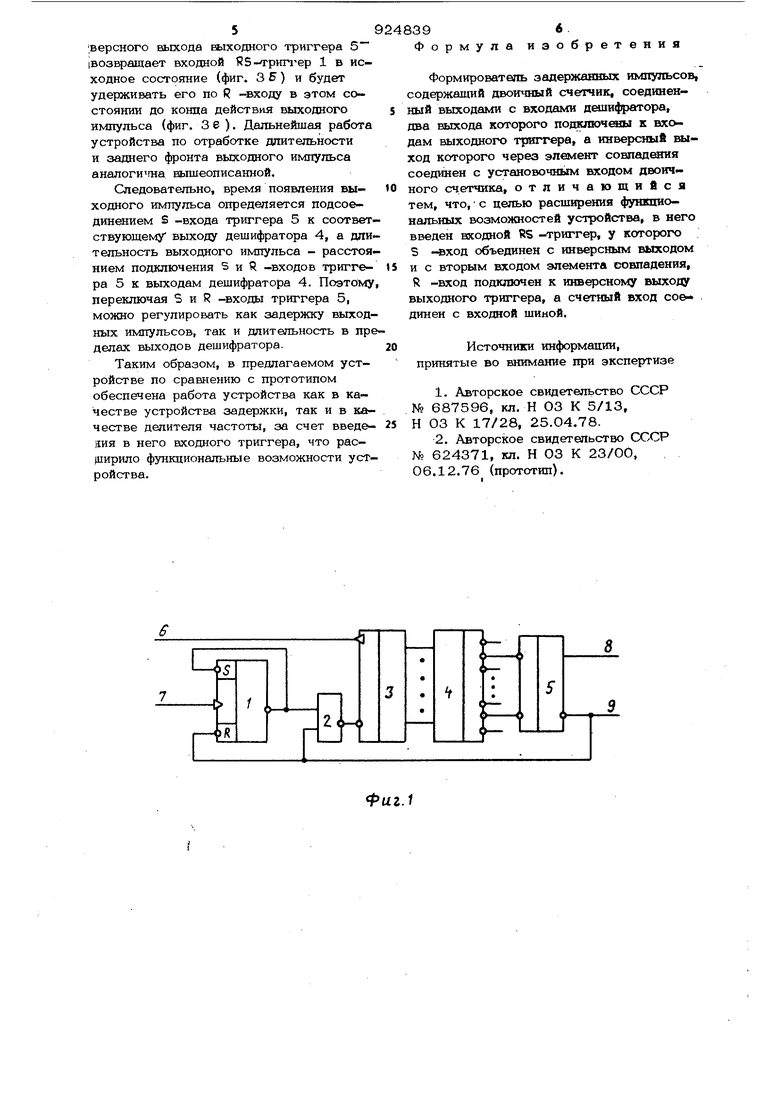

Изобретение относится к импульсной технике и может быть использовано в различных устройствах цифровой вычислительной техники в качестве устройства задержки импульсов. Известно устройство для задержки импульсов, содержащее тактовый генератор с подключенными к нему своими первыми входами вентилшхли, инвертор и счетный триггер, реверсивный счетчик, многонходовый вентиль, выходы которого соединены С суммирующим и вычитающим входами реверсивного счетчика, выходы посяег него подключены ко входам многонходово го вентиля, выход которого соединен с установочным входом счетного трип-ера, другой вход первого вентиля параллельно подключен к входной клемме и через инвертор к управл5пощим входам счетного триггера, неинвертирующий выход которого соединен с вторым входом другого вентиля 1 . Однако данное устройство имеет н&йостаточную надежность при работе с входными сигналами, имеющими различ ную длительность, и это ограничивает ето применение. Наиболее близким к предлагаемому 5тляется делитёль частоты с любым целочисленным коэффициентом деления, содержащзий два вентиля и инвертор ЕКОДЫ которых подключены к входной шине, выход первого вентиля соединен со счетным входом двоичного счетчика, выход второго вентиля - с его шиной сброса, выходы триггеров которого, соответствующие заданному коэффициенту деления, подключены ко входам дешифратора, и триггер управления, выходы последнего соединены с управлякмцими входами вентилей, дополнительный , входы которого соединены с нулевыми выходами триггеров двоичного счетчика, выход инвертора подключен к входам дешифраторов, выходы этих деигафраторов соединены с входами триггера управления 2 . Однако известный делитель частоты не может работать как устройство задержки. Цель изобретения - расширение функциональных возможностей устройства. Для достижения указанной цепи Е уст ройство, содержащее двоичный счетчик, соединенный выходами со входами дешиф ратора, два выхода которого подключены к входам выходного триггера, инверсный выход которого, через элемент совпадени соединен с установочным входом двоичного счетчика, введен нходной RS -тригг у которого S -вход объединен с инверсны выходом и с вторым входом элемента со падения, R -вход подключен к инверсном выходу выходного триггера, а счетный вход соединен с входной шиной. На фиг. 1 представлена функциональная схема устройства; на фиг. 2 и 3 временные диаграммы работы устройства. Формирователь задержанных импульсов содержит входной R5-триггер 1, элемент 2 совпадения, двоичный счетчик 3, дешифратор 4, выходной триггер 5, входные 6 и Т и выходные шины 8 и 9. . Устройство работает следующим образом. В исходном состоянии на входных шинах 6 и 7, на выходах элемента 2 совпадения, двоичного счетчика 3 и прямом выходе выходного триггера 5 (выходная шина 8) низкие уровни, а высокие уровни на инверсном выходе входного RS триггера 1, выходах дешифратора 4 и инверсном выходе выходного триггера 5 (выходная шина 9), С приходом входного асинхронного сигнала по шине 7 (фиг. 26) срабатывает входной триггер 1 (фиг. 2 g), в результате чего на выходе элемента 2 совпадения (фиг. 2t) появляется высок уровень, который разрешает двоичному счетчику 3 производить пересчет импуль сов тактовой частоты, поступающ 1х по шине 6 (фиг. 2 с(). Двоичный счетчик 3 просчитывает импульсы (фиг. 2S), каждое состо5шие которого дешифрируется дешифратором 4 (фиг. 2 е). Пусть, например, второй выход дешифратора 4 подключен к $ -входу выходного триггера, а седьмой - к 9 -входу. Следовательно, на выходных шинах 8 и 9 (фиг. 2 ж I i ) появляется передний фронт выходного импульса только после появления низкого уровня на втором вы ходе дешифратора 4 (фиг. 26), по которому выходной триггер 5 изменяет свое состояние. Низкий уровень инверсного ныхода триггера 5 (фиг. 2 3 ) всхзвращает входной R5-триггер 1 в исходное состо5шие (фиг. 2 6), При этом состояние выхода элемента 2 совпадения не изменяется (фиг. 2 г). Входной сигнал (фиг. 2 5) заканчивается, а в это время в двоичном счетчике 3 фиксируется пятое состояние. Окончание входного сигнала не оказывает действие на состояние элементов устройства. Двоичный счетчик 3 продолжает дальнейший пересчет Импульсов до седьмого состояния, по которому на седьмом выходе деши(|)- ратора 4 (фиг. 26) формируется низхшй уровень, который по В -входу устанавливает выходной триггер 5 в исходное состояние, формируя тем самым на выходных шинах 8 и 9 (фиг. 23) задний фронт выходных импульсов. Высокие уровни инверсных выходного и входного триггеров 5 и 1 проходят через элемент 2 совпадения, низким уровнем (фиг. 2 г) возвращают двоичный счетчик 3 в исходное состояние (фиг. 28), по которому седьмой выход дешифратора возвращается в исходное состояние. На этом процесс заканчивается, дальнейший приход входного очередного сигнала повторяет процесс работы. I Устройство может работать как и делитель частоты следования импульсов. Работа происходит следующим образом. В исходном положении состояние на шинах и выходах элементов устройства аналогичное исходному, описанному ранее. Импульсы тактовой частоты начинают поступать на шины 6 и 7 (фиг. За). По переднему фронту первого тактового импульса входной R5 -триггер 1 устанавливает на инверсном выходе низкий уровень (фиг. 35), который перекрывает элемент 2 совпадения (фиг. 3 и ) и разрешает пересчитывать двоичному счетчику 3 Импульсы тактовой частоты (фиг. 2 Я-). Низкий уровень инверсного выхода входного RS -триггера 1 удерживает трипер по 5 -входу в этом установившемся состоянии и поступающие последующие импульсы тактовой частоты по шине 7 не оказывают воздействия на входной триггер 1. Дешифратор 4 начинает дешифрировать состояние двои шого счетчика 3 (фиг. 35) и по низкому уровню соответствующего, например, второго выхода дешифратора 4 выходной триггер 5 формирует на выходных шинах 8 и S передний фронт выходных импульсов (фиг. 3 е , ). Низкий уровень miверсного выхода выходного триггера 5 |возвращает входной R 5-трип-ер 1 в исходное состояние (фиг. 35) и будет удерживать его по R -входу в этом состоянии до конца действия выходного импульса (фиг. 3 е ). Дальнейшая работа устройства по отработке длительности и заднего фронта выходного импульса аналогична вышеописанной.

Следовательно, время появления выходного импульса определяется подсоединением S -входа триггера 5 к соответствующему выходу дешифратора 4, а длительность выходного импульса - расстоянием подключения S и R -входов триггера 5 к выходам дешифратора 4. Поэтому, переключая S и R -входы триггера 5, можно регулировать как задержку выходных импульсов, так и длительность в пределах выходов дешифратора.

Таким образом, в предлагаемом устройстве по сравнению с прототипом обеспечена работа устройства как в качестве устройства задержки, так и в качестве делителя частоты, за счет введекия в него входного триггера, что расширило функциональные возможности устройства.

R

Формула изобретения

Формирователь задержанных импульсов содержащий двоичный счетчик, соединенный выходами с входами дш1Н(|ратора, два выхода которого пощключены к входам выходного триггера, а инверсный выход которого через элемент совпадения соед1шен с установочным входом двоичного счетчика, отличающийся тем, что, с целью расширения функциональных возможностей устройства, в него введен входной RS -триггер, у которого S -чзход объединен с инверсным выходом и с вторым входом элемента совпадения, R -вход подключен к инверсному выходу выходного триггера, а счетный вход соединен с входной шимой.

Источники информации, принятые во внимание при экспертизе

Н 03 К 17/28, 25.04.78.

fc-f

8

Фиг.1

а 6

д J

ж 3 5,9

fuz. 2 Я 5 г

Фиг.З 6,7 л 3

Авторы

Даты

1982-04-30—Публикация

1980-10-31—Подача