1

Изобретение относится к ядерному приборостроению и предназначено для отбора импульсов по амплитудам с де тектора ядерных излучений.

Известен многоканальный цифровой дискрис инатор, содержащий в каждом канале кольцевой десятиразрядный сдвиговый регистр, блок установки уровней анализа и блок ширины дифференциального окна, триггер и логические элементы И 1 .

Цифровой дискриминатор работает с временным преобразователем аналогкод и последующим запоминанием импульсов определенной частоты. Эти импульсы поступают на вход кольцевого сдвигового регистра в цифровом дискриминаторе. При помощи переключателей устанавливаются коды уровня дискриминации и ширины окна. Если количество импульсов, поступивших на вход сдвигового регистра лежит в пределах ширины окна, то на выходе дискриминатора появляется импульс, который записывается в определенный канал блока памяти информации. При помощи переключателей имеется возможность изменить уровень дискриминации и ширины окна. Тогда импульсы с выхода дискриминатора будут записываться в другие каналы блока памяти информации.

Недостаток этого устройства заключается в большом времени анализа.

Известен амплитудный дифференциальный дискриминатор, содержащий., генератор тактовых импульсов,регистр адреса цифровых окон,блок памяти

10 нижних и верхних порогов, блок памяти информации, два сумматора, блок отбора, амплитудно-цифровой преобразователь 2 .

Выходы регистра адреса цифровых

t5 подключены к адреснш4 входам блока памяти нижних и верхних порогов, выхода амплитудно-цифрового преобразователя подключены ко входгш обоих суквйаторов, к другим входгил

20 первого и второго сумматоров подключены соответственно выходы блока памяти нижних и верхних порогов, а выходы сумматоров подключены ко входам блока отбора, выход которюго

25 подключен к счетному входу блокапа14яти информации. Сначала амплитуда входного импульса анализируется на амплитудно-цифровом преобразователе, где определяется его цифровой код.

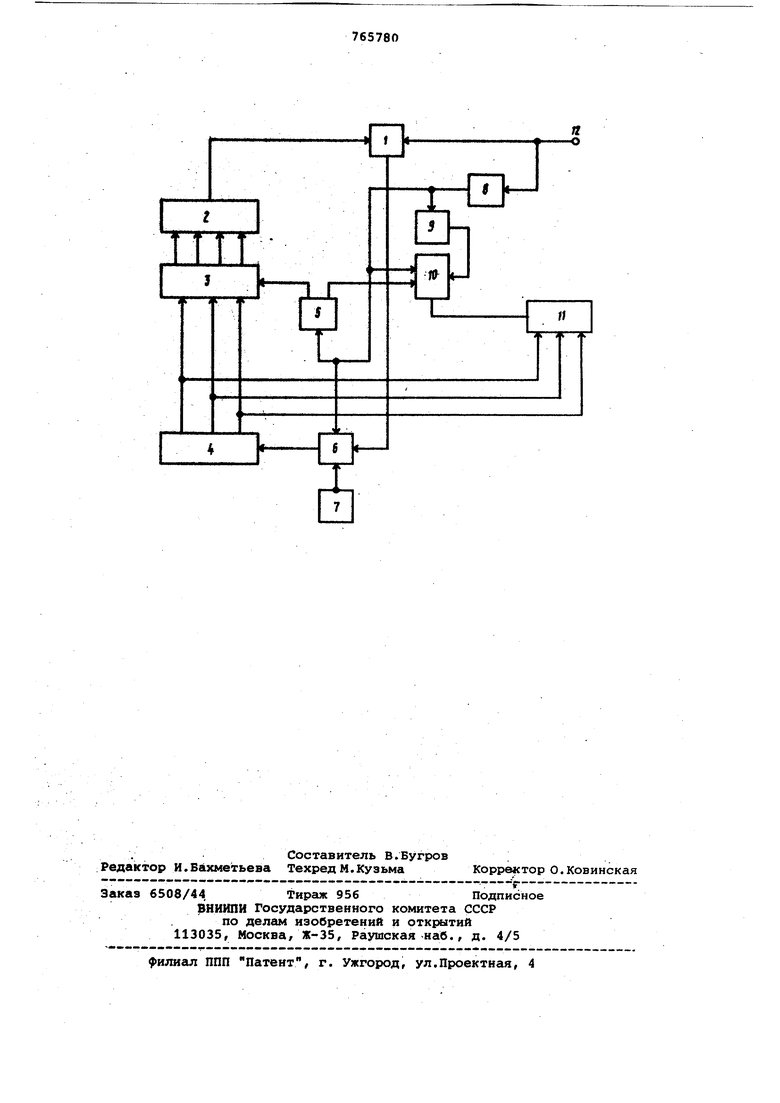

30 После этого происходит сравнение на сумматорах этого кода с кодами порогов. При этом регистр адреса цифровых окон ведет счет и на сумматоре последовательно, возбуждаются коды цифровых окон. Если код анализируемого импульса по величине находится между кодами нижнего и верхнего порогов цифрового окна, то блок передает в блок памяти информации импульсы записи. Недостатком этого устройства явля ется большое время анализа импульсов которое складывается из времени амплитудно-цифрового преобразования и времени сравнения кодов, а также сложность аппаратуры за счет влияния амплитудно-цифрового преобразователя многоразрядных сумматоров. Целью.изобретения является повыше ние быстродействия. Это достигается тем, что в амплитудный дифференциальный дискриминатор, содержащий генератор тактовых импульсов,регистр адреса цифровых окон,выходы которого соединены с адресными входами блока памяти нижних верхних порогов и блока памяти инфор мадии,введены компаратор,преобразова тель код аналог,триггер,формировател длительности импульса, блок опроса, элементы И, причем вход дискриминатора и выход преобразователя коданалог подключены ко входам компаратора, выходы компаратора формировате ля длительности ш шульса и генератора тактовых импульсов подключены ко входам первого элемента И, выход которого подключен ко входу регистра адреса цифровых окон, вход дискриминатора подключен ко входу формирователя длительности импульсов, выходы компаратора, блока опроса и триггера подключены ко входам второго элемента И, выход которого подключен к счетному входу блока памяти информации, выходы блока памяти нижних и верхних порогов подключены ко входам преобразователя код-аналог, выход формирователя длительности импульсов подключен ко входс1М триггера, и блока опроса, а выход триггера подключен к управляющему входу блока памяти нижних и верхних порогов. На чертеже изображена функциональ ная схема дискриминатора. Устройство компаратор 1 преобразователь 2, блок 3 памяти нижних и верхних порогов, регистр 4 адреса дифференциальных окон, триггер 5, первый элемент И б, генератор тактовых импульсов 7, формирователь 8 длительности импульса, блок опроса 9, второй элемент И 10, блок памяти информации 11, вход дискриминатора 12. Выход преобразователя код-аналог и вход дискриминатора 12 подключены ко входам компаратора 1, выходы компаратора 1, формирователя 8 длительности импульсов и генератора тактовых импульсов 7 подключены ко входам перового элемента И 6, выход которого подключен ко входу регистра 4 адреса дифференциальных окон. Вход дискриминатора 12 подключен ко входу формирователя 8 длительности импульсов . Выходы компаратора 1, блока опроса 9 и триггера 5 подключены ко вхоцам второго элемента И 10, выход которого подключен к счетному входу блока памяти информации 11. Выход формирователя Ь длительности импульсов подключен ко входам триггера 5 и блока опроса 9, а выход триггера 5 подключен к управляющему входу блока 3 памяти нижних и верхних порогов. Выходы регистра 4 адреса дифференциальных окон подключены к адресным входам блоков 3 памяти нижних и верхних порогов и информации 11, а выходы блока 3 памяти нижних и верхних порогов подключены ко входам преобразователя код-аналог 2, Устройство работает следующим образом. В начальный момент, при отсутствии анализируемых импульсов, регистр 4 адреса дифференциальных окон находится в таком состоянии, что выбирает первое дифференциальное окно из блока 3 памяти нижних и верхних порогов, а триггер 5 по управляющему входу выбирает верхний порог этого окна. Таким образом на вход преобразователя код-аналог 2 поступает цифровой код верхнего порога первого дифференциального окна,который преобразуется в аналоговую величину и с выхода преобразователя коданалог 2 поступает на вход компаратора 1. При поступлении анализируемого импульса на вход дискриминатора 12 срабатывает формирователь 8 длительности импульса, а амплитуда анализируемого импульса запоминается на компараторе на время анализа. На формирователе 8 длительности импульсов формируется прямоугольный импульс, Длительность котррого определяется временем анализа. Этот импульс отпирает первый элемент И б по одному из входов. Если амплитуда анализируемого импульса не превышает ригнал с выхода преобразователя код-аналог, то на выходе компаратора 1 присутствует сигнал запрета, который запирает эле менты И 6 и 10. После окончания импульса с выхода формирователе 8 длительности импульсов первый элемент И б запирается по соответствующему входу, а задним фронтом этого импульса переключается триггер 5 и запускается блок опроса 9. Триггер 5 отпирает второй элемент И 10 и по управляющему входу выбирает из блока 3 памяти нижних и верхних порогов нижний порог первого дифференциального окна. Величина этого порога на компараторе 1 сравнивается с амплитудой анализируемого импульса. Если амплитуда анализируемого импульса больше, то на выходе компаратора 1 появляется сигнал разрешения, который отпирает второй элемент И 10. Импульс с выхода блока опроса 9, который появляется с некоторой задержкой после его запуска, проходит через второй элемент И 10 и записывается в первом канале блока Памяти информации. Этот канал выбран регистром адреса дифференциальных окон.

Анализ заканчивается в случае, когда анализируемый импульс больше величины верхнего порога окна,на выходе компаратора 1 появляется разрешающий сигнал. Тогда первый элемент И б будет открыт по обоим входам и импульсы с выхода генератора 7 проходят на вход регистра 4 адреса дифференциальных окон и переключают его. Из блока 3 памяти нижних и верхних порогов последовательно выбираются коды верхних пороговых последующих окон и их аналоговые величины сравниваются с амплитудой анализируемого импульса. Это происходит до тех пор, пока величина порога не превысит амплитуду анализируемого импульса. После этого на выходе компаратора 1 появляется сигнал запрета. Переключение порогов прекращается.

Далее работа устройства происходит аналогично описанному случаю. То есть после окончания импульса с выхода формирователя длительности импульсов 8 происходит опрос нижнего порога выбранного окна и запись импульса в блоке памяти информации, если амплитуда анализируемого импульса превышает величину нижнего порога. Запись производится в канал, номер которого определяется состоянием регистра адреса дифференциальных окон 4.

Таким образом, происходит накопление информации в каналах блока памяти

информации, соответствующих определенным дифференциальным окнам, которые определяются блоком памяти нижних и верхних окон.

Формула изобретения

Амплитудный дифференциальный дискриминатор, содержащий генератор тактовых импульсов, регистр адреса цифровых окон, выходы которого соединены с адресными входами блока памяти нижних и верхних порогов и блока памяти информации, отличающийся тем, что, с целью повыше5ния быстродействия в него введены компаратор, преобразователь код-аналог, триггер, формирователь длительности импульса, блок опроса, элементы И, причем вход дискриминатора

0 и выход преобразователя код-аналог подключены ко входам компаратора, выходы колшаратора формирователя длительности импульса и генератора тактовых импульсов подключены ко входам первого элемента И, выход которого

5 подключен ко входу регистра адреса цифровых окон, вход дискриминатора подключен ко входу формирователя длительности импульсов, выходы компаратора, блока опроса и триггера

0 подключены ко входам второго элемента И, выход которого подключен к счетному входу блока памяти информации, выходы блока памяти нижних и верхних порогов подключены ко вхо5дам преобразователя код-аналог, выход формирователя длительности импульсов подключен ко входам триггера и блока опроса, а выход триггера подключен к управляквдему вхо0ду блока памяти нижних и верхних порогов.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 378859, кл. G Об F 15/36, 1971.

5

2.Соучек Б. в системах обработки информации, М., иэд. Мир, 1976, с.461 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для амплитудного анализа импульсов | 1980 |

|

SU938176A1 |

| Устройство для амплитудного анализа | 1981 |

|

SU1073886A1 |

| УСТРОЙСТВО МОНИТОРИНГА ИНФОРМАЦИОННОГО ТРАФИКА | 2021 |

|

RU2768543C1 |

| Устройство для определения временного положения сигнала | 1985 |

|

SU1307442A1 |

| ЦИФРОВОЙ ДАЛЬНОМЕР | 1992 |

|

RU2069003C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1999 |

|

RU2149446C1 |

| Устройство для считывания графической информации | 1987 |

|

SU1506460A1 |

| Преобразователь кода в аналог | 1973 |

|

SU651474A1 |

| Устройство для определения времени фибринолизиса | 1985 |

|

SU1323566A1 |

| СПОСОБ И УСТРОЙСТВО СЕЛЕКЦИИ СИГНАЛОВ НАДВОДНОЙ ЦЕЛИ В МОНОИМПУЛЬСНОЙ РЛС | 2004 |

|

RU2278397C2 |

Авторы

Даты

1980-09-23—Публикация

1978-08-25—Подача