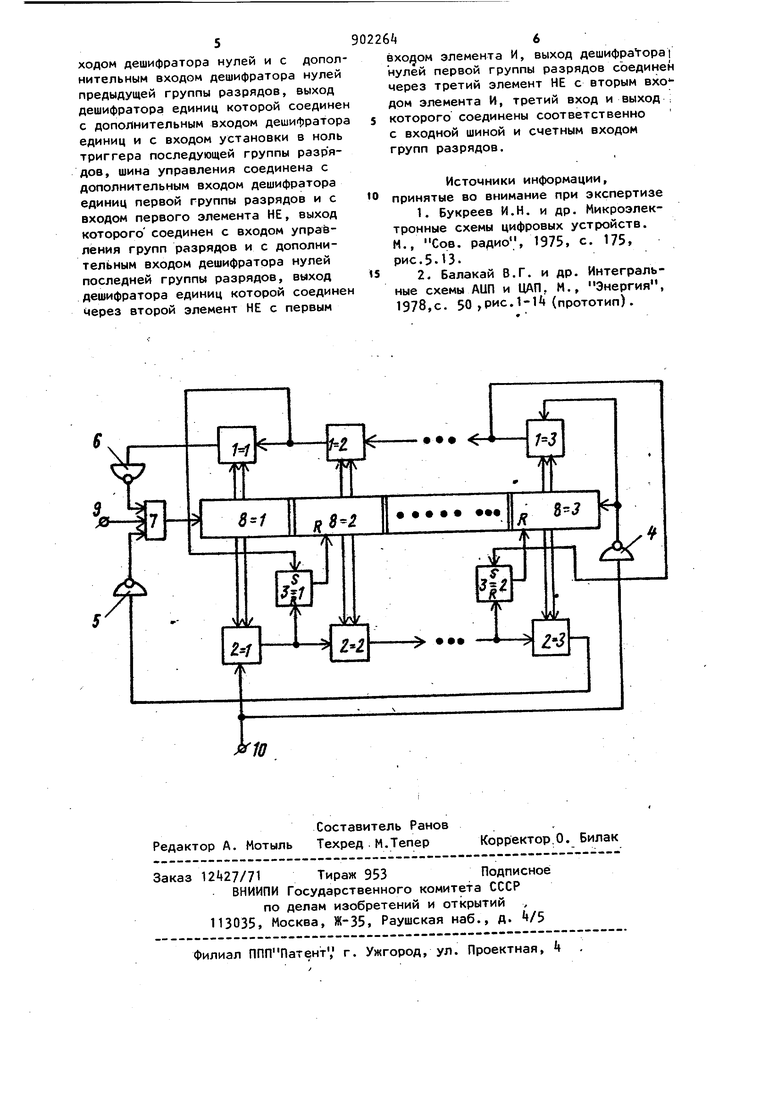

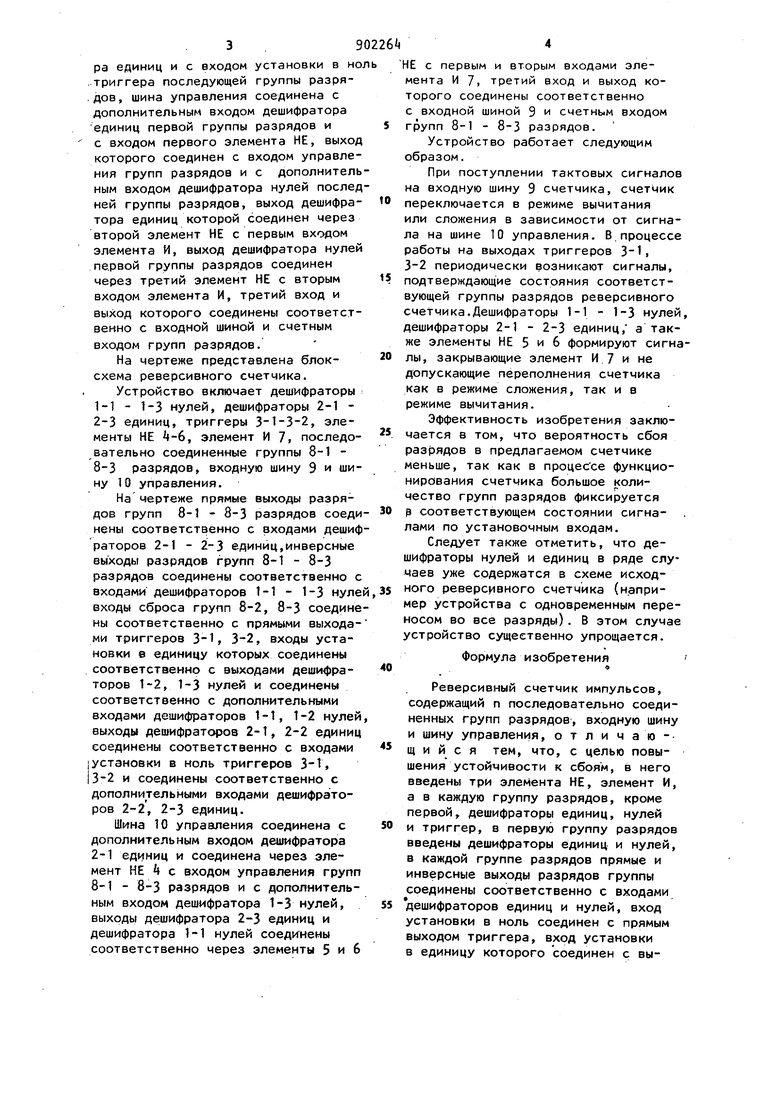

(5) РЕВЕРСИВНЫЙ СЧЕТЧИК Изобретение относится к автоматике и вычислительной технике и может быть использовано при реализации технических средств в этих областях. Известен реверсивный счетчик импульсов, содержащий входную шину, шину управления и последовательно соединенные разряды 1. Недостаток известного устройства относительно низкая помехоустойчивость. Известен реверсивный счетчик импульсов, содержащий п последовательно соединенных групп разрядов, счетный вход и вход управления кото рых соединены соответственно с входной шиной и шиной управления 2 Недостатком известного устройства является низкая помехоустойчивость, связанная с тем, что в резул тате сбоя элементы памяти могут изменить свое состояние. Цель изобретения - повышение устойчивости к сбоям. Поставленная цель достигается тем, что в реверсивный счетчик, содержащий п последовательно соединенных групп разрядов, входную шину и шину управления, введены три элемента НЕ, элемент И, а в каждую группу разрядов, кроме первой, дешифраторы единиц, нулей и триггер, в первую группу разрядов введены дешифраторы единиц и нулей, в каждой группе разрядов прямые и инверсные выходы разрядов группы соединены соответственно с входами дешифраторов единиц и нулей, вход установки в ноль соединен с прямым выходом триггера, вход установки в единицу которого соединен с выходом дешифратора нулей и с дополнительным входом дешифратора нулей предыдущей группы разрядов, выход дешифратора единиц которой соединен с дополнительным входом дешифрато39pa единиц и с входом установки в но ..триггера последующей группы разря.дов, шина управления соединена с дополнительным входом дешифратора единиц первой группы разрядов и с входом первого элемента НЕ, выход которого соединен с входом управления групп разрядов и с дополнитель ным входом дешифратора нулей послед ней группы разрядов, выход дешифра тора единиц которой соединен через второй элемент НЕ с первым входом элемента И, выход дешифратора нулей первой группы разрядов соединен через третий элемент НЕ с вторым входом элемента И, третий вход и выход которого соединены соответственно с входной шиной и счетным входом групп разрядов. На чертеже представлена блоксхема реверсивного счетчика. Устройство включает дешифраторы 1-1 - 1-3 нулей, дешифраторы 2-1 2-3 единиц, триггеры 3-1-3-2, элементы НЕ 4-6, элемент И 7, последо вательно соединенные группы 8-1 8-3 разрядов, входную шину 9 и ши ну 10 управления. На чертеже прямые выходы разрядов групп 8-1 - 8-3 разрядов соед иены соответственно с входами дешиф раторов 2-1 - 2-3 единиц,инверсные выходы разрядов групп 8-1 - 8-3 разрядов соединены соответственно входами дешифраторов 1-1 - 1-3 нул входы сброса групп 8-2, 8-3 соедин ны соответственно с прямыми выхода ми триггеров , , входы установки в единицу которых соединены соответственно с выходами дешифраторов 1-2, 1-3 нулей и соединены соответственно с дополнительными входами дешифраторов t-1, 1-2 нуле выходы дешифраторов 2-1, 2-2 едини соединены ссютветственно с входами установки в ноль триггеров . |3-2 и соединены соответственно с дополнительными входами дешифраторов 2-2, 2-3 единиц. Шина 10 управления соединена с дополнительным входом дешифратора 2-1 единиц и соединена через элемент НЕ i с входом управления груп 8-1 - 8-3 разрядов и с дополнитель ным входом дешифратора 1-3 нулей, выходы дешифратора 2-3 единиц и дешифратора 1-1 нулей соединены соответственно через элементы 5 и Е с первым и вторым входами элемента И 7) третий вход и выход которого соединены соответственно с входной шиной 9 и счетным входом групп 8-1 - 8-3 разрядов. Устройство работает следующим образом. При поступлении тактовых сигналов на входную шину 9 счетчика, счетчик переключается в режиме вычитания или сложения в зависимости от сигнала на шине 10 управления. В процессе работы на выходах триггеров , 3-2 периодически возникают сигналы, подтверждающие состояния соответствующей группы разрядов реверсивного счетчика.Дешифраторы 1-1 - 1-3 нулей, дешифраторы 2-1 - 2-3 единиц, а также элементы НЕ 5 и 6 формируют сигналы, закрывающие элемент И.7 и не допускающие переполнения счетчика как в режиме сложения, так и в режиме вычитания. Эффективность изобретения заключается в том, что вероятность сбоя разрядов в предлагаемом счетчике меньше, так как в процессе функционирования счетчика большое количество групп разрядов фиксируется Э соответствующем состоянии сигналами по установочным входам. Следует также отметить, что дешифраторы нулей и единиц в ряде случаев уже содержатся в схеме исходного реверсивного счетчика (например устройства с одновременным переносом во все разряды). В этом случае устройство существенно упрощается. Формула изобретения Реверсивный счетчик импульсов, содержащий п последовательно соединенных групп разрядов, входную шину и шину управления, отличающийся тем, что, с целью повышения устойчивости к сбоям, в него введены три элемента НЕ, элемент И, а в каждую группу разрядов, кроме первой, дешифраторы единиц, нулей и триггер, в первую группу разрядов введены дешифраторы единиц и нулей, в каждой группе разрядов прямые и инверсные выходы разрядов группы соединены соответственно с входами дешифраторов единиц и нулей, вход установки в ноль соединен с прямым выходом триггера, вход установки в единицу которого соединен с выходом дешифратора нулей и с дополнительным входом дешифратора нулей предыдущей группы разрядов, выход дешифратора единиц которой соединен с дополнительным входом дешифратора единиц и с входом установки в ноль триггера последующей группы разрядов, шина управления соединена с дополнительным входом дешифратора единиц первой группы разрядов и с входом первого элемента НЕ, выход которого соединен с входом управления групп разрядов и с дополнительным входом дешифратора нулей последней группы разрядов, выход дешифратора единиц которой соединен Через второй элемент НЕ с первым

90226i 6

входом элемента И, выход дeшифpaYopa| нулей первой группы разрядов соединен через третий элемент НЕ с вторым входом элемента И, третий вход и выход 5 которого соединены соответственно с входной шиной и счетным входом групп разрядов.

Источники информации, принятые во внимание при экспертизе

1.Букреев И.Н. и др. Микроэлектронные схемы цифровых устройств. М.. Сое. радио, 1975, с. 175, рис.5.13.

2.Балакай В.Г. и др. Интегральные схемы AUn и ЦАП. М., Энергия, 1978,с. 50 ,рис. 1-14 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный двоичный счетчик с обнаружением ошибок | 1981 |

|

SU1019641A1 |

| Счетное устройство | 1979 |

|

SU864585A1 |

| Счетчик джонсона | 1979 |

|

SU809582A1 |

| Кольцевой счетчик | 1979 |

|

SU807493A1 |

| Устройство для извлечения квадратного корня | 1977 |

|

SU714394A1 |

| Синхронное устройство управления | 1980 |

|

SU935957A1 |

| Устройство для возведения в квадрат чисел,представленных в унитарном коде | 1976 |

|

SU660045A1 |

| Счетное устройство по модулю три с контролем | 1983 |

|

SU1190518A1 |

| Устройство для контроля работы синхронного автомата | 1980 |

|

SU907809A1 |

| Устройство для возведения в квадрат чисел, представленных в унитарном коде | 1980 |

|

SU920715A1 |

Авторы

Даты

1982-01-30—Публикация

1980-06-18—Подача