1

Изобретение относится к области вычислительной техники и может найти широкое применение в специализированных вычислительных устройствах дискретного действия и электроизмерительных приборах.

Известно устройство для возведения в квадрат числа, представленного в унитарном коде, содержащее два сумматора, два счетчика, элементы И и триггер 1.

Недостатком его являются сравнительно большие затраты оборудования на реализацию устройства.

Наиболее близким к изобретению является устройство для возведения в квадрат чисел, представленных в унитарном коде, содержащее сумматор, счетчик, группу элементов И, элемент ИЛИ, элемент задержки и дискриминатор четности, состоящий из триггера, прямой выход которого через первый и второй элементы И связан с первым и вторым выходами дискриминатора четности, а инверсный выход через третий и четвертый элементы И - с третьим и четвертым выходами дискриминатора четности, причем другие входы первого и третьего элементов И соединены с первым входом дискриминатора четности, а другие входы второго и четвертого элементов И- со вторым входом дискриминатора четности, выходы первого и третьего элементов

И соединены соответственно со входами установки триггера дискриминатора четности в единичное и нулевое состояние, первый выход дискриминатора четности соединен со счетным входом счетчика, третий и четвертый выходы дискриминатора четности соединены с входами элемента ИЛИ, второй вход дискриминатора четности через элемент задержки связан с управляющим

входом сумматора и с управляющим входом устройства, первые входы группы элементов И соединены с выходом элемента ИЛИ, вторые входы - с выходами разрядов счетчика, а выходы - со входами разрядов сумматора, начиная с третьего 2.

Недостатком этого устройства является сравнительно низкое быстродействие.

Целью изобретения является повышение быстродействия.

Поставленная цель достигается тем, что в устройство введены делитель частоты, состоящий из счетного триггера и элемента И, вторая группа элементов И, второй элемент задержки, второй элемент ИЛИ, пятый и щестой элементы И, причем вход устройства подключен ко входу делителя частоты, который соединен со счетным входом счетного триггера и первым входом элемента И делителя частоты, второй вход

элемента И делителя частоты подключен

к прямому выходу счетного триггера, а выход - к выходу делителя частоты, который соединен с нервым входом дискриминатора четности, нрямой выход счетного триггера нодключсн также к первому входу нятого элемента И и к выходу первого разряда устройства, второй вход нятого элемента И через второй элемент задержки подключен к выходу первого элемента задержки, а выход - к первому входу шестого элемента И и к нервым входам элементов И второй грунны, второй вход шестого элемента И соединен с прямым выходол триггера дискриминатора четности, а выход - через второй элемент ИЛИ со-вместно со вторым выходом дискриминатора четности соединен со входом первого разряда сумматора, выходы разрядов счетчнка соединены с вторыми входами элементов И второй группы, выходы которых соединены со входами разрядов сумматора, начиная со второго, выход второго разряда устройства подключен к шине логического нуля, выходы разрядов сумматора являются вв1ходами разрядов устройства, начиная с третьего.

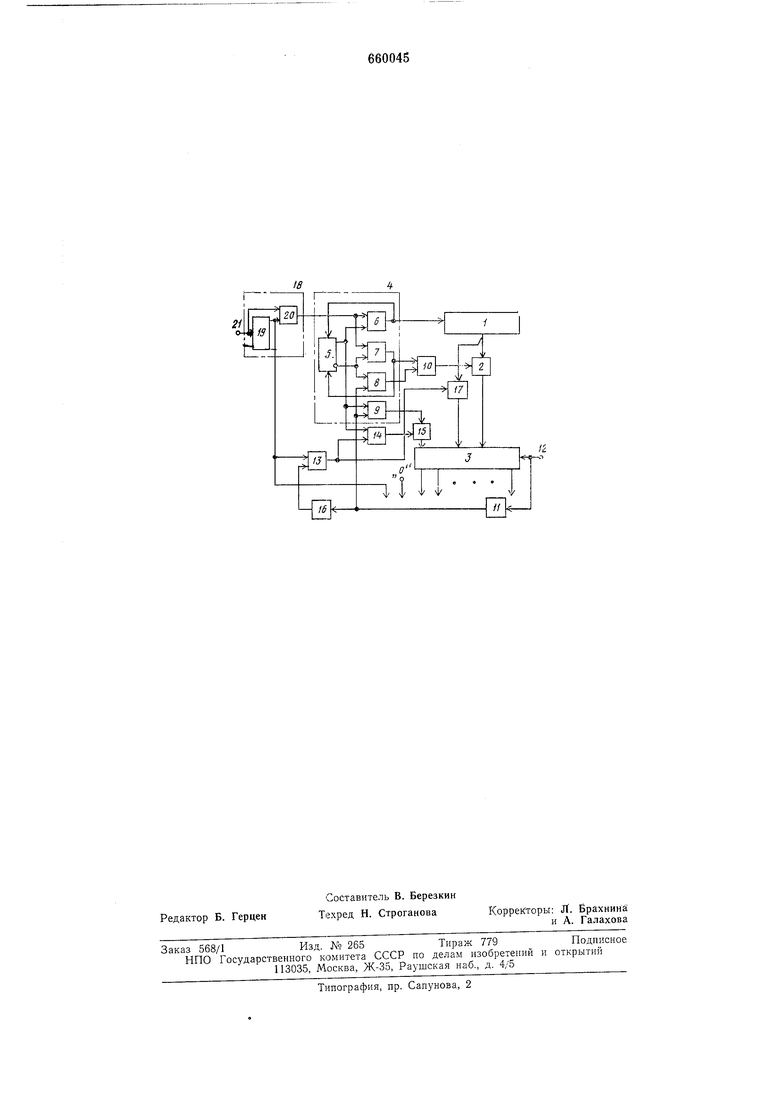

стройство, предетавленное на чертеже, содержит счетчик 1, группу 2 элементов И, сумматор 3, дискри.минатор 4 четности, триггер о, элементы И 6, 7, 8, 9, элемент ИЛИ 10, элемент И задержки, унравляюн;нй вход 12 устройства, элементы И 13 и 4, элемент ИЛИ 15, элемент 16 задержки, грунну 17 элементов И, делитель 18 частоты, содержащий счетный триггер 19 и эле.мент И 20, вход 21 уетройства.

Устройство работает следуюш,им образом. Возводимое в квадрат число импульсов поступает на вход 21 устройства.

Зту последовательность и импульсов можно представить в виде

/r.,2+...-f а„2«,

где cii - член носледовательности, принимаюпднй значение ноль или единица при t 0, 1, 2, ... п. После деления входной последовательности на делителе частоты 18 на его выходе образуется последовательность иАтнульсов, равная

паа

22

Тогда

/г ао -f 2/7.,. Возведем обе части равенства в квадрат:

п г.: (а, + 2л,) - al + 4ao«i + 4« Для п четных ао 0,

т. е. п гг: ф-г,(I)

для п нечетных ,

т. е. п 1 + 4/г, + Ап,(2)

Если подать п на вход устройства, в сумматоре зафиксируется:

Д -1-г4Г2,(3)

L -J

для п нечетных н п четных имиульсов;

n-l-f (4)

для п нечетиых и HI нечетных.

Учитывая выражения (1), (3), (4) работу устройства можно представить в виде зависимости

I i

Я.: .

(5)

2 «j-l

1+4J2

для п четных

для п нечетных, HI четных для п нечетных, п четных

Перед началом работы все элементы, обладающие памятью, сбрасываются в нулевое состояние.

После деления на два, осуществляемое в делителе 18 частоты, носледовательность п

нмну.тьсов постунает на вход дискриминатора 4 четности, который выделяет на элементах И 7 и ИЛИ 10 нечетные имнульсы, ностунающие на унравляющий вход группы 2 элементов И, что ос}чцествляет перенос кода счетчика 1 в сумматор 3, а четные импульсы, формируемые в дискриминаторе 4 на элементе И 6, поступают на вход счетчнка 1. После прохождения последовательности импульсов выделяется сигнал конна

последовательности, который удваивает число в сумматоре 3 и, если носледовательность «1 четная, т. е. триггер 5 находится в состоянии «единица, прибавляет к содержимому сумматора 3 значеине счетчика

1 путем заниси его через груину 17 элементов И импульсом конца носледовательности, проходящим но цени первого н второго элементов 11 и 16 задержки и элемента И 13, открытого триггером 19.

Если же последовательность «i имиульсов нечетная, то импульс конца последовательности нройдя но цепи элементов 11 задержки, И 9, ИЛИ 15 поступит на вход первого разряда сумматора и прибавит

единицу к его содержимому.

Таким образом, в сумматоре фиксируется код числа п, а в счетчике код числа

п,til - I

- .

22

При вышеприведепных вычислениях (5), обеспечиваемых при четном п счетным триггером 19, который находится в нулевом состоянии, закрывающем элемент И 13, в сумматоре фиксируется значение

так как суммирование значения содержимого счетчика производится со сдвигом на три разряда влево.

Если последовательность п нечетная, а «1 - четная, то элемент И 13 открыт, и сумматор 3 фиксирует значение, определяемое зависимостью (5)

+п .

2

При нечетных последовательностях п и rti дополнительно открыт элемент И 14 и имнульс конца носледовательности, пройдя элемент ИЛИ 20, прибавляется к содержимому сумматора:

1 . 2|

1 +4Г1+2 -+П1

При возведении любого числа в квадрат, второй его разряд всегда содержит ноль, так как

(ао2 + а,2Ч-...+а„2)

где flj О или 1 при 1 О, 1, 2, ... п.

Раскрывая скобки и собирая члены при 2, получим

аоа,2 + аоа,,2

Исходя из изложенного, выход второго разряда устройства подключен к шине логического нуля, а первый разряд устройства соединен с выходом триггера четности делителя частоты.

Введение делителя частоты, элементов И, ИЛИ с их связями, позволило уменьшить частоту поступления импульсов на счетчик 1, исключить при этом один разряд счетчика 1 и уменьшить разрядность сумматора за счет замены его первых разрядов значением триггера четности и логического нуля, что позволило повысить обш,ее быстродействие устройства и расширить диапазон воспроизводимой им функции.

Формула изобретения

Устройство для возведения в квадрат чисел, представленных в унитарном коде, содержашее сумматор, счетчик, группу элементов И, элемент ИЛИ, элемент задержки и дискриминатор четности, состоящий из триггера, прямой выход которого через первый и второй элементы И связан с первым и вторым выходами дискриминатора четности, а инверсный выход через третий и четвертый элементы И - с третьим и четвертым выходами дискриминатора четности, причем другие входы первого и третьего элементов И соединены с первым входом дискриминатора четности, а другие входы второго и четвертого элементов

И - со вторым входом дискриминатора четности, выходы первого н третьего элементов И соединены соответственно со входами установки триггера дискриминатора четности в единичное и нулевое состояние, nepBbiji выход дискриминатора четности соединен со счетным входом счетчика, третий и четвертый выходы дискриминатора четности соединены с входами элемента

ИЛИ, второй вход дискриминатора четности через элемент задерл ки связан с управляющим входом сумматора и с управляющим входом устройства, первые входы группы элементов И соединены е выходом

элемента ИЛИ, вторые входы - с выходами разрядов счетчика, а выходы - со входами разрядов сумматора, начиная с третьего, отличающееся тем, что, с целью увеличения быстродействия, в устройство

введены делитель частоты, состоящий из счетного триггера и элемента И, вторая группа элементов И, второй элемент задержки, второй элемент ИЛИ, пятый и шестой элементы И, причем вход устройства

подключен ко входу делителя частоты, который соединен со счетным входом счетного триггера и нервым входом элемента И делителя частоты, второй вход элемента И делителя частоты подключен к прямому

выходу счетного триггера, а выход - к выходу делителя частоты, который соединен с первым входом дискриминатора четности, прямой выход счетного триггера нодключен также к первому входу пятого элемента И п к выходу первого разряда устройства, второй вход пятого элемента И через второй элемент задержки подключен к выходу первого элемента задержки, а выход- к первому входу щестого элемента Инк

первым входам элементов И второй группы, второй вход щеетого элемента И соединен с прямым выходом триггера дискриминатора четности, а выход - через второй элемент ИЛИ совместно со вторым выходом дискриминатора четности соединен со входом первого разряда сумматора, выходы разрядов счетчика соединены с вторыми входами элементов И второй группы, выходы которых соединены со входами

разрядов сумматора, начиная со второго, выход второго разряда устройства подключен к щине логического нуля, выходы разрядов сумматора являются выходами разрядов устройства, начнная е третьего.

Источники информации,

принятые во внимание при экспертизе

1.Авторское свидетельство СССР 475619, кл. G 06F 7/38, 1973.

2.Авторское свидетельство СССР Л 397907, кл. G 06F 7/38, 1971.

i

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения квадратного корня | 1976 |

|

SU613321A1 |

| УСТРОЙСТВО для ВОЗВЕДЕНИЯ В КВАДРАТ ЧИСЕЛ, ПРЕДСТАВЛЕННЫХ В УНИТАРНОМ КОДЕ | 1973 |

|

SU397907A1 |

| СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ТЕЛЕВИЗИОННЫХ СИГНАЛОВ | 1991 |

|

RU2014745C1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1160560A1 |

| Устройство для определения максимальной гармоники спектра Уолша | 1984 |

|

SU1211751A1 |

| Устройство для возведения в квадрат чисел, представленных в унитарном коде | 1980 |

|

SU920715A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1988 |

|

SU1606996A1 |

| ЦИФРОВАЯ СИСТЕМА РАДИОВЕЩАНИЯ | 1992 |

|

RU2048704C1 |

| Устройство для контроля параллельного кода на четность | 1987 |

|

SU1413632A1 |

| УСТРОЙСТВО для ВОЗВЕДЕНИЯ В КВАДР.'М ЧИС-ЛА, ПРЕДСТАВЛЕННОГО В УНИТАРНОЛ! КОДЕ | 1970 |

|

SU269603A1 |

Авторы

Даты

1979-04-30—Публикация

1976-03-23—Подача