(54) СИНХРОННОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный счетчик | 1980 |

|

SU902264A1 |

| Устройство для сравнения двоичных чисел | 1979 |

|

SU798816A1 |

| Устройство для контроля работыСиНХРОННОгО ABTOMATA | 1979 |

|

SU840910A1 |

| Счетное устройство | 1979 |

|

SU864585A1 |

| Счетчик джонсона | 1979 |

|

SU809582A1 |

| Синхронное дискретное устройство | 1987 |

|

SU1786488A1 |

| Кольцевой счетчик | 1979 |

|

SU807493A1 |

| Устройство для возведения в квадрат чисел,представленных в унитарном коде | 1976 |

|

SU660045A1 |

| Реверсивный двоичный счетчик с обнаружением ошибок | 1981 |

|

SU1019641A1 |

| Устройство для извлечения квадратного корня | 1977 |

|

SU714394A1 |

1

Изобретение относится к вычислительной технике и может быть использовано при построении помехоустойчивых вычислительных устройств.

Известно вычислительное устройство последовательного действия, содержащее входные и выходные шины, триггеры памяти и комбинационные цепи LI.

Наиболее близким к изобретению является синхронное вычислительное устройство, содержащее блок формирования состояний и выходных сигналов, имеющий внешние три входные и выходные шины, три внутренних установочных входа, три внутренних установочных выхода, три триггера пaмяtи, информационные входы которых соединены с соответствующими установочными выходами, а информационные выходы - с соответствующими установочными входами блока формирования состояний и выходных сигналов, цепь синхронизации.

соединяющую синхронизирующие входы первого, второго и третьего триггеров памяти С21.

Недостатком известного устройства является низкая устойчивость к сбоям триггеров памяти.

Цель изобретения - повышение надежности устройства.

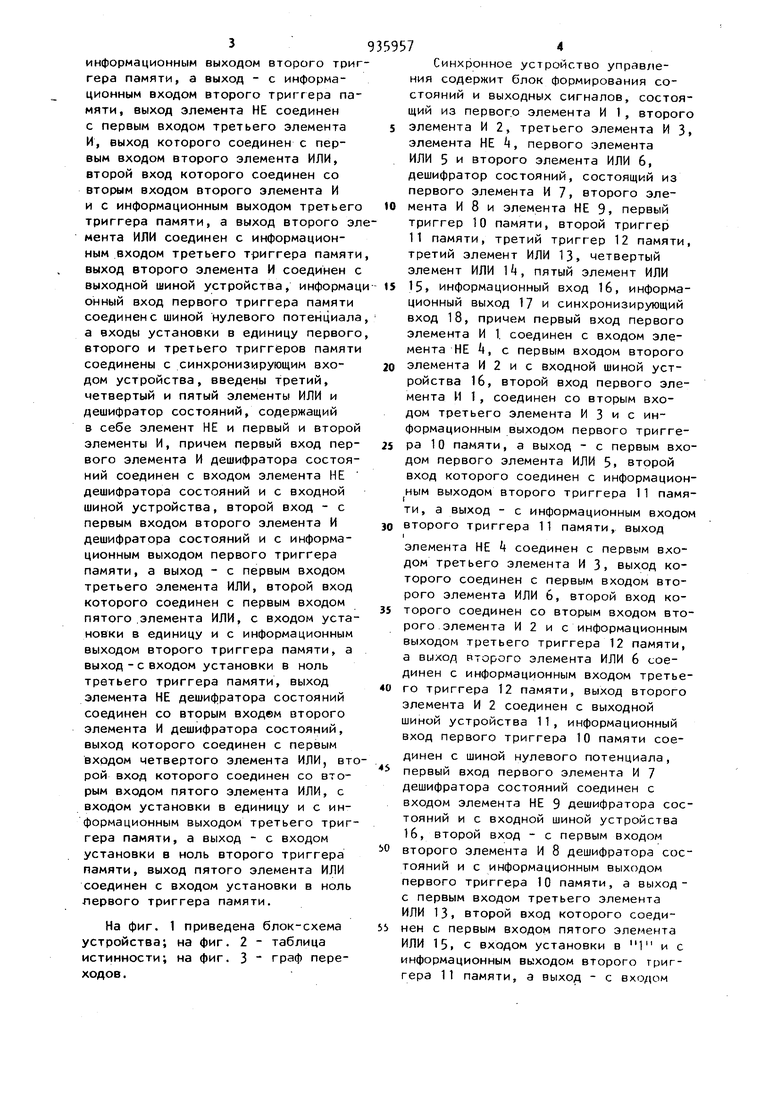

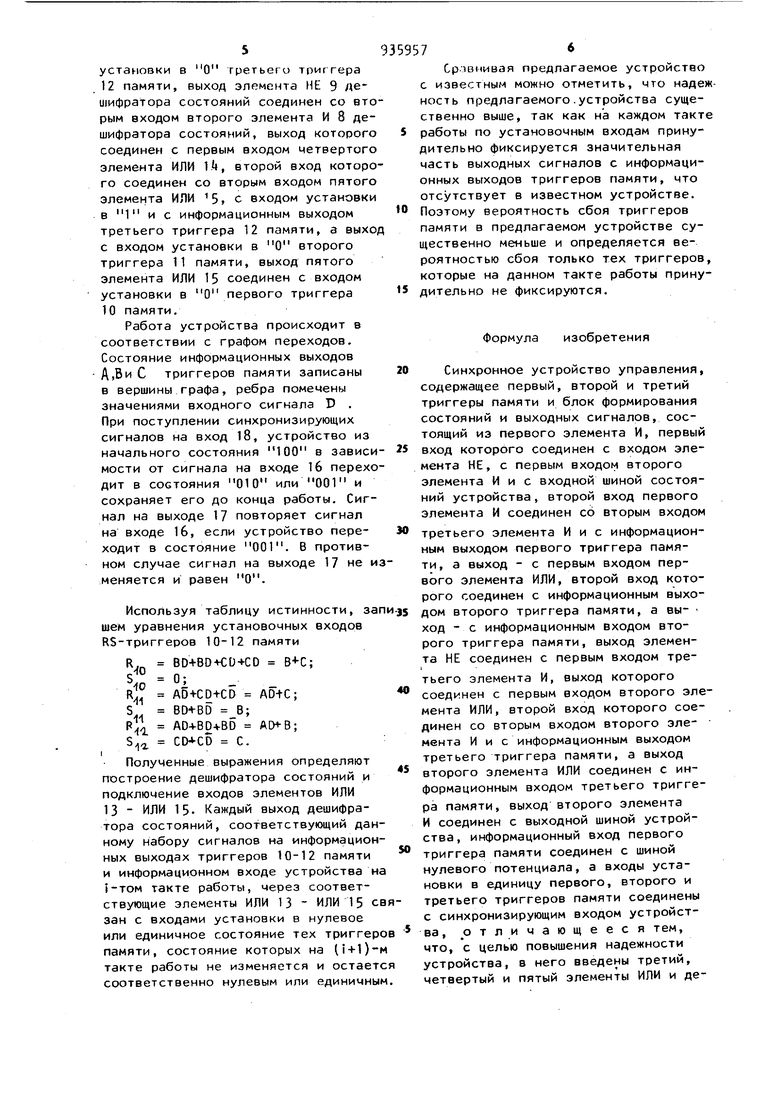

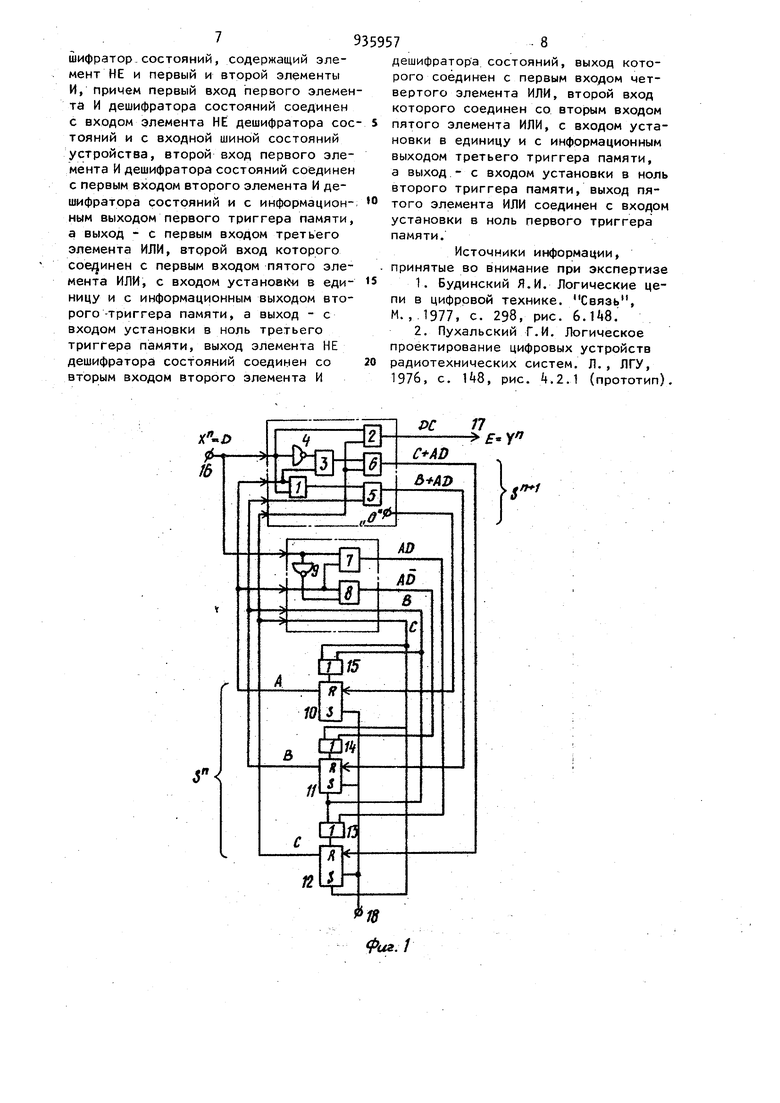

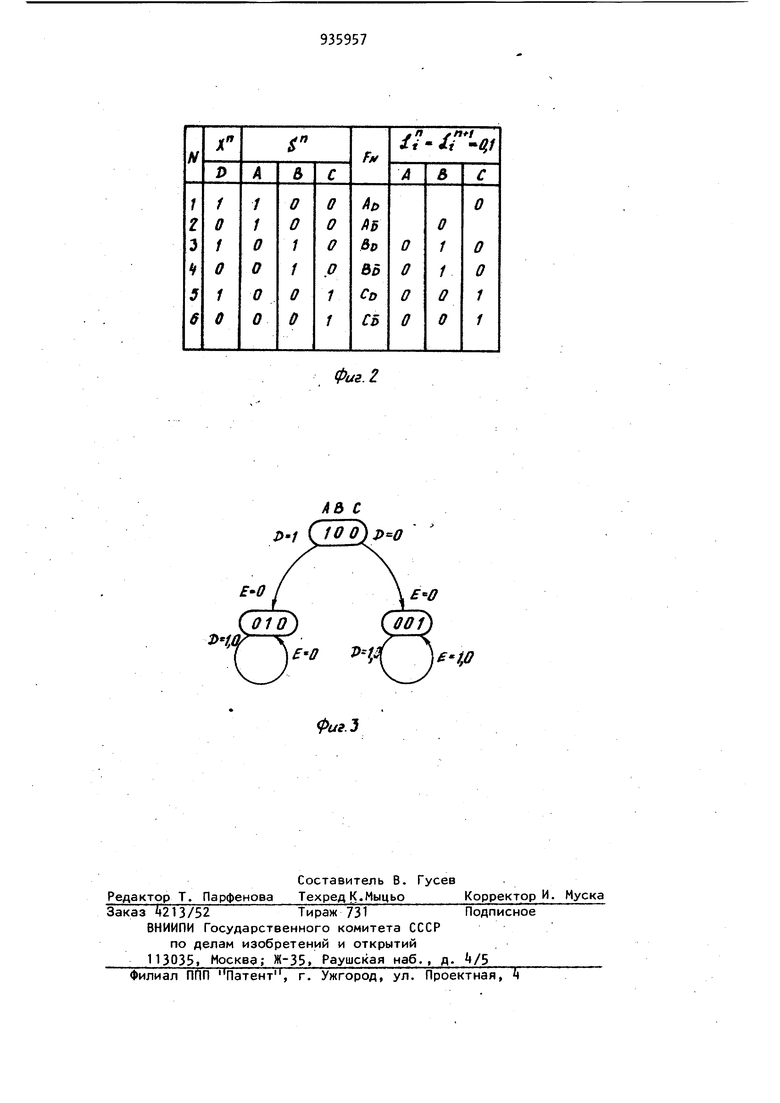

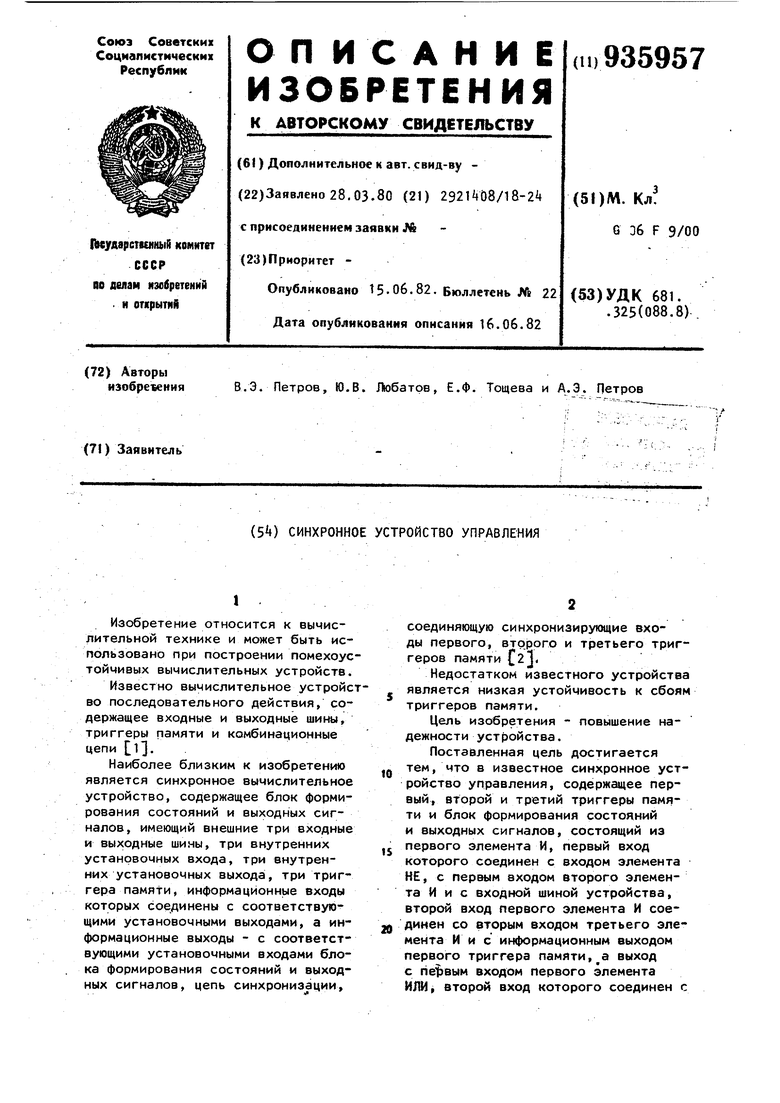

Поставленная цель достигается тем, что в известное синхронное устройство управления, содержащее первый, второй и третий триггеры памяти и блок формирования состояний и выходных сигналов, состоящий из первого элемента И, первый вход которого соединен с входом элемента НЕ, с первым входом второго элемента И и с входной шиной устройства, второй вход первого элемента И соединен со вторым входом третьего элемента И и с информационным выходом первого триггера памяти,а выход с входом первого элемента ИЛИ, второй вход которого соединен с 3 информационным выходом второго три гера памяти, а выход - с информационным входом второго триггера па мяти, выход элемента НЕ соединен с первым входом третьего элемента И, выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен со вторым входом второго элемента И и с информационным выходом третьег триггера памяти, а выход второго э мента ИЛИ соединен с информационным входом третьего триггера памят выход второго элемента И соединен выходной шиной устройства, информа онный вход первого триггера памяти соединен с шиной нулевого потенциал а входы установки в единицу первог второго и третьего триггеров памят соединены с синхронизирующим входом устройства, введены третий, четвертый и пятый элементы ИЛИ и дешифратор состояний, содержащий в себе элемент НЕ и первый и второ элементы И, причем первый вход пер вого элемента И дешифратора состоя ний соединен с входом элемента НЕ дешифратора состояний и с входной шиной устройства, второй вход - с первым входом второго элемента И дешифратора состояний и с информационным выходом первого триггера памяти, а выход - с первым входом третьего элемента ИЛИ, второй вход которого соединен с первым входом пятого .элемента ИЛИ, с входом уста новки в единицу и с информационным выходом второго триггера памяти, а выход - с входом установки в ноль третьего триггера памяти, выход элемента НЕ дешифратора состояний соединен со вторым входем второго элемента И дешифратора состояний, выход которого соединен с первым входом четвертого элемента ИЛИ, вт рой вход которого соединен со вторым входом пятого элемента ИЛИ, с входом установки в единицу и с информационным выходом третьего триг гера памяти, а выход - с входом установки в ноль второго триггера памяти, выход пятого элемента ИЛИ соединен с входом установки в ноль лервого триггера памяти. На фиг. 1 приведена блок-схема устройства; на фиг, 2 - таблица истинности; на фиг. 3 граф переходов . 7 Синхронное устройство управления содержит блок формирования состояний и выходных сигналов, состоящий из первого элемента И 1, второго элемента И 2, третьего элемента И 3, элемента НЕ k, первого элемента ИЛИ 5 и второго элемента ИЛИ 6, дешифратор состояний, состоящий из первого элемента И 7, второго элемента И 8 и элемента НЕ 9, первый триггер 10 памяти, второй триггер 11 памяти, третий триггер 12 памяти, третий элемент ИЛИ 13, четвертый элемент ИЛИ I, пятый элемент ИЛИ 15, информационный вход 16, информационный выход 17 и синхронизирующий вход 18, причем первый вход первого элемента И 1, соединен с входом элемента НЕ k, с первым входом второго элемента И 2 и с входной шиной устройства 16, второй вход первого элемента И 1, соединен со вторым входом третьего элемента И 3 и с информационным выходом первого триггера 10 памяти, а выход - с первым входом первого элемента ИЛИ 5, второй вход которого соединен с информационным выходом второго триггера 11 памяти, а выход - с информационным входом второго триггера 11 памяти, выход элемента НЕ 4 соединен с первым входом третьего элемента И 3, выход которого соединен с первым входом второго элемента ИЛИ 6, второй вход которого соединен со вторым входом второго элемента И 2 и с информационным выходом третьего триггера 12 памяти, а выход RTOporo элемента ИЛИ 6 соединен с информационным входом третьего триггера 12 памяти, выход второго элемента И 2 соединен с выходной шиной устройства 11, информационный вход первого триггера 10 памяти соединен с шиной нулевого потенциала, первый вход первого элемента И 7 дешифратора состояний соединен с входом элемента НЕ 9 дешифратора состояний и с входной шиной устройства 16, второй вход - с первым входом второго элемента И 8 дешифратора состояний и с информационным выходом первого триггера 10 памяти, а выходс первым входом третьего элемента ИЛИ 13, второй вход которого соединен с первым входом пятого элемента ИЛИ 15, с входом установки в 1 и с информационным выходом второго триггера 11 памяти, а выход - с входом установки в О третьего триггера 12 памяти, выход элемента НЕ 9 дешифратора состояний соединен со вт рым входом второго элемента И 8 де шифратора состояний, выход которого соединен с первым входом четвертого элемента ИЛИ h, второй вход которо го соединен со вторым входом пятого элемента ИЛИ 5. с. входом установки в 1 и с информационным выходом третьего триггера 12 памяти, а выхо с входом установки в О второго триггера 11 памяти, выход пятого элемента ИЛИ 15 соединен с входом установки в О первого триггера 10 памяти. Работа устройства происходит в соответствии с графом переходов. Состояние информационных выходов А,Ви С триггеров памяти записаны в вершины графа, ребра помечены значениями входного сигнала D . При поступлении синхронизирующих сигналов на вход 18, устройство из начального состояния 100 в зависи мости от сигнала на входе 16 перехо дит в состояния 010 или 001 и сохраняет его до конца работы. Си1- нал на выходе 17 повторяет сигнал на входе 16, если устройство переходит в состояние 001. В противном случае сигнал на выходе 17 не и меняется и равен О. Используя таблицу истинности, за шем уравнения установочных входов RS-триггеров 10-12 памяти Я.„ BD+BD D+CO В+С; рпО „ 0 °1 - R ADtC; S В; R;J AD4-BD4-B6 АСИ-В; S C. Полученные выражения определяют построение дешифратора состояний и подключение входов элементов ИЛИ 13 - ИЛИ 15. Каждый выход дешифратора состояний, соответствующий дан ному набору сигналов на информацион ных выходах триггеров 10-12 памяти и информационном входе устройства н i-TOM такте работы, через соответствующие элементы ИЛИ 13 - ИЛИ 15 с зан с входами установки в нулевое или единичное состояние тех триггер памяти, состояние которых на (+1)такте работы не изменяется и остает соответственно нулевым или единичны Ср-1внивая предлагаемое устройство с известным можно отметить, что надежность предлагаемого.устройства существенно выше, так как на каждом такте работы по установочным входам принудительно фиксируется значительная часть выходных сигналов с информационных выходов триггеров памяти, что отсутствует в известном устройстве. Поэтому вероятность сбоя триггеров памяти в предлагаемом устройстве существенно меньше и определяется вероятностью сбоя только тех триггеров, которые на данном такте работы принудительно не фиксируются. Формула изобретения Синхронное устройство управления, содержащее первый, второй и третий триггеры памяти и блок формирования состояний и выходных сигналов, состоящий из первого элемента И, первый вход которого соединен с входом элемента НЕ, с первым входом второго элемента И и с входной шиной состояний устройства, второй вход первого элемента И соединен со вторым входом третьего элемента И и с информационным выходом первого триггера памяти, а выход - с первым входом первого элемента ИЛИ, второй вход которого соединен с информационным выходом второго триггера памяти, а выход - с информационным входом второго триггера памяти, выход элемента НЕ соединен с первым входом тре1тьего элемента И, выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен со вторым входом второго эле- мента И и с информационным выходом третьего триггера памяти, а выход второго элемента ИЛИ соединен с информационным входом третьего триггера памяти, выход второго элемента И соединен с выходной шиной устройства, информационный вход первого триггера памяти соединен с шиной нулевого потенциала, а входы установки в единицу первого, второго и третьего триггеров памяти соединены с синхронизирующим входом устройства, отличающеесятем, что, с целью повышения надежности устройства, в него введены третий, четвертый и пятый элементы ИЛИ и де/шифратор.состояний, содержащий элемент НЕ и первый и второй элементы И, причем первый вход первого элемен тй И дешифратора состояний соединен с входом элемента НЕ дешифратора сое тояний и с входной шиной состояний устройства, второй вход первого элемента И дешифратора состояний соединен с первым входом второго элемента И дешифратора состояний и с информационным выходом первого триггера памяти, а выход - с первым входом третьего элемента ИЛИ, второй вход которого соединен с первым входом пятого элемента ИЛИ, с входом установ в единицу и с информационным выходом второго-триггера памяти, а выход - с входом установки в ноль третьего триггера пiaмяти, выход элемента НЕ дешифратора состояний соединен со вторым входом второго элемента И

х«а

i 7 дешифратора, состояний, выход которого соединен с первым входом четвертого элемента ИЛИ, второй вход которого соединен со вторым входом пятого элемента ИЛИ, с входом установки в единицу и с информационным выходом третьего триггера памяти, а выход - с входом установки в ноль второго триггера памяти, выход пятого элемента ИЛИ соединен с входом установки в ноль первого триггера памяти. Источники информации, принятые во внимание при экспертизе 1.Будинский Я.И. Логические цепи в цифровой технике. Связь, М., 1977, с. 298, рис. 6.U8. 2,Пухальский Г.И. Логическое проектирование цифровых устройств радиотехнических систем. Л., ЛГУ, 1976, с. 1if8, рис. it.2.1 (прототип).

Фиг.2

А& С Л-/ Cfff ff)

.Ъ

Авторы

Даты

1982-06-15—Публикация

1980-03-28—Подача