I

Изобретение относится к автоматике и вычислительной технике и может быть использовано при реализации технических средств цифровых систем контроля, систем обработки данных и автоматизированных систем управления.

Известно устройство для определения наибольшего и наименьшего из л чисел и их максимальной разности, содержащее п входных регистров, элементы ИЛИ р.

Основным недостатком этого устройства является низкое быстродействие, так как определение экстремального числа производится за К тактов работы генератора импульсов, где К - разрядность чисел.

Наиболее близким по технической сущности к изобретению является устройство для сравнения М двоичных чисел, содержащее h регистров, группу элементов И, элементы ИЛИ, регистр результата. В этом устройстве шина тактовых сигналов соединена с первыми

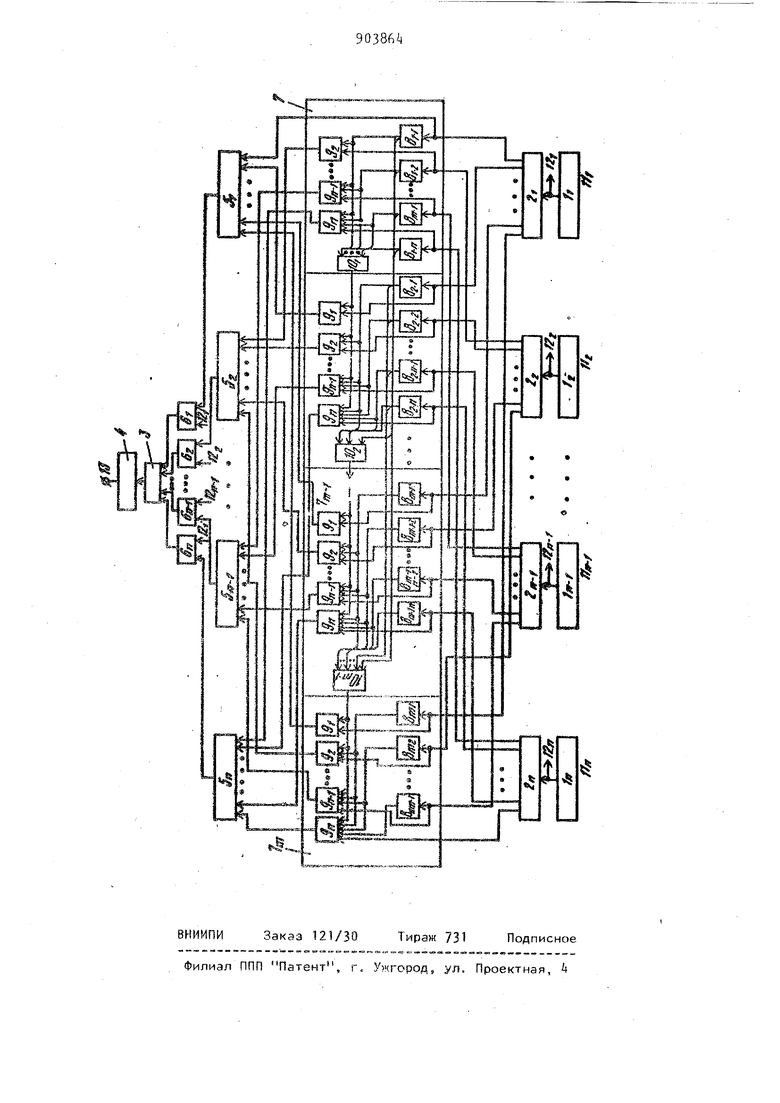

входами элементов И третьей группы, выходы которых подключены ко вторым входам элементов И первой группы. Вторые входы элементов И третьей группы соединены с выходами соответствующих разрядов регистра результата, вхбды установки в единичное состояние всех разрядов которого, кроме первого, подключены к выходам элементов И четвертой группы, первые входы каждого из которых соединены с выходами соответствующих разрядов сдвигающего регистра, а вторые входы - с выходами первого элемента ИЛИ. Входы этого элемента подключены к выходам первого и второго элементов И, первые входы которых соединены с инверсным и прямым выходами триггера знака соответственно, а вторые входы - с выходами третьего и четвертого элементов И, первые входы которых подключены к вы|ходу первого элемента задержки, KOTof рый через второй элемент задержки cof, единен со входами сдвигающего регист - . 390 pa и счетчика. Выход счетчика подключан ко входу установки в нулевое состояние сдвигающего регистра, к hepвым входам элементов И пятой Труппы, ко входу установки в нулевое состояние первого разряда регистра результа та и к первым входам группы элементов ИЛИ, выходы которых соединены со входами установки в единичное состояние соответствущих разрядов регистра результата, выходы которого подключены ко вторым входам элементов И третьей и пятой групп. Выходы элементов И пятой группы соединены с пе выми входами элементов И шестой групг ). Вторые входы элементов И шестой группы подключены к выходам регистрой. Вход третьего элемента аадержки соединен с шиной тактовых сигналов, а его выход - со входом первого элемента задержки и с первыми входами элементов И седьмой группы, второе входы которых подключены к выходам соответствующих разрядов сдвигающего регистра. Выходы элементов И седьмой группы соединены со вторыми входами элементов И второй группы 2 . Недостатком известного устркэйства является низкое быстродействие, так как сравнение п чисел производится последовательно за k тактовых импульсов, и, кроме того, от разряднос ти чисел, так как величина такта определяется временем сложения чисел в накапливающем сумматоре. Цель изобретения - повышение быст родействия. fTocTзеленная цель достигается тем, что в устройстве для определения наименьшего из г чисел, содержащем регистры, дешифраторы, регистр результата, многовходовой элемент И, поразрядные узлы анализа, элементы ИШ, группы элементов И, ИЛИ, при чем выходы каждого -го регистра, где i 1,2,...,п соединены со входами i-ro дешифратора и с информационными входами элементов И i-ой груп пы, а выходы i-ro элемента ИЛИ подключены ко входам управления элементов И 1-ой группы, выходы элементов И каждой 1-ой группы соединены с входами элементов ИШ группы, выходы которых подключены ко входам регистЬа результата, каждый j-ый выход каж дого i-ro дешифратора соединен с i-ы входом j-ro поразрядного узла анали;за, где j 1,2,...,m,m - число раз4рядов операндов, каждый i-ый выход j-ro поразрядного узла анализа подкгЛочен к j-ому выходу i-ro элемента ИЛИ, а выход переносов каждого К-го поразрядного узла анализа, где К 1,2,...,(т-1), соединен со входом управления (К+1)- го поразрядного узла анализа. Кроме того, каждый поразрядный узел анализа состоит из п элементов И, п элементов НЕ и многовходового элемента И, причем каждый i-ый вход узла подключен к первому входу l-po элемента И, вход управления узяа соединен со вторыми входами элементов И, каждый i-ый вход узла подкт)цен через 1-ый элемент НЕ к (+2)-ому входу (i-H), (+2),..° п-го элементо.в И и к 1-ому входу многовходового ;элемента И, выход которого подключен .к выходу переносов узла, выход каждого- -го элемента соединен с I-HM выходом узла. При этой лт-ый поразрядный узел анализа состоит из И элементов И и {и-1)го элемента НЕ, причем каждый р-ыйвход узла, где Р- 1,2,. ,. ,(и-1) соединен с первым входом элемента И, вход переносов зла подключен ко вторым входам элементов И, каждый Р-ый вход узла через р-ый элемент НЕ соединен с (р +2)-ым входом (f -U, (р4-2),.., ,Ц-го элементов И, ni-мй вход узла подключен к (и+2 )-ому входу Wro элемента И, выход каждого I-ro элемента И соединён с -l -ым выходом узла. На чертех{е представлена блок-схема устройства. Устройство содержит регистры 1 , 1д,,...,1у,, дешифраторы 2,22,...,., группу элементов ИЛИ 3f регистр k результата, элементы ИЛИ 5/, 2. группы элементов И 6 , 6 , ..,,6, поразрядные узлы , 7,-.. ,7 ана-лиза, каждый К-ый из которых, где К 1,2 ,.., , ), состоит из элементов НЕ 8 8/JI, ..., 8и, элементов И 9, 9г, ..,9и многовходового элемента И 10,т-ый поразрядный узел анализа состоит из элементов НЕ 8, Sj., ..., элементов И 3 , 9 9,, входы регистров 11, ll, ходы регистров 12xf, 12,2,..., 1 выходные шины 13 устройства, Устройство работает следующим образом. 590 Пусть наименьшее число находится во втором регистре 2 и равно 1, т.е на втором выходе дешифратора 2 будет единичный сигнал. При этих условиях все первые выходы всех дешифраторов, а также вторые выходы, кроме 2-го дешифратора, будут нулевые. Тогда выходы элементов НЕ первого поразрядно го узла анализа будут единичными, многовходовой элемент И 10 первого поразрядного узла анализа разрешает .анализ во второй группе, открывая по первым входам все элементы И этой группы. Второй выход первого дешифратора - нулевой, поэтому единичный сигнал с выхода первого элемента НЕ во втором поразрядном узле анализа L открывает по вторым входам все элементы И, начиная со второго. На входе второго элемента Н Зда и на третьем входе второго элемента И 92. действует единичный сигнал. Нулевой сигнал с выхода элемента Sgj закрывает все элементы И во втором поразрядном узле анализа, начиная с третьего, по третьему входу. С выхода элемента И 92. единичный сигнал через элемент ИШ 5/1 поступает на второй вход элемента И первого поразрядного узла анал«1за 7. Число, хранимое в регистре Ij, по шинам 12 передается через группу элементов ИЛИ 3 в регистр Ц результата. Очередной цикл работы устройства начинается после приема следующей в группы И чисел во входные регистры. В предлагаемом устройстве время сравнения не зависит ни от количества сравниваемб1х чисел и ни от их разрядности и определяется суммарным временем анализа в одной группе, так ка он выполняется во всех группах одновременно, что позволяет повысить быстродействие. Формула изобретения 1. Устройство для определения наи меньшего из VI чисел, содержащее регистры, дешифраторы, регистр результата, многовходовой элемент И, поразрядные узлы анализа, элементы ИЛИ группы элементов И, ИЛИ, причем ёыхо ды каждого из i-ro регистра, где 1 1,2,...,и соединены со входакм i-ro дешифратора и с информационными входами элементов И fl-ой группы, а выходы 4-го элемента ИЛИ подключены 46 ко входам управления элементов И -с(й группы, выходы элементов И каждой -ой группы соединены со входами элементов ИШ группы, выходы который подключены ко входам регистра резулцтата, отличающееся тем, что, с целью повышения быстродействия, в нем каждый выход каждо-. го -f-ro дешифратора соединен с входом -го поразрядного узла анали-j за, где j 1,2,... ,УИ, ш- число раз ядов операндов, каждый t-ый выход -j-po поразрядного узла анализа подключен к 4-ому входу ч-го элемента ИЛИ, а выход переносов каждого К-го поразрядного узла анализа, где К 1 ,2,.. . ,() , соединен со входом управления ( К+1)-го поразрядного узла анализа. 2, Устройство по п. 1, отличающееся тем, что в нем каждый К-ый поразрядный узел анализа состоит из элементов И, И элементов НЕ и МНОГОВХОДОВ.ОГО элемента И, nf iчем каждый 1 -ый вход узла подключен к первому входу -1-го элемента И, вход управления узла соединен со BTd рыми входами элементов И, каждый -t-ый вход узла подключен через -ый элемент НЕ к{1+2)-ому входу (V+ll , (1+2)%... ,У1-го элементов И и к -i-OMy входу многоэходового элемента И, выход которого подключен к выходу переносов узла, выход каждого -го элемента соеданен с 4-ым выходом узла. 3. Устройство по п. t, отличающееся тем, что в нем ftrwH поразрядный узел анализа состоит из И элементов И и (и-1)-го элемента Нц, каждый р-ый вход.узла, где р 1,2,...|1И-|) соединен с первым входом р-го И, вход переносов узла подключен ко вторым входам элементов И, каждый р-ый вход узла через р-ый элемент. Н€ соединен с ;(р+2)-ым входом (р-0 ,(р+2 ),..., И-ifo элементов И, т-ый вход узла подключен к {||Н-2)-ому входу п-го элемен-та И, выход каждого i-ro элемента И соединен с i-ым выходом узла Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР tf 23«003, кл. G Об Г 7/0. 1968. 2.Авторское свидетельство СССР № , кл. G 06 F 7/02, 1979 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения экстремального из @ чисел | 1984 |

|

SU1171779A1 |

| Устройство для выбора упорядоченной последовательности данных | 1982 |

|

SU1059565A1 |

| Устройство для выбора упорядоченной последовательности данных | 1983 |

|

SU1109738A1 |

| Устройство для упорядочивания @ чисел | 1982 |

|

SU1062687A1 |

| Устройство для сравнения чисел | 1980 |

|

SU903862A1 |

| Устройство для сравнения чисел | 1981 |

|

SU960799A1 |

| Устройство для определения экстремального числа | 1981 |

|

SU981987A1 |

| Устройство для определения максимального из @ чисел | 1981 |

|

SU999041A1 |

| Устройство для сравнения п двоичных чисел | 1979 |

|

SU840888A1 |

| Устройство для сравнения чисел | 1979 |

|

SU798813A1 |

Авторы

Даты

1982-02-07—Публикация

1980-01-17—Подача