носов узла преобразования кодов, а ( р л- 1) -и вход узла преобразования кодов соединен дополни ельно с (г + 4 l)-ым входом р -го элемента И.

3. Устройство по п. 1, о т л и -ч а io д а е с я тем, что в нем (6+ 1) й узел преобразования кодов содержит 8 - 1 элементов EiE, ( П1 - 6 элементов И и ( Ш - 2 - 1 элементов ИЛИ, причем 6 -и вход

6 + 1) -го узла преобразования кодов, где 6 1, 2, . . ., (т -Е,), подключен к (5+ 1). -му входу. S -го элемента И, первый -вход управления узла преобразования.кодов соединен с первыми входами первого элемента И и всех элементов ИЛИ,t -и управляющий вход узда, где t 2, 3,.,,

... (i -1)11 f подключен к i -ьш входам S , S + 1, . . ., (т - Е - 1) -гсэ элементов ИЛИ, выход 5-го элемента ИЛИ соединен с (5+ 1)-ым входом

(5+ 1)-го элемента И, выход первого элемента И соединен с выходом переносов узла преобразования кодов

и через первый элемент НЕ - с первыми входами остальных элементов И, выход (6+ элемента И. соединен через (S + 1) -и элемент НЕ с (5 + 2)-ми входами (5+2 ,5+3 /.. .. . , (vn-)-го элементов И.

4, Устройство по п. 1, отличающееся тем, что, в нем каждый ( -и ком{лутатор содержит группу элементов ИЛИ и ц блоков из (т + 1 -i) групп элементов И, причем информационные входы элементов И -го блока подключены к информационным входам « -ой группы коммутатора, первые управляющие входы элементов И t--ro блока подключены к i -ым входам управления передачей, вторые управляющие входы элементов И р-и группы каждого i-го блока, Р 1, 2, ..., .../ т+-1--|)},соединены с р-ым управпяющим входом коммутатора, выходы элементов И всех групп подключены к соответствующим входам элементов ИЛИ группы, выходы которых соедине- ны с выходами -го коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выбора упорядоченной последовательности данных | 1983 |

|

SU1109738A1 |

| Устройство для выбора упорядоченной последовательности данных | 1982 |

|

SU1059565A1 |

| Устройство для группового обслуживания запросов | 1984 |

|

SU1196868A1 |

| Устройство для определения экстремального из @ чисел | 1984 |

|

SU1171779A1 |

| Устройство для определения наименьшего из @ чисел | 1980 |

|

SU903864A1 |

| Устройство для выбора упорядоченной последовательности данных | 1984 |

|

SU1218381A1 |

| Устройство для сортировки двоичных чисел | 1982 |

|

SU1049900A1 |

| Устройство для сравнения чисел | 1981 |

|

SU964631A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1986 |

|

SU1425698A2 |

| Устройство для сравнения п двоичных чисел | 1979 |

|

SU840888A1 |

1

Изобретение относится к вычислительной технике и может быть использовано при реализации систем обра60Т5СИ данных и автоматизированных систем управления.

Известно устройство для упорядочения чисел, содержащее входных регистров, где и -. количество чисел,

элементы ИЛИ, группы элементов. И, блок памяти из п выходных регистров 1 ,

Нгшболее близким по технической сущности к изобретению является устройство для определения наименьшего из п чисел, содержащее регистры, дешифраторы, регистр результата, поразрядные узла анализа, группы элементов и, ИЛИ,причем каждый j-и выход каждого -го дешифратора соединен с i -ым входом -го поразрядного узла анализа, где j 1, 2,,.. „, ,-рГ1| J 1, 2, . , ., ЦП , m - число разрядов операндов, каждый i -ый выход поразрядного узла анализа подключен к j-му входу I -го элемента ИЛИ, а выход переносов каждогоk -го поразрядного узла анализа, где К 1, 2, ..,,(m-l), соединен с входом управлений (k+ 1)-го поразрядного узла анализа, канодый k-и поразрядный узел .анализа состоит из ti элементов И, и элементов НЕ и многовходового элемента И, причем казкдый «-и вход узла подключен к первому

входу 4 -го элемента И, вход управлени узла соединен с вторыми входами элементов И, каждый -и вход узла .подключен через -и элемент НЕ к (i +2)-му входу (i +1) ,(л +2) , . . , , h -го элементов И и к i-му входу многЪвходового элемента И, выход которого подключен к выходу переносов узла, выход каждого i -го элемента

0 И соединен с t -ым выходом узла, тп -и поразрядный узел анализа состоит из П элементов И и ( п - 1) -го элементов НЕ, причем каждыйр -и вход узла , где , 2, ..., (п-1),

5 соединен с первым входом р-го элемента И, вход переносов узла подклю-. чен к вторым входам элементов И, каждый р-и вход узла через р-и элемент НЕ соединен с р + 2)-м входом

- ( р + 1) , ( р + 2) , . . ., tt -го элементов И, ill -и вход узла подключен к (т+ 2)-му входу л-го элемента И, выход каждого .; -го элемента И соединен с -ым выходом узла 2 .

Однако определение наименьшего числа производится за один цикл работы устройства. Поэтому для yrio- , рядочивания массива из И чисел пот- ребуется п раз выполнить йбраадение к устройству, причем каждый раз

0 необходимо исключать из анализа выбранное число в предыдущем цикле. Таким образом, известное устройство требует организации п циклов обращения и, следовательно, его неостатком является низкое быстроействие.

Цель изобретения - пойышение быстродействия устройства для упорядочивания h -чисел за счет одновременного сравнения исходных чисел.

Поставленная цель достигается ем, что, в устройство для упорядоивания п чисел, содержащее входные егистры, дешифраторы, поразрядные злы анализа, элементы ИЛИ, выходной регистр, причем выходы каждого -го входного регистра, входы которого являются информационными входами устройства, соединены с входами .i-ro дешифратора, где i 1, 2, .... ..,,П,каждый j -и выход -го дешифратора, где , 2, ...,m,vn- чисо разрядов операндов, соединен с -ым входом j--ro поразрядного узла анализа, каждый -и выход j-го поразрядного узла анализа подключен к j-му входу -го элемента ИЛИ, каждый -и поразрядный узел анализа содержит элементы НЕ .и И, выходы которых соединены с выходами поразрядного узла анализа, а один из входов через элемент НЕ - с входами поразрядного -узла анализа, введены злы преобразования кодов, коммутаторы и (п- 1) выходных регистров, причем выход логической суммы -го поразрядного узла анализа подключен к k. входу -го узла преобразования кодов, где k i - (i- 1) , выход переносов каждого -го узла преобразования кодов соединен с первым управляющим входом (-t + 1) -го узла преобразования кодов, каждый р-й выход -го узла преобразования кодов соединен с р -ым управляющим входом 1-го коммутатора, где р 1,2, . .. , гп - I i - 1 , а С -и выход узла преобразования кодов - с cj-ым управляющим входом + 1)-го узла преобразования кодов, где ( 2, 3, ...,|т-) выходы i-го входного регистра подключены к информационным входам i -ых групп коммутаторов, выходы каждого i-го элемента ИЛИ соединены с -ми входами управления передачей коммутаторов, выходы i-го коммутатора подключены к входам i-ro выходного регистра, вкходы которого являются информационньоми выходсхми устройства, в каждый -и поразрядный узел анализа введен элемент ИЛИ, причем каждый С-и вход поразрядного узла анализа, где t 1., 2, ..., (tt- 1) , через 6-й элемент НЕ соединен с Е-ми зходами В, +1, ..,, ( 1)-го элементов И и Р-ым входом элемента ИЛИ, выход которого является выходом ло- : гической суммы поразрядного узла анализа, «-и вход узла подключен к п-му входу (Ч- 1)-го элемента И, .

Первый вхея поразрядного узла анализа соединен с его первым выходом, выход каждого 2 -го элемента И является (6 + 1) -ым выходом поразрядного узла ансшиза,

5 Первый узел преобразования кодов содержит (и- 1 элементов НЕ и (км - I) элементов И, причем каждый г-и вход узла преобразования кодов, где 1 1, 2, ...,(т- 1), через

0 Р-й элемент НЕ соединен сг -ми входами f,, ...,(vYi- 1) -го элементов И, выходы которых соединены с (t + 1) -ми выходами узла преобразования кодов, причем первый вход

5 подключен к первому выходу и выходу переносов узла преобразования кодов, а(п+ l)-и вход узла преобразования кодов соединен дополнительно 0(1 + + 1)-м входом г-го элемента И.

Q Каждый (е + 1) -и узел преобразо- , вания кодов содержит (т-2 - 1) элементов HE,(im-e) элементов И и (гп - 1) элементов ИЛИ, причем S-и вход (Р + 11 -го узла преобразования

5 кодов, где S 1, 2, ...,(т-В)., подключен к (S + 1)-му входу 5-го элемента И, первый вход управления узла преобразования кодов соединен с первыми входами первого элемента

И и всех элементов ИЛИ, -и управляЮ1ДИЙ вход узла, где t 2, 3, .... „,)11- (i - 1) , подключен к t-ым входам 5,5 + 1, . .., (т - - 1) -го элементов ИЛИ, выход 5-го элемента ИЛИ соединен с (5+ И -ым входом

5 2 + 1) -го элемента И, выход первого элемента И соединен с выходом переносов узла преобразования кодов и через первый элемент НЕ - с первыми входами остальных элементов И,

0 выход (б + 1) -го элемента И соединен через (S+ 1)-и элемент НЕ с (5+2)-ми входами is + 2) , (s + 3) , . .., ( ni -Е)-го элементов И.

Каждый i -и коммутатор содержит

5 группу элементов ИЛИ и YI блоков из (m + 1 -i) групп элементов И, причем информационные входы элементов И i-го блока подключены к информационным входам i-и группы коммутатоQ ра, первые управляющие входы элементов И { -го блока подключены к л-ым входам управления передачей, вторые управляющие входы элементов И р-и группы каждого i -го блока, | р 1,

5 2 f ( + 1 4 13 соединены с

р-ым управляющим входом коммутатора, выходы элементов И всех групп подключены к соответствующим входам элементов ИЛИ группы, выходы которых соединены с выходами -го коммутато0 ра.

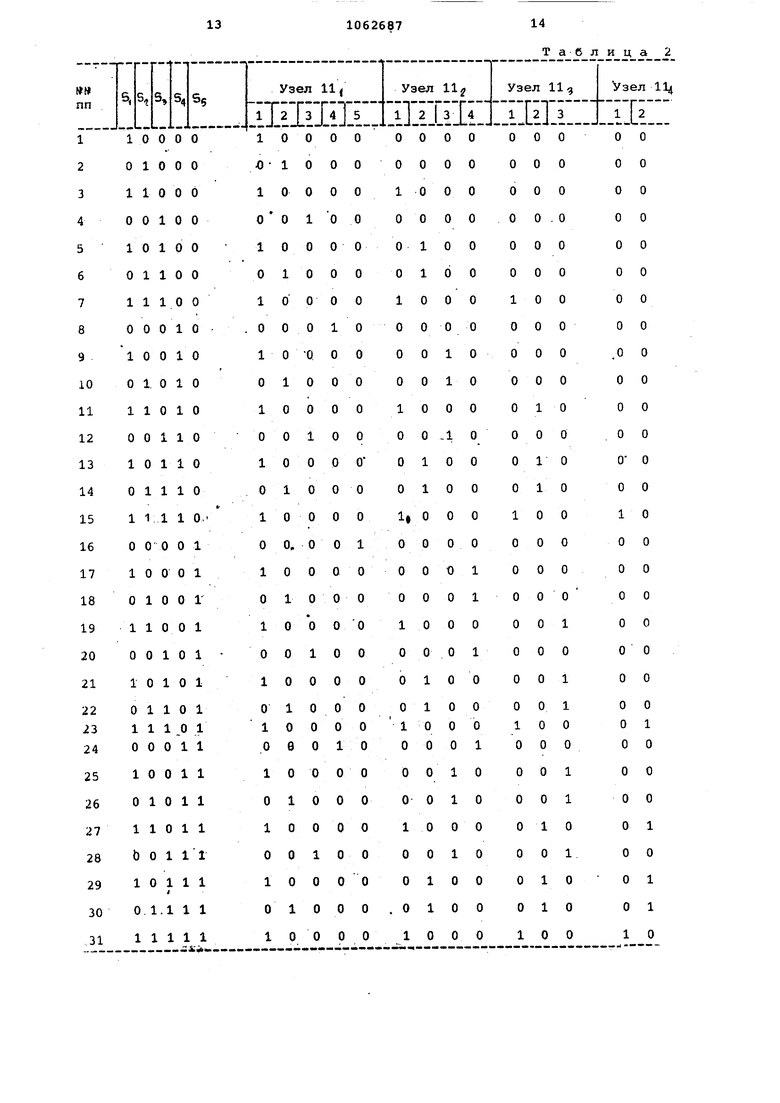

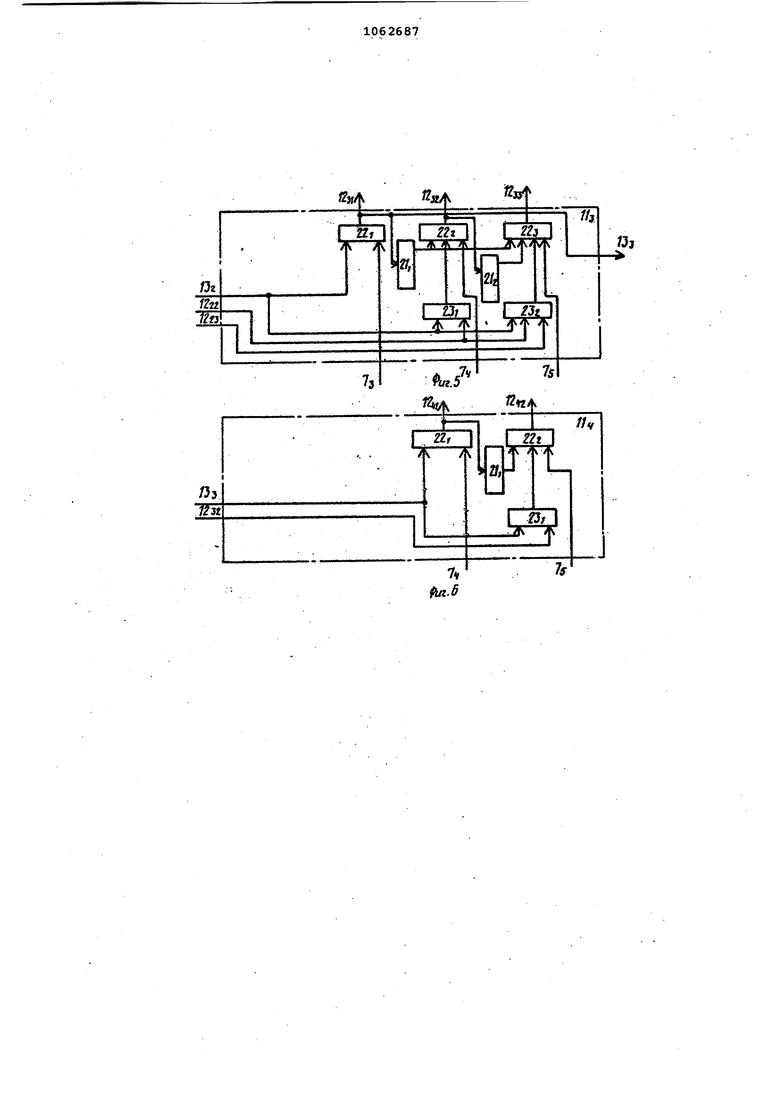

На фиг. 1 приведена функциональная схема устройства для четырех чисел, принимающих значения от 1 до5; 5 яа фиг. 2 - функциональная схема поразрядного узла анализа; на фиг.3-6 узлы преобразования кодов с первого по четвертый; на фиг. 7 - функциональная схема ког/шутатора. Устройство содержит инфор 5ационные входы 1 - ) / подключенные к входным регистрам 2 - 2 , выходные шины которых 3( - 34 подсоединены к дешифраторам 4 - 4, выходы дешифраторов 5 - 2 - , 5, -5з5 5 - , соединенные с поразрядными узлами анализа б - 6 , имеющие выходы 7jf - 7 логической суммы и выходные шины 8 - 8 , 8 - 8,24 - f 841 В4(), 85- - 854/ подключенные к элементам ИЛИ 9 -- 9 имеющие выходные шины 10 - Юл , узлы преобразования кодов 11- 11д , имеющие выходные шины 12 ( - i2 , 12/3, 12 12, выходы переносов 13 - 13-j, комму таторы 14 ,j - 14 , выходные шины ко торых 15 - 154 подсоединены к выходным регисарам 16 - 164 , выходы которых соединены с выходными шинам устройства 17 - 174. Поразрядные узлы анализа имеют одинаковую структуру, каждый узел содержит элементы НЕ 18 - 18, эле мент ИЛИ 13 и элементы И 20 - 20. Узлы преобразования кодов имеют одинаковую структуру по своему функ цио.пальному назначению. Отличие сос тоит лишь в количестве входов и выходов и определяется их местом в схег-.;е устройства. Первый узел содержит группу эле. .в НЕ 21 и группу элементов И 22„ Последующие узлы преобразования кодов дополнительно содержат группу элементов ИЛИ 23. Коммутаторы имеют одинаковую структуру, отличающуюся лишь Их местом в устройстве „ Коммутатор содержит четыре блока количеству входных регистров. Каждый блок состоит из группы элементов И 24 f число которык определяется местом коммутатора в устрой/стве, и группы элементов ИЛИ 25. Тггк. KOMi.iyTaTop 14 ( содержит в каждок блоке по пять групп элементов И 24J коммутатор 142 - по четыре группы, коммутатор 14-j -по три гру пы, комглутатор 14 - по две группы элементов И 24. Устройство работает следующим об разом, Упорядочивание .массива из ft чисе ,в предлагаемом устройстве производи ся в порядке возврастания значений чисел таким образом, что в первом выходном регистре 16 размещается наименьшее число из И чисел, во вто ром регистре 162 - наименьшее из (.и-- 1) чисел и т,д., а в j -ом выход ном регистре наибольщее из п чи -сел. Такая последовательность образуется при упорядочивании массива чисел, представленных в прямом коде При необходимости упорядочивания массива из Ц чисел в порядке убыва-ния значений все числа принимаются t.Bo входные регистры 2 - 2 в обратном коде. Выбор экстремального числа выполняется путем сравнения сигналов одноименных выходов дешифраторов, преобразующих двоичные коды чисел в распределительные. Пусть имеется массив из четырех чисел: а 5, а, 1, а 4, а 2. Для этих значений чисел в табл. 1 приведены распределительные коды. Из анализа табл. 1 видно, что в первый выходной регистр 16/) необходимо передать число из второго входного регистра 2- по управляющему сигналу, сформированному на основе сигналов с первых выходов дешифраторов 4 - 4, во второй выходной регистр 16/2 аналогично рассмотренному выше - из четвертого входного регистра 2 , в третий выходной регистр 16 - из третьего входного регистра 2,, в четвертый выходной регистр 1б4 - из первого входного регистра 2 , Формирование обобщенных сигналов 5;( - 5 , являющихся логической суммой сигналов с одноименных выходов дешифраторов 4 /( - 4 , производится в поразрядных узлах 6 - 6 анализа. Эти сигналы поступают на выходы 74 - 7 логических сумм 6 j - 65 узлов анализа и используются в узлах 11 - 114 преобразования кодов для формирования управляющих сигналов, подаваемых в коммутаторы 14/i - . Обобщенные сигналы i - i4 формируются элементами ИЛИ 9 - 94 и поступают на шины 10,, - 104. Эти сигналы используются в коммутаторах 14j управления передачей содержимого входных регистров 2 - 24 в соответствующие выходные регистры 16 164 в определенном для них порядке. Поразрядные узлы 6 - 6 ангшиза имеют одинаковую структуру и для чисел. При наличии хотя бы одного единичного сигнала на входах м (фиг. 2) на одном из выходов появляется единичный сигнал. Кроме того, единичный сигнал возникает и на выходе 7 логической суммы, так как все входные сигналы поступают на элемент ИЛИ 19. Элемен-ты НЕ 18;,IB-j необходимы для получения одного лишь сигнала на выходах В/ - 8 ц при равных кодах исходных чисел. Так, для указанного выше примера единичный сигнал возникает йа вхо;Де Sj, поэтому элемент И 20|. открыт, 1Так как на его входах присутствуют , единичные сигналы с выхода элемента НЕ 18,{И.с входа 52 , Нулевой сигнал с выхода элемента НЕ 18, запирает элементы И 20 и 20-j. Таким образом, сигн-ал с..выхода . , T.e.i f указывает ка то, что наименьшее число находится в регист ре 2 , а сигнал 7 , т.е. S , определяет необходимость передачи это го числа в первый выходной регистр Так как сигнал 3 равен единице, то второе число из четвертого входного регистра 2 1 Должно быть передано во второй выходной регистр 16. Очередной сигнал 5 О, а 54 1 Это означает, что очередное наименьшее число необходимо передать в третий выходной регистр 16 по сигналу 64 из третьего входного регистра 2ч (3 1) . Сигнал 55 1/ что означает необходимость передачи числа в выходной регистр 16ii. из первого входного регистра 2, (f 1) . Таким образом, двоичный код сигналов в -55 г равный 11011, должен быть преобразован в код 1111. Эти функции выполняются узлами преобразования кодов 11 - 11(} , каждый из которых формирует управляющие сигна лы для соответствующего выходного регистра. Таким образом, каждый узел 11/1 - 114 преобразования кодов (фиг. 3-6) имеет одинаковую структуру. Однако функциональная схема каждого из них определяется местом узла в устройстве. Так, узел формирует управляющие сигналы для передачи числа из одного из четырех входных регистров в первый выходной Поэтому он имеет пять входов по числу сигналов 5 -3g и пять выходов Если значение числа равно единице, то сигнал Si 1, и он присутствует на входе 7, коммутатора 14( (фиг. 3). Этот сигнал через элементы НЕ 21 закрывает элементы И 225И 22, и поэтому единичный сигнал б дет лишь на выходе 12 . Если значение .наименьшего числа равно 2, то сигнал Sj О, а сигнал S2 1. В этом случае сигнал на выходе узла 11 равен единице. Если же значение наименьшего чис ;ла равно 5, то сигнал S 1 г а остальные сигналы S -5 равны нулю В этом.случае единичный сигнал буде только на выходе 12 ,§ Узла 11 . Узлы-И - 11. L4 преобразрвания кодов (фиг, 4-6) отличаются от узла 11 тем, что в них учитывается .передача числа в предыдущие выходные регистры. В этих узлах дополнительно имеются элементы ИЛИ 23, пос редством которых учитываются преобразованные коды в предыдущих узлах преобразования. С помощью элементов НЕ 21 блокируется/ формирование ложных единичных сигналов, чем исключается наличие на выходах узла преобразования двух и более-сигналов. Посредством элемента 22, формируется сигнал переноса при кодах в, 1111 : в. узле llg - 11...; в узле Из - 111. . . Преобразование кодов в каждом узле 11 - 114 производится в соответствии с табл. 2 состояния узлов. В крайней левой части табл. 2 указаг ны возможные комбинации сигналов j (J - If5), в остальныхчастях таблицы - кодовые комбинации выходных сигналов узлов 11 - 11 преобразования. Рассмотрим работу узлов 11 - 11. преобразования, когда кодовая ком- . бйнация сигналов 5j (j 1,5) равна 11111. При этих условиях сигналы на шинах 7, - 7j равны единице. По сигналу шины 7 в узле . 3) блокируется через элемент НЕ 21 формирование сигналов на выходных шинах 12 Таким образом. единичный сигнал будет на выходе 12 и кодовая комбинация выходных сигналов составит 10000 (табл. 2). Сигнал переноса с выхода 13 узла 11 и нулевые сигналы на выходах 12 12,(4 поступают на второй узел 11 преобразования кодов (фиг. 4) . Так как на шинах 13, и 7 имеются единичные сигналы, то элемент И 22.J узла 112 открыт, и еди- ничный сигнал с выхода этого элемента поступает на выходную шину 122 и шину переноса и через элемент НЕ 21( закрываются элементы И 22 - 22. На выходе узла 11/ образуется кодовая комбинация 1000 ( табл.2) . Выходные сигналы с узла 11 поступают на третий узел 11 преобразования кодов. Так как единичные сигналы имеются на шинах 13-2 и 7 з (.фиг. 5), то элемент И 22 открыт. Единичный сигнал с его выхода поступает на выходную шину 122j и шину 13- переноса и через элемент НЕ 21 закрываются элементы И 22 и 22. Таким образом, выходная комбинация сигналов составит 100 (табл. 2). Сигналы с выходов узла 11- поступают на четвертый узел 11, преобразования кодов. Так как единичные сигналы имеются на входах 13 и 7 (фиг. 6), то элемент И 21 открыт. Единичный сигнал с его выхода поступает на шиНу 124« и через элемент , НЕ 21 -закрывает элемент И 22. Таким образом, на выходе узла 114 формируется кодовая комбинация сигналов 10, что также соответствует табл. 2.

При других кодовых комбинациях сигналов 5j Q 1,5 работа узлов 11 - 11;} производится аналогично рассмотренной выше с участием элементов ИЛИ 23.

Выходные сигналы узлов 11 - 11, по шинам 12 - , - , 12- - , 124,| .- ,е, преобразованные сигналы 5 РЧ элементов ИЛИ а ;( - 94 по шинам 10 д - 10, (сигналы i 4) входных регистров по шинам 3 ;( - З поступают на коммутаторы 14 - 144.

Коммутаторы 14 - 144 обеспечивают в соответствии с .преобразованными кодами сигналов 5;| -Sg в узлах 11 { - 11 передачу чисел из входных регистров 2ц - 24 в выходные регистры 16-( - 164. Коммутаторы одинаковую структуру, различие состоит в количестве оборудования, определяемое местом коммутатора в устройстве,

Рассмотрим работу устройства в целом при указанных выше знaчeнияx четырех исходны { чисел.

В соответствии с табл. 1 единичные сигналы появляются на выходе Ъ дешифратора 4, на выходе S1 дешиф-ратора 4,2/ выходе 5,4 дешифратора 4, на,выходе 5,, дешифратора 4 (фиг. 1) . Таким образом, единичные сигналы появляются на следующих входах поразрядных узлов анализа 6 1 - 65 : на входе узла 6 ,. на входе- узла 6, на входе 5-5-4 У ла 64 и на входе 5/( узла бд .. В узлах 6. - 6 .формируютсясигналы (фиг. 1 и фиг. 2), поступающие в узле 6,1 на шину 7 (5/, 1) и на шину 8,2 г в узле 6 - .на шину 7 (, 1) и на шину 824 г в узле 6ф - на шину 7 (4 1 и на шину 84-5 ; в узле 6 .на шину 7 (S - и шину 8 . В узле 65 сигналы равны нулю.

Сигналы S , 5 , 64 / Sj поступают на узлы 11/1 - 11 преобразования. Сигналы с выходов узлов 6, -6 на элементы ИЛИ 9;) -. Эд поступают .,, по следующим шинам: на элемент ИЛИ 9 по шине 8 5 , на элемент ИЛИ Sj по шине f на элемент ИЛИ 9, - по шине 8,, на элемент ИЛИ 9 - по шине 8 54

На выходах элементов ИЛИ 9 - 9 формируются сигналы соответственно f, -i(} , поступающие на коммутаторы 14 - 144.

По кодовой комбинации сигналов oj ( 1,5), равной 11011, формируются выходные сигналы в узлах 11

-11д преобразования кодов следующим образом.

г В узле .,3) по единичному сигналу на шине 7 кодовая комбинация 10000, и сигнал переноса на шине 13. В узле 11-г (фиг. 4) по единичным сигналам на шинах 13 и Iq кодовая комбинация 1000 и сигнал на шине переносов 13,2 узле 11 „(фиг.5) единичные сигналы присутствуют на шинах 13/j, 7 и 7 5-. Так как элемент 5 И 22,| закрыт нулевым сигналом Sна шине 7, то единичный сигнал с выхода элемента НЕ 21,) открывает элементы И 22 и 22, по их первым входам. Так как единичные сигналы

0 присутствуют- на втором входе элемента И 22 (сигнал на шине ) и на третьем (сигнал на шине 7), то элемент-И 22 открыт. На выходе 22, узла ll-j формируется единичный сиг5 нал, который через элемент НЕ 21 закрывает элемент И 22. Таким образом, на выходе узла 11 формируется кодовая комбинация 010. Эти сигн алы и сигнал переноса по шине 13-j,

Q равный нулю, поступают в четвертый . узел 11,:. Так как сигнал на шине 13з равен нулю (фиг. 6), то элемент И 22 J закрыт, нулевой выходной сигнал которого через элемент- НЕ 21(

5 открывает элемент И 22„.по первому входу. На шине 7 имеется единичный сигнал. Так как имеется единичный

сигнал на шине 12

то элемент

32

И 222 открывается, и на выходе 114 Q формируется кодовая, комбинация 01.

Кодовые комбинации выходных сиг.Нс-лов узлов 11 - 114 преобразова.ния соответствуют табл. 2 (строка В(}Табл. 2 помечена звездочкой).

Таким образом, единичные сигналы.

по которым производится передача чисел в выходные регистры, присутствуют на шине 12,ц коммутатора 14, на шине 12 KON-iMyTaTopa 14 , на шине коммутатора 1., на шине

1242 коммутатора 14, на шинах 10 - 10() элементов ИЛИ 9 - 94 .

По сигналу на шине 12 и сигналу на шине 10 (фиг. 7) число передается в регистр 16 по шине 15 из ре5 гистра 2i через группу элементов И 24 . . По сигналу на шине 122 :) сигналу на шине Юд число из регистра 24 передается в регистр 16 по шине через группу элементов

0 И 244,| . По сигналам на шинах 10, число из регистра 2 передается в регистр 16/j по шине IS-j через группу элементов И 24 о. По сигналам на шинах 12) { «исло из регист5 рз 2{ передается в регистр 16 по шине 154 через группу элементов И 24 , .

Таким образом, в регистрах 16 ( 16 сформирована упорядоченная пос0 ледовательность чисел: а 1, л 2, , а(5за один цикл работы устройства.

При необходимости получения убывающей упорядоченной последовательности во входные регистры следует принимать обратные коды исходник чи- сел. При этом в выходных регистрах фиксируется последовательность чисел в обратных кодах. Проведем сравнительный анализ предлагаеного устройства и базового объекта по быстродействию, полагая, что оба устройства выполнены на одной и той же элементной базе. В качестве базового объекта выберем устройство для упорядочивания чисел. Общим принципом работы обоих устройств является сравнение чисел от момента приема их во входные регистры и до момента их записи в блок памяти, содержащий П. выходных регистров. В базовом объекте время сравнения кодов чисел определяется задержкой между импульсами СИ/ и CHg : H«-2)tTp, где 2 иди время задержки в элементе ИЛИ; время срабатывания триггера в реверсивном счетчике В соответствии с (3 можно прип ,и НС ) - I-MAM Тогдаг,г„,.8(у,-2П,,„ ЛЛИ ИЛИ I-Выдача выбранного числа для запиего в блок памяти производится по импульсу СИл. Время выдачи опре|Деляется как А Л ЛвЪ1А И ИЛИ -«ли Таким образом, общее время, затрачиваемое на упорядочение чисел, составляет Т, 3. Подставляя выражения (1) и (2) в выражение (.3) , получим ,(n-2ro,.Q-tv,-A8nM3b c,, вре гд ны та В) ва ляе при при по обе ВИИ сел

Таблица 1 В предлагаемом устройстве общее мя цикла работы составляет ,+inp4tj, tg - время работы дешифратора; время работы поразрядного узла анализа; Пр время работы узлов преобра, зования -кодов; Ск - время работы коммутатора. Примем, что дешифраторы выполнена элементах И, тогда -V -ИЛИ Время tgn (фиг. 2) ДЛЯ чисел сосляетВремяijjp (фиг. 3-6), i (фиг. 7) л.г.ч-г ,,M ;M2n,,„4г,, Исходя из полученных соотношений, мя работы предлагаемого устройстсоставляет,2ni,,,.1;,,,4 Выигрыш в быстродействии опредется по соотношению Т, Лб -13Ь1„ли 8п-13 -или- -2 + В табл. 2 приведены значения ti различных величинах ц Из анализа таблицы видно, что менение предлагаемого устройства сравнению с базовым объектом спечивает выигрыш в быстродейст-при упорядочивании массива чи, когда П 2- 2.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для упорядочивания чисел | 1980 |

|

SU932487A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для определения наименьшего из @ чисел | 1980 |

|

SU903864A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-12-23—Публикация

1982-10-12—Подача