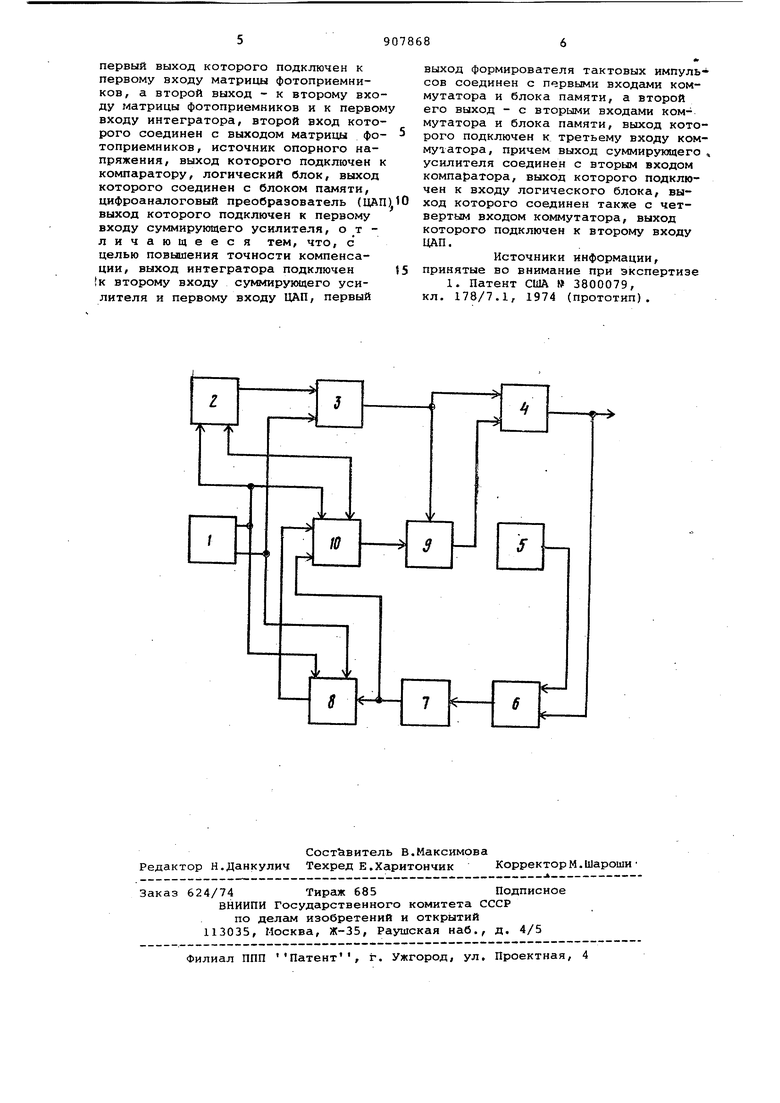

вый выход формирователя тактовых им пульсов соединен с первыми входами коммутатора и блока памяти, а второ его выход - с вторыми входами комму татора и блока памяти, выход которого подключен к третьему входу ком мутатора, причем выход суммирующего усилителя соединен с вторым входом компаратора, выход которого подключ к входу логического блока, выход которого соединен также с четвертьом рходом коммутатора, выход которого подключен к второму входу 1ДАП. На чертеже представлена структурная схема предлагаемого устройства. Устройство компенсации различий в чувствительности матрицы фотоприем ников содержит формирователь 1 тактовых импульсов, матрицу 2 фотоприемников, интегратор 3, суммирующий усилитель 4, источник 5 опорного напряжения, компаратор б, логическое устройство 7, блок 8 памяти, цифроаналоговый преобразователь 9 и коммутатор 10, Устройство работает следующим образом. В режиме записи стандартного фон цифровые входы цифроаналогового преобразователя 9 с помощью коммутатора 10 подключаются к выходу ло гического устройства 7. Последовательно выходные сигналы фоточувстви тельной матрицы 2 интегрируются и поступают на один из входов суммиру ющего усилителя 4, на другой вход суммирующего усилителя 4 подается выходной сигнал цифроаналогового преобразователя 9, Как известно выходное напряжение п - разрядного цифрового преобразователя можно представить в виде %1Х UBX li 2- , (1) напряжение на опорном входе где Ug цифроаналогового преобразователя ; 9; разрядный коэффициент j-ro разряда, который равен нулю если соответствующий разряд является логическим нулем, и единице, если этот разряд является логической единицей. Выходной сигнал суммирующего уси лителя 4 в режиме записи стандартного фона можно выразить как + К Ui , (2) todUi- O J juj где и)ц, - выходное напряжение интег ратора 3 в момент времени, соответствующий развертке j-ro элемента фотоприемной матрищл 2; K(j - коэффициент передачи суммирующего усилителя 4 по первому входу, определяемый из максимального разброса чувствительности элементов матрицы 2; К- - эквивалент двоичного -цифрового кода на входе цифроаналогового преобразователя 9 в десятичной форме. С помощью логического устройства 7 и компаратора 6 за время развертки одного элемента матрицы 2 осуществляется определение цифрового кода на входе циф зоаналогового преобразователя 9,при котором выходной сигнал суммирукнцего усилителя 4 равен напряжению источника 5 опорного напряжения. Эквивалент этого цифрового кода можно выразить как Цд, - к где U( - опорное напряжение на выходе источника 5. Полученный цифровой код записывается в соответствующую ячейку блока 8 памяти. По окончании режима записи стандартного фона цифровые выходы цифроаналогового преобразователя 9 с помощью коммутатора Ю подключаются к выходу блока 8 памяти, и устройство компенсации разницы в чувствительности элементов матрицы фотоприемников переходит в режим компенсации. При этом выходное напряжение суммирующего усилителя 4 можно представить как W «oU«-bg -K,)u,--n.cЦифровой код в каждой ячейке блока 8 памяти обратно пропорционален чувствительности соответствующего элемента матрицы 2, поэтому выходной сигнал суммирукядего усилителя 4 оказывается скомпенсированным. Синхронизация работы блоков устройства компенсации осуществляется формирователем 1 тактовых импульсов. Поскольку операция умножения цифрового сигнала на аналоговый является линейной, в отличие от операции деления аналоговых .сигналов, ошибка компенсации разницы чувствительности датчиков за счет нелинейности блока деления аналоговых сигналов исключается. Использование одного и того же цифроаналогового преобразователя в режимах записи и компенсации исключает также взаимные ощибки при преобразовании аналогового сигнала в цифровой код и обратном преобразовании цифрового кода в аналоговый сигнал. Формула изобретения Устройство для компенсации различий в чувствительности элементов матрицы фотоприемников, содержащее формирователь тактовых импульсов,

первый выход которого подключен к первому входу матрицы фотоприемников, а второй выход - к второму входу матрицы фотоприемников и к первому входу интегратора, второй вход которого соединен с выходом матрицы фо- 5 топриемников, источник опорного напряжения, выход которого подключен к компаратору, логический блок, выход которого соединен с блоком памяти, цифроансшоговый преобразователь (ЦАП)10 выход которого подключен к первому входу суммирующего усилителя, отличающееся тем, что, с целью повышения точности компенсации, выход интегратора подключен 15 (к второму входу суммирующего усилителя и первому входу ЦАП, первый

выход формирователя тактовых импульсов соединен с первыми входами коммутатора и блока памяти, а второй его выход - с вторыми входами коммутатора и блока памяти, выход которого подключен к третьему входу коммутатора, причем выход суммирующего усилителя соединен с вторым входом компаратора, выход которого подключен к входу логического блока, выход которого соединен также с четвертым входом коммутатора, выход которого подключен к второму входу ЦАП.

Источники информации, принятые во внимание при экспертизе

1. Патент США 3800079, кл. 178/7.1, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОМПЕНСАЦИИ РАЗЛИЧИЙ В ЧУВСТВИТЕЛЬНОСТИ ЭЛЕМЕНТОВ МАТРИЦЫ ФОТОПРИЕМНИКОВ | 1995 |

|

RU2108685C1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ РАЗБРОСА ПАРАМЕТРОВ ФОТОЧУВСТВИТЕЛЬНЫХ ЭЛЕМЕНТОВ МНОГОЭЛЕМЕНТНОГО ПРИЕМНИКА | 1992 |

|

RU2025905C1 |

| Устройство для компенсации различий в чувствительности элементов матрицы фотоприемников | 1987 |

|

SU1571793A1 |

| ФОТОПРИЕМНОЕ УСТРОЙСТВО С КОМПЕНСАЦИЕЙ РАЗБРОСА ПАРАМЕТРОВ ФОТОЧУВСТВИТЕЛЬНЫХ ЭЛЕМЕНТОВ | 1992 |

|

RU2065669C1 |

| Преобразователь перемещения в код | 1989 |

|

SU1777240A1 |

| Вихретоковый дефектоскоп | 1983 |

|

SU1103141A1 |

| Устройство для регистрации информации | 1982 |

|

SU1167635A1 |

| Способ компенсации неравномерности видеосигнала матричного фотоприемника | 1982 |

|

SU1117858A1 |

| СПОСОБ КОМПЕНСАЦИИ РАЗБРОСА ПАРАМЕТРОВ ФОТОЧУВСТВИТЕЛЬНЫХ ЭЛЕМЕНТОВ ФОТОПРИЕМНОГО УСТРОЙСТВА | 1992 |

|

RU2105427C1 |

| Термоанемометр | 1979 |

|

SU834524A1 |

Авторы

Даты

1982-02-23—Публикация

1980-04-21—Подача