Фиг.1

Изобретение относится к телеви- д|ению и может быть использовано в системах автоматического регулирования в системах технического зрения Промышленных роботов, дефектоскопии, радиолокации.

Целью изобретения является повы- в1ение надежности работы устройства при повышений тактовой частоты.

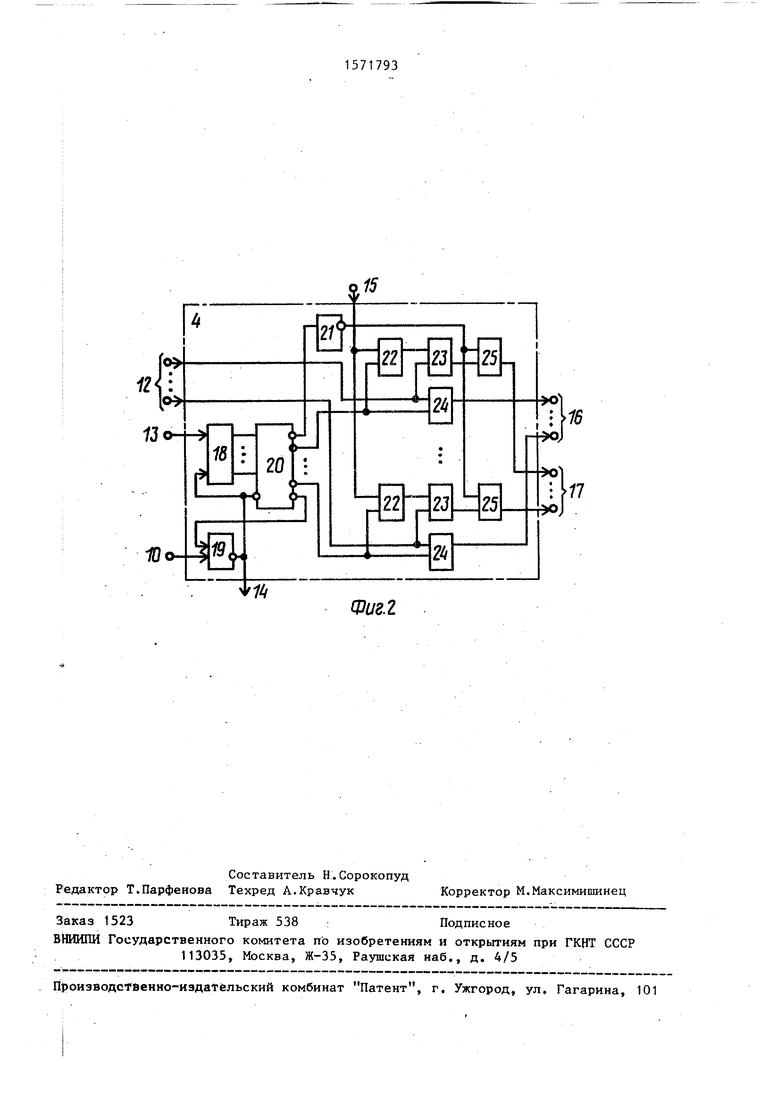

На фиг.1 представлена структурная электрическая схема предлагаемого устройства; на фиг.2 - структурная электрическая схема логического блока устройства.

Устройство для компенсации раз- в чувствительности элементов матрицы фотоприемников содержит Сфиг.1) матрицу 1 фотоприемников, С|инхрогенератор 2, интегратор 3,логический блок 4, блок Ь памяти, п- разрядный цифроаналоговый преобразователь (ЦАП) 6, суммирующий усилитель 7, источник 8 опорного напряжения, компаратор 9, вход 10 запуска выход 11.

Логический блок 4 (фиг.2) имеет второй информационный вход 12, син- Хровход 13, управляющий выход 14, Йервый информационный вход 15, второй информационный выход 16, первый Информационный выход 17 и содержит с{четчик 18 кадров, триггер 19, де- йифратор 20 с (п+2)-мя выходами, инвертор 21, п цепей, каждая из которых состоит из первого элемента pJJIH 22, первого элемента И 23, второго элемента И 24 и второго элемен- ta ИЛИ 25.

Матрица 1 и интегратор 3 предназначены для формирования видеосигнала исследуемого изображения. В качестве матрицы 1 могут применяться, например, ПЗС-матрицы или фотодиодные матрицы. Синхрогенератор 2 предназначен для управления работой формирователя видеоканала и блока памяти и вырабатывает необходимую для Этого синхросмесь импульсов, тактовые импульсы.

Разрядность ЦАП 6 определяется разрядностью кода коррекции,хранимог В блоке 5 памяти. ЦАП 6 должен имет необходимое быстродействие, определемое циклом формирования одного элемента изображения, должен быть перемножающего типа и иметь аналоговый Вход.

Устройство работает следующим образом.

Существует два режима работы: режим записи стандартного фона и режим коррекции. В режиме записи стандартного фона устройство осуществляет формирование, за счет аналого-цифрового преобразования сигнала, и запись

в блок Ь памяти коэффициентов, характеризующих чувствительность каждой ячейки матрицы 1. При этом на фоточувствительную поверхность матрицы 1 проецируется равномерное фоновое

г изображение. В режиме коррекции ви« деосигнала по сформированным в предыдущем режиме коэффициентам осуществляется компенсация различий в чувствительности элементов матрицы фотоприемников.

В любом режиме работу под воздействием синхронизирующих и управляющих сигналов с выхода синхрогенератора 2 матрицей 1 и интегратором 3 осущест5 вляется формирование видеосигнала изображения. Видеосигнал поступает на первый вход суммирующего усилителя 7 к на аналоговый вход перемножающего ЦАП 6. Тактовые импульсы,

0 соответствующие в каждый момент времени выбираемой ячейке матрицы 1, поступают на входы блока 5 памяти. На его информационных выходах формируются коды, которые через логический блок 4 поступают на цифровые входы ЦАП 6 и управляют коэффициентом передачи напряжения с его аналогового входа на выход.

В режиме записи стандартного фона Q с выхода интегратора 3 на первый

вход суммирующего усилителя 7 и аналоговый вход ЦАП 6 от каждой ячейки фоточувствительной матрицы 1 последовательно во времени поступает на5 пряжение , которое зависит от яркости стандартного фона и чувст- вительности данной ячейки. Как известно, перемножающий ЦАП формирует

5

50

на своем выходе напряжение и МП Ujx -la- -2

где а. - коэффициент i-того разряда

кода ЦАПJ . п - число разрядов кода.

Это напряжение поступает на второй вход суммирующего усилителя 7, ид выходе которого будет сигнал

Uex. К0 + UL-К

ех лн

KNгде .К - коэффициент передачи суммирующего усилителя 7 по первому входу, определяемый максимальным разбросом чувствительности матрицы 1; эквивалент цифрового кода на входе ЦАП, учитывающий коэффициент передачи суммирующего усилителя 7 по второму входу.

Напряжение с выхода суммирующего усилителя 7 сравнивается в компараторе 9 с опорным напряжением, поступающим с выхода источника 8 опорного напряжения. Результат сравнения поступает на первый вход логического блока 4. Методом последовательных приближений за п циклов (за п кадров) логический блок 4 формирует на своем втором информационном выходе код коррекции чувствительности каждой ячейки, который при подаче его на вход ЦАП 6 приводит к выполнению равенства опорному напряжению Uon , напряжений видеосигнала от каждой ячейки матрицы, прошедших через суммирующий усилитель 7

и,

U Кя + U

К.

on в о °вх 1Чм Из этого выражения можно найти эквивалент цифрового кода KN который для каждой фоточувствительной ячейки матрицы 1 в конце работы устройства в режиме записи стандартного фона будет выработан на выходах логического блока 4 и записан в соответствующую ячейку блока 5 памяти

и

оп

US,

КоЕсли теперь в режиме коррекции видеосигнала с выхода интегратора 3 на входы ЦАП 6 и суммирующего уси- .лителя 7 будет поступать видеосигнал исследуемого изображения UBX , то на выходах суммирующего усилителя 7 будет лолучен скорректированный по чувствительности каждой ячейки матрицы видеосигнал

иеых21 и (и°п

Ч

+ UBX KN UBX.K0 +

- KJ U.

U0n

о JB ц

6Х

В предлагаемом устройстве в режиме записи стандартного фона методом последовательных приближений осуществляется аналого-цифровое преоб0

5

0

5

0

5

0

5

0

5

разование сигнала каждой ячейки матрицы 1 в n-разрядный код коррекции. Осуществляется это следующим образом. От внешнего устройства на вход 10 запуска приходит сигнал, перебрасывающий триггер 19 в состояние логической единицы. С выхода триггера 19 на управляющий выход 14 логического блока 4 поступает сигнал, который разрешает запись информации в блок 5 памяти. В результате устройство устанавливается в режим записи стандартного фона. Начинается цикл предварительной нормализации содержимого блока 5 памяти. Он заключается в записи во все ячейки блока 5 памяти кодов 11 1 ... 1 и продолжается в течение времени формирования одного кадра. Логический сигнал с выхода триггера 19 поступает на вход обнуления счетчика 18 и стробирую- щий вход дешифратора 20. Счетчик 18 получает возможность считать кадровые синхроимпульсы, поступающие со втор ого выхода синхрогенератора 2 на синхровход 13 логического блока 4. Одновременно на первом выходе дешифратора 20 появляется сигнал логического нуля, который, пройдя через инвертор 21, в сигнала логической единицы поступает на входы вторых элементов ИЛИ 25 всех п цепей. Это приводит к установлению на их выходах логических единиц, которые будут поданы с первого информационного выхода 17 логического блока 4 на информационные входы блока 5 памяти. В блоке 5 памяти за время этого цикла (кадра) по всем ячейкам будут записаны максимальные коды, т.е. коды 1 1 1 ... 1 .

С приходом второго кадрового синхроимпульса на синхровход 13 логического блока 4 счетчик 18 переключается в новое состояние, в соответствии с которым на втором выходе дешифратора 20 появляется сигнал логического нуля. Начинается проверка и формирование по ее результатам старшего разряда кодов коррекции чувствительности всех ячеек. Коды коррекции с выхода блока 5 памяти поступают на второй информационный вход 12 логического блока 4. Поскольку все выходы дешифратора 20, кроме второго, находятся в состоянии логической единицы, то соответственно все разряды кодов коррекции, кроме

первого, поступают через открытые элементы И 24 на второй информационную выход 16 логического блока 4 и алее на цифровые входы ЦАП 6. Второй элемент И 24, на который с выхода блока памяти поступает старший раз- рд кода коррекции всех ячеек мат- 1, находится в закрытом состоянии и на его выходе принудительно ормируется логический ноль. В тече- нЬе времени второго кадра, в котором проверяется старший разряд кодов коррекции всех ячеек матрицы 1, на в|ходы ЦАП 6 подаются коды 011...1. По результатам сравнения в компараторе 9 напряжения с выхода суммирующего усилителя 7 и напряжения Источника 8 опорного напряжения на выходе компаратора 9, а следовательно, на входе 15 логического бло- К|а 4, формируется сигнал логического нуля или логической единицы. Напри- , если напряжение с выхода сум- Нирующего усилителя больше опорного, То на входе 15 появляется логический ноль, и наоборот. Сигнал с вы- компаратора 9, пройдя через открытый только в старшем (в данном 4икле) разряде ключ на элементе ИЛИ 42, вместе с неизменными остальными разрядами кода коррекции подается tfa информационные входы блока 5 па- и записывается в текущую ячейку г1амяти.

После завершения проверки и записи Зтаршего разряда кодов коррекции всех чеек матрицы 1 следующим кадровым Синхроимпульсом счетчик 18 переводится в новое состояние, и на следующем выходе дешифратора 20 появляется логический ноль. Повторяется процедура подачи через логический блок 4 на цифровые входы ЦАП 6 кодов коррекции из блока 5 памяти, но уже с принудительной установкой в ноль второго разряда кода коррекции. Остальные разряды кодов проходят на входы ЦАП 6 без изменений. По сигналу с йыхода компаратора 9 логическим блоком 4 код коррекции проверяемой ячейки либо переписывается в блок 5 памяти без изменений, либо записывается с установкой в логический ноль йроверяемого в данном цикле разряда. Количество циклов проверки равно разрядности кодов коррекции (п). После проверки всех разрядов кодов коррекции кадровый синхроимпульс пере-

1571793

брасывает

10

15

20

25

30

35

40

45

50

55

состояние ноль появл ходе дешиф переводит запретив возможнос 5 памяти. закончен. коррекции

В режи с выхода вии с ном момент вр рез откры ЦАП 6 пост щем режим ствительн соответст аналоговым мирующим коррекция ходное на

и,

в

где К - к ви

ны

Таким нение логи записать ментов ма за п кадр требования при неизм режимах - и коррекци ется скор ния с матр

Форму

Устройс личий в чу матрицы фо последоват ратор, вхо выходу мат мирующий у рой вход к ду источни гический рядньй циф тель, анал ключен к в к второму теля, и си

8

0

счетчик 18 в следующее состояние, при котором логический ноль появляется уже на (п+2)-ом выходе дешифратора 20. Триггер 19 переводится в исходное состояние, запретив по управляющему выходу 14 возможность перезаписи кодов в блоке 5 памяти. Цикл настройки устройства закончен. Начинается работа в режиме коррекции видеосигнала.

В режиме коррекции видеосигнала с выхода блока Ь памяти в соответствии с номером выбираемой в данный момент времени ячейки матрицы 1 через открытые элементы И 24 на входы ЦАП 6 поступают полученные в предыдущем режиме работы коды коррекции чувствительности элементов матрицы 1. В соответствии с этими кодами цифро- аналоговым преобразователем 6 и суммирующим усилителем 7 осуществляется коррекция видеосигнала. При этом выходное напряжение равно

5

0

5

0

5

0

5

и,

U,

К,

вых вх

где К - коэффициент коррекции чувствительности ячейки, рав- Uon

ный

I

Таким образом предлагаемое выполнение логического блока 4 позволяет записать коды коррекции для всех элементов матрицы 1 не за один кадр, а за п кадров. При этом снижаются требования к быстродействию ЦАП 6 при неизменной синхронизации в двух режимах - записи стандартного фона и коррекции. В результате повышается скорость считывания изображения с матрицы 1 без срыва работы ЦАП.

Формула изобретения

Устройство для компенсации различий в чувствительности элементов матрицы фотоприемников, содержащее последовательно соединенные интегратор, вход которого подключен к выходу матрицы фотоприемников, суммирующий усилитель, компаратор, второй вход которого подключен к выходу источника опорного напряжения, логический блок и блок памяти, п-раз- рядньй цифроаналоговый преобразователь, аналоговый вход которого подключен к выходу интегратора, а выход - к второму входу суммирующего усилителя, и синхрогенератор, первый выход

которого подключен к первому синхро- входу матрицы фотоприемников и блока памяти, а второй выход подключен к второму синхровходу матрицы фотоприемников и блока памяти и входу сброса интегратора, причем выход суммирующего усилителя является выходом устройства, отличающееся тем, что, с целью повышения надежности работы устройства при повышении тактовой частоты, логический блок дополнительно имеет второй информационный вход, который подключен к выходу блока памяти, синхровход, который подключен к второму выходу син- хрогенератора, вход запуска, второй информационный выход, который подключен к входу n-разрядного цифроанало- гового преобразователя, и управляющий выход, который подключен к управляющему входу блока памяти, и выполнен из счетчика кадров, дешифратора с (п + 2)-мя выходами, триггера, инвертора и п цепей, каждая из которых содержит последовательно соединенные первый элемент ИЛИ, первый элемент И и второй элемент ИЛИ, а также второй элемент И, причем счетный вход счетчика кадров является синхровходом логического блока, первый вход триггера является входом запуска логического блока, выход триггера подключен к входу запуска счет0

5

0

5

0

чика и стробирующему входу дешифратора и является управляющим выходом логического блока, выходы счетчика кадров подключены к информационным входам дешифратора, первый выход дешифратора подключен через инвертор к второму входу второго элемента ИЛИ каждой из п цепей, каждый выход дешифратора со -второго по (п+1)-й подключен к первым входам первого элемента ИЛИ и второго элемента И соответствующей цепи, (п+2)-й выход дешифратора подключен к второму входу триггера, вторые входы первого элемента ИЛИ каждой из п цепей объединены и являются первым информационным входом логического блока, выходы второго элемента ИЛИ каждой из п цепей объединены в первую п-разряд- ную информационную шину, которая является первым информационным выходом логического блока, выходы вторых элементов И каждой из п цепей объединены во вторую n-разрядную информационную шину, которая является вторым информационным выходом логического блока, соединенные вторые входы первого и второго элементов И каждой из п цепей объединены в третью n-разрядную информационную шину, которая является вторым информационным входом логического блока.

т

Фиг. 2

Изобретение относится к телевидению. Цель изобретения - повышение надежности работы устройства при повышении тактовой частоты. Устройство содержит матрицу 1 фотоприемников, синхрогенератор 2, интегратор 3, логический блок 4, блок памяти 5, N-разрядный ЦАП 6, суммирующий усилитель 7, источник 8 опорного напряжения и компаратор 9. Устройство имеет два режима работы: режим записи стандартного фона и режим коррекции. В режиме записи устройство осуществляет формирование за счет аналого-цифрового преобразования сигнала и запись в блок памяти 5 коэффициентов, характеризующих чувствительность каждой ячейки матрицы 1. При этом на фоточувствительную поверхность матрицы 1 проецируется равномерное фоновое изображение. В режиме коррекции видеосигнала по сформированным в предыдущем режиме коэффициентам осуществляется компенсация различий в чувствительности эл-тов матрицы 1 фотоприемников. 2 ил.

| Патент США № 3800079, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для компенсации различий в чувствительности элементов матрицы фотоприемников | 1980 |

|

SU907868A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-06-15—Публикация

1987-10-08—Подача