(Б) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ПАРАМЕТРОВ ЭКСПОНЕНЦИАЛЬНЫХ ФУНКЦИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и управления городским электротранспортом | 1983 |

|

SU1120392A1 |

| Устройство для измерения среднеквадратического значения напряжения | 1988 |

|

SU1670616A2 |

| Устройство для анализа логических состояний | 1980 |

|

SU1096648A1 |

| Устройство для контроля и управления технологическим процессом тренировки и испытаний фотоэлектронных умножителей | 1986 |

|

SU1325516A1 |

| Устройство для контроля и управления технологическими процессами испытаний и тренировки фотоэлектронных умножителей | 1988 |

|

SU1517041A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1608740A1 |

| ИМИТАТОР РЕАЛИЗАЦИИ СЛУЧАЙНЫХ ИЗМЕНЕНИЙ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 1995 |

|

RU2099863C1 |

| Анализатор частотного спектра | 1980 |

|

SU900209A1 |

| АВТОМАТИЧЕСКИЙ СЛЕДЯЩИЙ ДЕЛИТЕЛЬ ПЕРИОДОВ ИМПУЛЬСНЫХ СИГНАЛОВ | 1992 |

|

RU2105410C1 |

| Адаптивный коммутатор телеизмерительной системы | 1988 |

|

SU1552217A1 |

I

Предлагаемое изобретение относится к вычислительной и преобразовательной технике и может быть использовано для исследования параметров экспоненциальных функций.

Известно устройство для измерения логарифмического декремента колебаний 1 }.

Однако устройство не позволяет определить величину f, характеризующую параметры цепи, влияющие на затухание сигнала, а лишь констатирует сам факт затухания и определяет его декремент. Кроме того устройство не позволяет прогИозировать значение экспоненциальной функции во времени.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее логические элементы, переключатели блок умном ения, цифроаналоговый преобразователь, счетчики и блок сравнения 2 .

Однако при помощи этого устройство можно лишь вычислять лога эиф мические и показательные функции по заданному значению основания (степени) функции.

Цель изобретения - расширение области применения устройства.

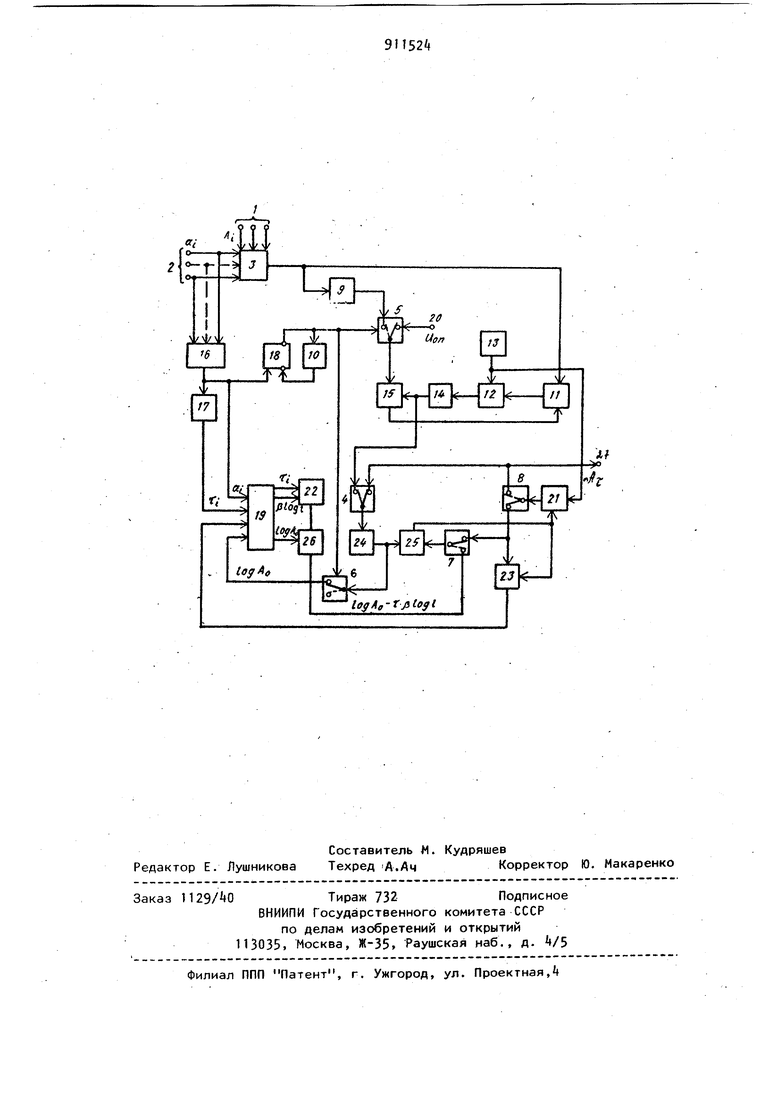

Поставленная цель достигается тем, что в устройство для вычисления параметров экспоненциальных функций, содержащее два переключателя, умножитель, первый элемент И, логарифмЗтор, два счетчика, первую схему сравнения и цифроаналоговый преобразователь , причем выход логарифматора соединен с первым входом первой схемы сравнения, вход логарифматора соединен с выходом первого переключателя, выход первой схемы сравнения соединен с первым входом первого счетчика, информационный выход устройства соединен с первыми входами первого и второго переключателей, введены коммутатор. 3 элемент ИЛИ, таймер, блок памяти, третий, четвертый и пятый переключа тели, триггер, два элемента задержки, генератор импульсов, вычитатель вторая схема сравнения и делитель, примем первая и вторая группы входо коммутатора являются соответственно группой информационных и группой управляющих входов устройства, .груп па управляющих входов устройства соединена с группой входов элемента ИЛИ, выход которого соединен с единичным входом триггера, с первым входом блока памяти и с входом таймера, выход которого соединен со вторым входом блока памяти, выход коммутатора соединен с первым входо второй схемы сравнения и через первый элемент задержки с первым входом третьего переключателя, нулевой выход триггера соединен с входом второго элемента задержки, с управляющим входом третьего переключателя и с управляющим входом четверто переключателя, выход второго эле мента задержки соединен с нуле вым входом триггера, первый и второй выходы блока памяти соединены с первым и вторым входами умножителя, выход которого соединен с первым входом вычитателя второй вход которого соединен с третьим выходом блока памяти, трети и четвертый входы блока памяти соединены соответственно с выходами делителя и с первым выходом четвертого переключателя, второй вход третьего переключателя соединен с выходом опорного напряжения устройства, выход третьего переключателя соединен с первым входом цифроаналогового преобразователя, второй вход которого соединен с выходом второго счетчика и со вторым входом первого переключателя, выход генера тора импульсов соединен с первым входом элемента И и со вторым входом первого счетчика, выход элемента И соединен с входом второго счет чика, второй вход элемента И соединен с выходом второй схемы сравнени второй вход которой соединен с выхо дом цифроаналогового преобразовател выход первого счетчика соединен со вторым входом второго переключателя выход которого соединен с первым входом делителя и с первым входом пятого переключателя, второй вход делителя соединен с выходом первой схемы сравнения, выход вычитателя соединен со вторым входом пятого переключателя, выход которого соединен со вторым входом первой схемы сравнения. На чертеже приведена структурная схема устройства. Устройство содержит группу информационных входов 1 устройства, группу управляющих входов 2 устройства, коммутатор 3, переключатели -8, элемента 9 и 10 задержки, схема 11 сравнения, элемент И 12, генератор 13 импульсов, счетчик И, цифроаналоговый преобразователь 15 элемент ИЛИ 16, таймер 17, триггер 18, блок 19 памяти, вход 20 отпорного напряжения устройства, счетчик 21, умножитель 22, делитель 23, логарифматор 2, схема 25 сравнения, вычитатель 26, информационный выход 27 устройства. Коммутатор 3 предназначен для подачи входных сигналов с группы входов 1 под управлением сигналов группы входов 2. Элемент задержки 9 предназначен для задержки входных сигналов по отношению к сигналам с выхода счетчика 1, схема 11 сравнения предназначена для сравнения входного сигнала с сигналов с выхода преобразователя 15- Генератор 13 импульсов и элемент И 12 предназначены для подачи тактовых сигналов на вход преобразователя 15« Элемент ИЛИ 16 предназначен для запуска таймера 17i который в свою очередь обеспечивает временную диаграмму работы блока 19 памяти. Триггер 18 предназначен для переключения переключателей 5 и 6. Элемент 10 задержки предназначен для сброса триггера 18, вход 20 - для подачи опорного напряжения на вход устройства. АО ер функция исследуемого сигнала значения исследуемого сигнала, начальное в момент t, измеренное в момент t и вычисленное устройством в момент т Ь - параметр цепи, учитывающий форму экспоненты;( - время; время задержки формируемые соответственноэлементами 9 и 10 задержки; УОП const опорный сигнал N N АО до/А4: .максимальная емкость счетчика 14 и коды цифровых эквива лентов аналоговых величин А,иА,/АЬ Устройство работает следующим об разом. В работе устройства можно выделить три этапа: первый - вычисление логарифма log АО начального значения А исследуемого сигнала А; второй - вычисление логарифма отношени log -д- и параметра (% log 6 экспонен циальной функции; третий - вычислен А исследуемого сигнала А. Первый этап. Переключатели 8 устанавливают в положения, указанны на чертеже. При подключении входа схемы 11 сравнения через коммутатор 3 к соот ветствующему входу 1 с исследуемым сигналом А, определяемом стробирующим импул1гсов с входа 2, происхо дит преобразование аналоговой.величины А в цифровой эквивалент с последующим вычислением его логарифма log Ag в логарифматоре 2 и записью значения log А в блок 19 памяти через переключатель 6 (зресь и далее для простоты объяснений аналоговые значения А и их цифровые эквиваленты N. будут обозначены одним и тем же символом А). Через время задержки t на выходе триггера 18 появляется сигнал, который переводит переключатели 5 и 6 в положения, указанные пунктиром на чертеже, обозначающие подготовку ко второму этапу работы. Второй этап. Переключатели 5 и 6 в положениях, указанных пунктиром, переключатели ,7,8 в положениях, указанных на чертеже. На вход преобразователя 15 и вход 20 поступают соответственно сигналы AV и (для простоты объяснений А- и А). На выходе преобразователя 1.5 формируется значение - Aiirf пропорциональное отношению , которое далее логарифмируется в логарифматоре 24. В результате этого на первый вход схемы 25 сравнения поlogступает значение и счетчик 21 заполняется импульсами с генератора 13 до момента равенства значений кодов на первом и втором входах схемы 25 сравнения в соответствии с выражением Iog - tPlog в момент равенства которого вход второго счетчика 2t заблокируется- и результат деления jbEog E с выхода целителя 23 переписывается в блок 19 памяти.. Третий этап. Переключатели ,6, 7,8 переведены в положения, указанные на чертеже пунктиром. С выходов блока 19 памяти и на входы умножителя 22 и вычитателя 26 поступают соответственно значения f /1 EoOt и log A(j, в результате чего на втором входе блока 25 сравнения значение кода равно A -TT-I logР- Уравновешивание кодов на первом и втором входах схемы 25 сравнения осуществляют аналогичным второму этапу заполнения импульсами второго счетчика 21. В результате этого появление сигнала равенства на выходе схемы 25 сравнения фиксирует в счетчике 21 значение Ар, которое и определяет на выходе 27 устройства конечный результат вычислений «-Р % Применрне изобретения позволяет расширить область применения устойства. Формула изобретения Устройство для вычисления параетров экспоненциальных функций, одержащее два переключателя,умноитель, элемент И, логарифматор,два четчика, первую схему сравнения и 7 цифроаналоговый преобразователь, причем лога рифма тора соединен с первым входом первой схемы сравне ния, вход логарифматора соединен с выходом первого переключателя,выход первой схемы сравнения соединен с первым входом первого счетчика,ин формационный выход устройства соеди нен с первыми входами переого и второго переключателей, о т л ича щееся тем, что, с целью расширения области применения устройства,оно содержит коммутатор, элемент ИЛИ, таймер, блок памяти, третий,, четвертый и пятый переключатели, триггер, два элемента задержки, генератор импульсов, вычитатель, вторую схему сравнения и делитель, причем первая и вторая группы входов коммутатора являются соответственно группой информационных и группой управляющих входов устройства, группа управляющих входов устройства соединена с группой входов элемента ИЛИ, выход которого соединен с единичным входом триггер с первым входом блока памяти и с входом таймера, выход которого соединен со вторым входом блока памяти выход коммутатора соединен с первым входом второй схемы сравнения и через первый элемент задержки с первым входом третьего переключателя, нулевой выход триггера соединен с входом второго элемента задержки, с управляющим входом третьего переключателя и с управляющим входом четвертого переключателя, выход вто рого элемента задержки соединен с нулевым входом триггера, первый и второй выходы блока памяти соединены с первым и вторым входами умножи теля, выход которого соединен с первым входом вычитателя, второй вход которого соединен с третьим выходом блока памяти, третий и четвертый входы блока памяти соединены соответственно с выходом делителя и с первым выходом четвертого переключателя, второй вход третьего переключателя соединен с выходом опорного напряжения устройства, выход третьего переключателя соединен с первым входом цифроаналогового преобразователя, второй вход которого соединен с выходом второго счетчика и со вторым входом первого переключателя, выход генератора импульсов соединен с первым входом элемента И и со вторым входом первого счетчика, выход элемента Л соединен с входом второго счетчика, второй вход.элемента И соединен с выходом второй схемы сравнения, второй вход которой соединен с выходом цифроаналогового преобразователя, выход первого счетчика соединен со вторым входом второго переключателя, выход которого соединен с первым входом делителя и с первым входом пятого переключателя, второй вход делителя соединен с выходом первой схемы сравнения, выход вымитателя соединен со вторым входом пятого переключателя, выход которого соединен со вторым входом первой схемы сравнения. Источники информации, принятые во внимание при экспертизе . 1.Авторское свидетельство СССР № i 8l9l8, кл. G 06 F 3/00, . 2.Авторское свидетельство СССР № , кл.G Об F 3/00, 1976.

Авторы

Даты

1982-03-07—Публикация

1980-01-04—Подача