11

Изобретение относится к автоматике и вычислительной технике и .может быть использовано в производстве фотоэлектронных приборов.

Цель изобретения - повьшение точности устройства.

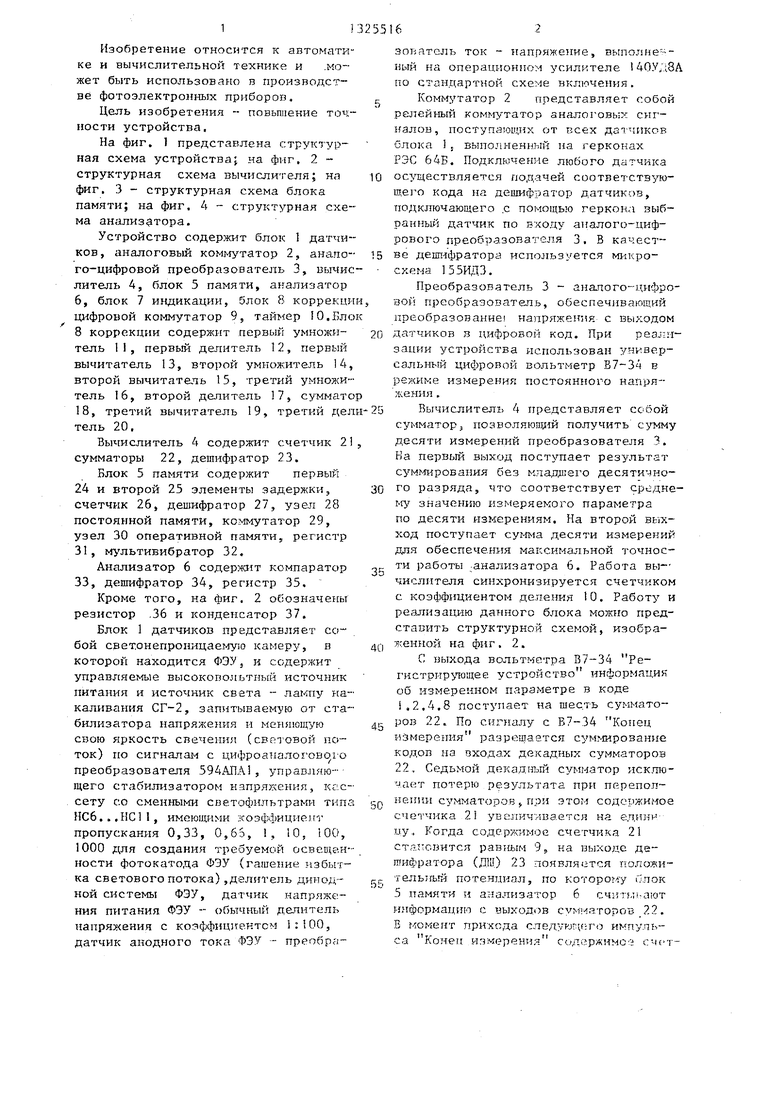

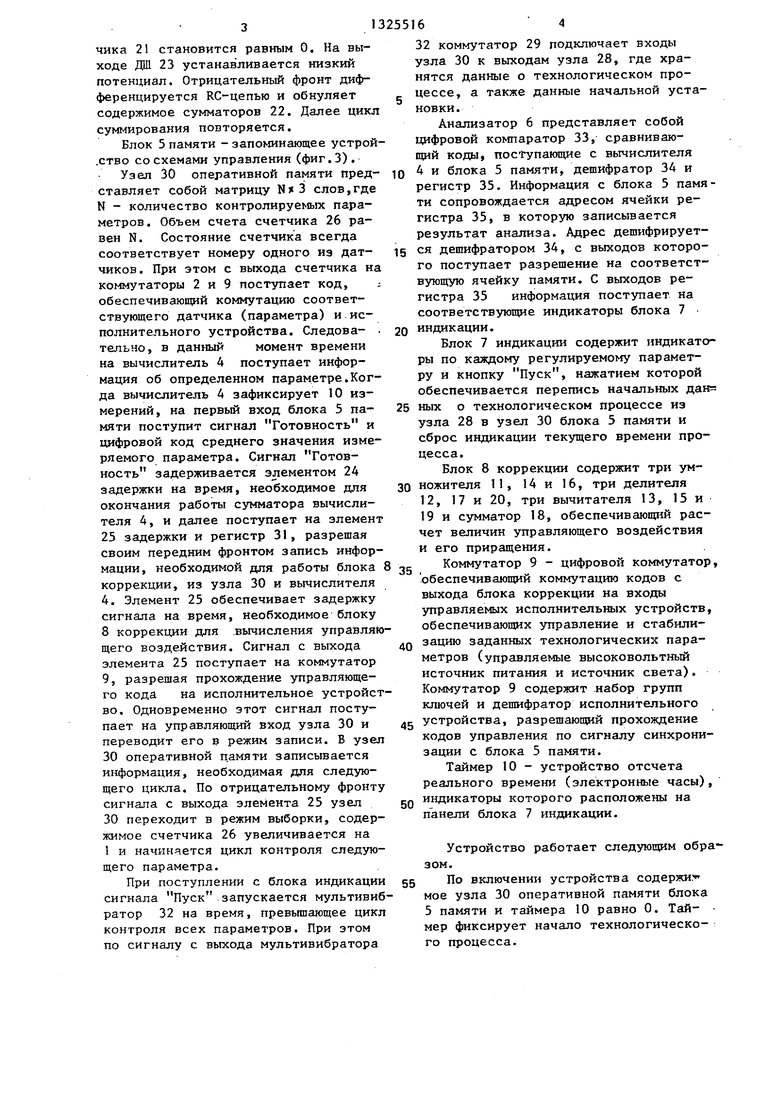

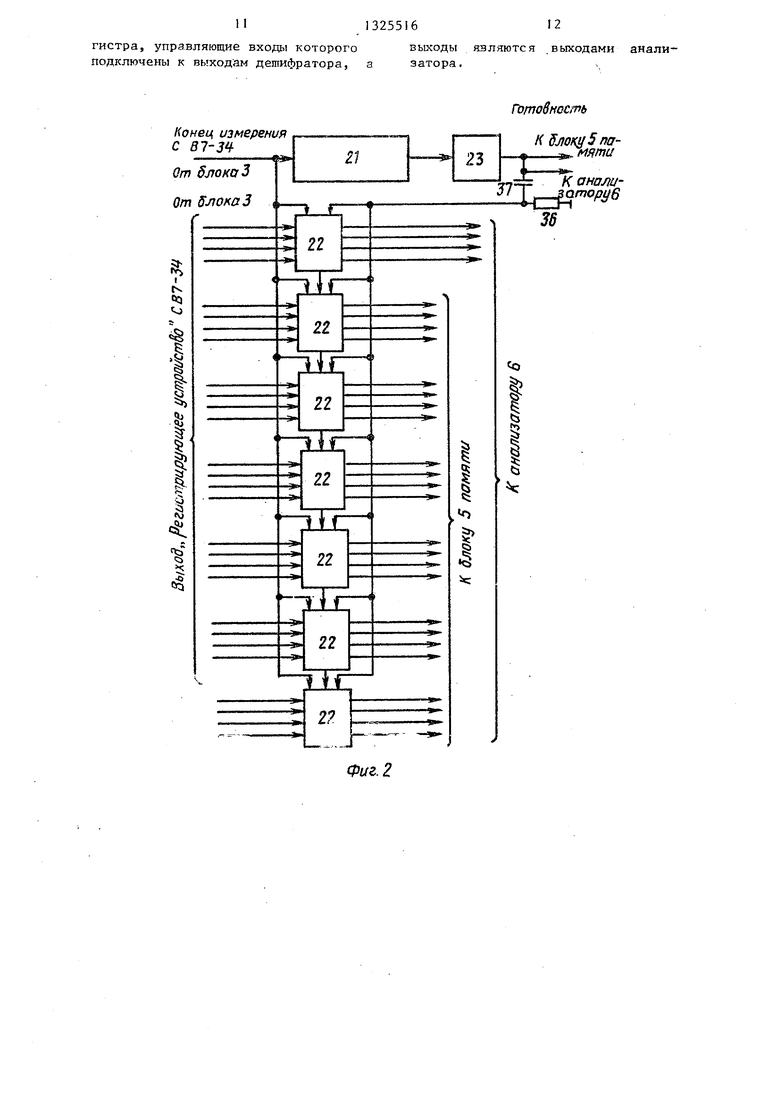

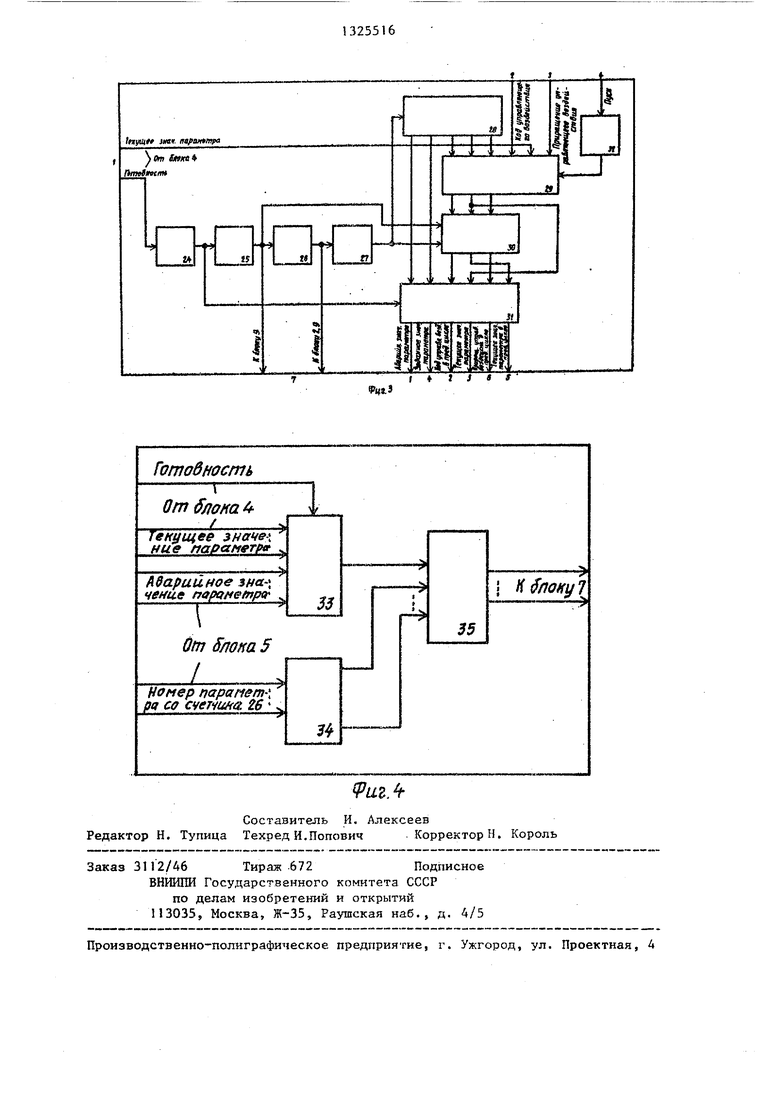

На фиг. 1 представлена структурная схема устройства.J на ф1-1Г, 2 - структурная схема вычислителя; на фиг. 3 - структурная схема блока памяти; на фиг. А - структурная схема ангализэтора.

Устройство содержит блок 1 датчиков, аналоговый коммутатор 2, анапо- го-цифровой преобразователь 3, вычис литель 4, блок 5 памяти, анализатор 6, блок 7 индикации, блок 8 коррекци цифровой коммутатор 9, таймер О,Бло 8 коррекции содержит .первый умножи- тель 11, первый делитель 12, первый вычитатель 13, второй умножитель 14, второй вычитатель 15, третий умножитель 6, второй делитель 17, суммато 18, третий вычитатель 19, третий дел тель 20.

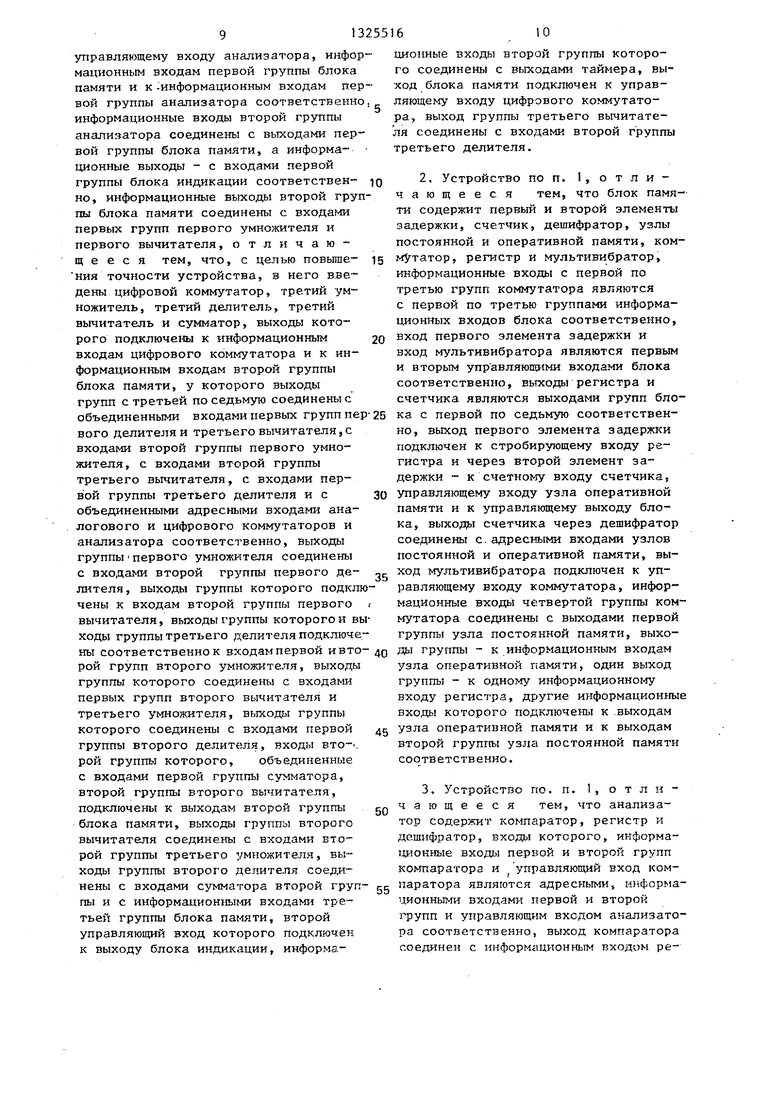

Вычислитель 4 содержит счетчик 21 сумматоры 22, дешифратор 23.

Блок 5 памяти содержит первый 24 и второй 25 элементы задержки, счетчик 26, дешифратор 27, узел 28 постоянной памяти, ко:ммутатор 29, узел 30 оперативной памяти, регистр 31, мультивибратор 32.

Анализатор 6 содержит компаратор 33, дешифратор 34, регистр 35.

Кроме того, на фиг. 2 обозначены резистор .36 и конденсатор 37.

Блок 1 датчиков представляет со бой свет.онепроницаег-гуга камеру, в которой находится ФЭУ, и содержит управляемые высоковольтными источник питания и источник света - лампу накаливания СГ-2, запитываемую от стабилизатора напряжения и меняющую свою яркость свеченнл (световой поток) по сигналам с цифроаналогово го преобразователя 594АПА1, управляющего стабилизатором напряжения, кассету со сменными светофильтрами типа НС6...НС11, имеющими коэффициент пропускания 0,33, 0,65, , 10, 100, 1000 для создания требуемой осве1цен- ности фотокатода ФЭУ (гашение избытка светового потока), делитель динод- ной системы ФЭУ, датчик напряже;- ния питания ФЭУ -- обычный делитель напряжения с коэффициентом , датчик анодного тока ФЭУ - преобра

5

5 0 5

0

g

0 5 0 .-

6

зователь ток напряжение, BbrnojiHe --- ный на операционном усилителе t40УЛ8Л по с андартной схеме включения.

Коммутатор 2 представляет собой релейный коммутатор аналоговых сигналов, HOCTynaiouiTix от всех дап.чиков блока I. выполненный на герконах РЭС 64Б. Подключение любого датчика осуществ.пяется подачей соответствующего кода на дешифратор датчиков, подключающего .с помощью геркона зыб- ранньй датчик по входу аналого-цифрового преобразователя 3. В качестве дешифратора используется микросхема 155ИД.З.

Преобразователь 3 - аналого-цифровой преобразователь, обеспечивающий преобразование напряжения с выходом датчиков в цифровой код. При реализации устройства использован у.нивер- сальный цифровой вольтметр В7-34 в режиме измерения постоянного напря- .

Вычислител:ь 4 представляет собой сумматор3 позволяющий получить сумму десяти измерений преобразователя .3. На первый выход поступает результат сум№-1рования без кладдгего десятичного разряда, что соответствует средне- значению измеряемого параметра по десяти измерениям. На второй вых- ход поступает cyi-n ta десяти измерений для обеспечения максимальной точнос- Т.И работы -анализатора 6. Работа вы- числителя синхронизируется счетчиком с коэффициентом де.пения 10. Работу и реализацию данного блока можно представить структурной схемой, изображенной на фиг. 2.

С выхода вольтметра Ре- гистрир 1ощее устройство информация об измеренном параметре в коде i,2.4.8 поступает на шестъ сумматоров 22. По сигналу с В7-34 Конец измерения разрешается суммирование кодов на входах декадных сумматоров 22., Седьмой дека.дшош сумматор исключает потерю результата при переполнении сумматоро.в , при этом содержимое сиет -п-1ка 2 увеличивается на e.n.tiHv цу., Когда содержимое счетчика 21 стаковится Э, на выходе дешифратора (ДЩ) 23 появляется положительный потенциал, по которому u.rioK 5 памяти и а; ализатор 6 счнть;ьают информацию с выходов сум маторов 22. Б момент прихода следуюг;г;го импу.пь- са Конец измерения содержимо Э с-и т

чика 21 становится равным 0. На выходе да 23 устанав ливается низкий потенциал. Отрицательный фронт дифференцируется КС-цепью и обнуляет содержимое сумматоров 22. Далее цикл суммирования повторяется.

Блок 5 памяти - запоминающее устрой- .ство со схемами управления (фиг.З).

Узел 30 оперативной памяти представляет собой матрицу N л 3 слов,где N - количество контролируемых параметров . Объем счета счетчика 26 равен N. Состояние счетчика всегда соответствует номеру одного иэ датчиков. При этом с выхода счетчика на коммутаторы 2 и 9 поступает код, -. обеспечивающий коммутацию соответствующего датчика (параметра) и исполнительного устройства. Следова- . тепьно, в данный момент времени на вычислитель 4 поступает информация об определенном параметре.Когда вычислитель 4 зафиксирует 10 измерений, на первый вход блока 5 памяти поступит сигнал Готовность и цифровой код среднего значения измеряемого параметра. Сигнал Готовность задерживается элементом 24 задержки на время, необходимое для окончания работы сумматора вычислителя 4, и далее поступает на элемент 25 задержки и регистр 31, разрешая своим передним фронтом запись информации, необходимой для работы блока коррекции, из узла 30 и вычислителя 4. Элемент 25 обеспечивает задержку сигнала на время, необходимое блоку 8 коррекции для .вычисления управляющего воздействия. Сигнал с выхода элемента 25 поступает на коммутатор 9, разрешая прохождение управляющего кода на исполнительное устройство. Одновременно этот сигнал поступает на управляющий вход узла 30 и переводит его в режим записи. В узел 30 оперативной цамяти записывается информация, необходимая для следующего цикла. По отрицательному фронту сигнала с выхода элемента 25 узел 30 переходит в режим выборки, содержимое счетчика 26 увеличивается на 1 и начинается цикл контроля следующего параметра.

При поступлении с блока индикации сигнала Пуск -запускается мультивибратор 32 на время, превышающее цикл контроля всех параметров. При этом по сигналу с выхода мультивибратора

10

15

20

-

8 35 325516 4

32 коммутатор 29 подключает входы узла 30 к выходам узла 28, где хранятся данные о технологическом процессе, а также данные начальной установки.

Анализатор 6 представляет собой цифровой кo mapaтop 33, сравнивающий коды, поступающие с вычислителя 4 и блока 5 памяти, дешифратор 34 и регистр 35. Информация с блока 5 памяти сопровождается адресом ячейки регистра 35, в которую записывается результат анализа. Адрес дешифрируется дешифратором 34, с выходов которого поступает разрешение на соответствующую ячейку памяти. С выходов регистра 35 информация поступает на соответствующие индикаторы блока 7 индикации.

Блок 7 индикации содержит индикаторы по каждому регулируемому параметру и кнопку Пуск, нажатием которой обеспечивается перепись начальных 25 ных о технологическом процессе из узла 28 в узел 30 блока 5 памяти и сброс индикации текущего времени процесса.

Блок 8 коррекции содержит три ум- 30 ножителя 11, 14 и 16, три делителя 12, 17 и 20, три вычитателя 13, 15 и 19 и сумматор 18, обеспечивающий расчет величин управляющего воздействия и его приращения.

Коммутатор 9 - цифровой коммутатор, обеспечивающий коммутацию кодов с выхода блока коррекции на входы управляемых исполнительных устройств, обеспечивающих управление и стабилизацию заданных технологических параметров (управляемые высоковольтный источник питания и источник света). Коммутатор 9 содержит набор групп ключей и дешифратор исполнительного g устройства, разрешающий прохождение кодов управления по сигналу синхронизации с блока 5 памяти.

Таймер 10 - устройство отсчета реального времени (электронные часы), индикаторы которого расположены на панели блока 7 индикации.

40

50

Устройство работает следуюш Им образом.

По включении устройства содержи, мое узла 30 оперативной памяти блока 5 памяти и таймера 10 равно 0. Тай- мер фиксирует начало технологического процесса.

513

При нажатии кнолкич Пуск на блоке 7 индикации в блок 5 памяти поступает сигнал, по которому блок 5 памяти переписьшает данньи; о техно-логическом процессе и данные начапь- ной установки из узла 28 в узел 30. На ког-нчутаторы 2 и 9 начинают поступать коды номеров регулируемых параметров. Коммутаторы 2 и 9 подключают датчики и исполнительные устройства к входу АЦП 3 и выход сумматора 18 блока 8 коррек1дии к третьему входу блока 5 памяти (вход коммутатора 29) При поступлении очер вдного кода номера параметра сигнгш с соответствую щего датчика преобразовывается АЦП 3 в цифровой код, поступающий на вычислитель А. Вычислитель суммирует результат десяти преобразований и среднее значение измеренного парамет ра передает в блок 5. памяти и на анализатор 6. Блок 5 памяти выдает на анализатор 6 код аварийного значеш я регулируемого параметра. Анализатор сравнивает коды и в случае превыопе- ния параметром аварийного значения выдает сигнал на блок 7 индикации, п которому загорается соответству1оп(изЧ индикатор.

Наиболее важными технологическими параметрами ФЗУ являются напряжение питания, освещенность фотокатода, величина динодного тока. Анодный ток ФЗУ в сильной степени зависит от освещенности фотокатода и напря- жения питания, )ициенты влияния величины напряжения на анодньй ток ФЭУ лежат в пределах от 7 до 12, а освещенности - от 4 до 8 и имеют существенный разброс ,цля ФЭУ одного и того же типа. Это оЗуславливает невозможность использования линейшлк методов регулирования при стабилизации их технологических параметров,

...

В изобретениии расчет величины изменения управляющего воздействия, необходимого для стабилизации пара- метра, производится с учетом коэффициента влияния, определяемого по реакции объекта на предыдущее изменение управляющего воздействия по выргше- нию:

KV

ATI-X ..-.где X f, - значение параметра в настоя- щий момент времени;

50 -06 о

35 25

Х„.., - значение параметра до нения управляющего воздействия;

а„Р - вегшчина предыдущего изменения: управляющего воздействия .

Расчет коэффициента влияния К,, производится вычитателем 19 и делителем 20. Значения, необходимые для расчета, поступают на входы блоков из блока 5 памяти.

Расчетная величина изменения управляющего Еюздействия д определяется выражением:

л h VуiJK

л

где Y - величина управляющего воздействия в настоя Ц1- Й момент времени I

Xpg заданное значение параметра. Расчет .величины Д производит- ея умножителем 11, делителем 12, вы- чятатех1ем 13 и умножителем 14. Необходимая информация поступает с блока 5 памяти.

Расчет изменения управляющего воздействия по заданным выражениям позволяет учесть нелинейность характеристики ФЭУ по управляющим воздействиям. Однако техпроцессы при изготовлении ФЭУ производятся при предельных значениях анодных токов и при незначительном перерегулировании происходят перераспределения напряжений питагаш динодной системы ФЭУ, задаваемых резистивным делителем и начинается лавинооЬразь ый рост анодного тока. Поэтому во избежание перерегулирования в расчетную величину изменения управляющего воздействия вводится поправка по выражению -)

где & величина изменения управлян - щего воздействия в данный момент времени.

Квадратичная зависимость шения управляющего воздействия в зависимости от отношения расчетного изменения к его величине оказывает влияние только при выводе параметра в область заданного значения, где

55

отношение

;.

стрет-штся к О и поправна перестает влиять на точность регулирования.

71

Расчет величины 4 производится вычитателем 15, умйожителем 16 и делителем 7.

Величина управляющего воздействия Yj, поступающая на исполнительное устройство, определяется вьфаже- нием

Y,Y+A.

Расчет величины Y производится сумматором 18.

Все величины параметров, необходимые для расчета управляющего воздействия, поступают на блок 8 коррекции из блока 5 памяти в момент передачи среднего значения параметра из вычислителя 4. Через время, необходимое для расчета управляющего воздействия, с блока 5 памяти на коммутатор 9 поступает сигнал, разрешающий прохождение нового управляющего воздействия на исполнительное устройство. После этого блок 5 памяти записывает в свое ОЗУ информацию, необходимую для следующего цикла расче- та управляющего воздействия и выдает на коммутаторы 2 и 9 код номера следующего параметра. Процесс контроля и регулирования этого параметра происходит аналогично.

По заверщении цикла контроля и регулирования по всем параметрам цикл повторяется.

Таким образом, устройство для контроля и управления технологическим процессом тренировки и испытаний фотоэлектронных умножителей, непрерывно контролируя параметры объекта, рассчитывая с наперед заданной точностью их изменения, прогнозируя их изменения к моменту следующего цикла контроля и определяя с учетом этих данных величину управляющего воздействия, обеспечивает точную стабилизацию .и конт

роль технологических параметров испытаний .

Работа предлагаемого .устройства экспериментально проверена при изменении нестабильности испытаний на долговечность и тренировку следующих типов ФЭУ: ФЭУ-148, ФЭУ-ПО, ФЭУ-93, ФЭУ-IU. Погрешность стаби- л 1зации технологических параметров составляет 0,14%. Достижение такой точности стабилизации технологических параметров известным устройством невозможно из-за того, что временные характеристики процесса задаготся кон

8

д 0 5 0

5

0

5

0

5

стантами, что не обеспечивает учет их изменений при изменении условий эксплуатации. Погрешность реального значения временных характеристик в технологическом процессе изготовления ФЭУ может достигнуть нескольких процентов, что и ограничивает точность стабилизации параметров. В предлагаемом устройстве временные параметры учитываются при определении коэффициента влияния в каждом цикле контроля. Имеются временные флуктуа- ции контролируемого параметра, которые не могут быть учтены прогнозированием и влияние которых возрастает пропорционально интервалу контроля. В предлагаемом устройстве влияние указанных факторов сведено к минимуму . за счет обеспечения минимально возможного времени цикла контроля - управления. В известном устройстве интервал контроля может достигать значительной величины; попытка получе-: ния повыщенной точности за счет сужения области номинальных значений контролируемых параметров уменьшает время цикла контроля, но обеспечивает повышение точности только для параметров, имеющих наивысший приоритет за счет уменьшения времени обслуживания параметров с более низкими приоритетами.

Формула изобретения

I. Устройство для контроля и yn-f равления технологическим процессом тренировки и испытаний фотоэлектронных умножителей, содержащее аналоговый коммутатор, аналого-цифровой преобразователь, вычислитель, анализатор, блок индикации, блок памяти и таймер, первый и второй умножители, первый и второй делители и первый и второй вычитатели, информационные

ч,

входы аналогового коммутатора являются входами устройства для подключе- . ния к выходам объекта контроля, выход соединен с информационным входом аналого-цифрового преобразователя, цифровые выходы которого и выход Конец преобразования подключены к информационным и управляющему входам вычислителя соответственно, у которого первый и второй управляющие выходы и информационные выходы первой и второй групп подключены к первому управляющему входу блока памяти.

управляющему входу анализатора, информационным входам первой группы блока памяти и к -информационным входам первой группы анализатора соответственно. информационные входы второй группы анализатора соединены с выходами первой группы блока памяти, а информа- - ционные выходы - с входами первой группы блока индикации соответствен- io но, информационные выходы второй группы блока памяти соединены с входами первых групп первого умножителя и первого вычитателя, отличаюциоиные входы второй группы которого соединены с выходами таймера, выход блока памяти подключен к управляющему входу цифрового коммутатора, выход группы третьего вычитателя соединены с входами второй группы третьего делителя.

2. Устройство по п. 1, отличающее с я тем, что блок памяти содержит первый и второй элементы задержки, счетчик, дешифратор, узлы постоянной и оперативной памяти, ком- щ е е с я тем, что, с целью повыше- 15 мутатор, регистр и мультивибратор, ния точности устройства, в него вве- информационные входы с первой по дены цифровой коммутатор, третий ум- третью групп коммутатора являются ножитель, третий делитель, третий с первой по третью группами информационных входов блока соответственно, 20 вход первого элемента задержки и

вход мультивибратора являются первым и вторым управляющими входами блока

вычитатель и сумматор, выходы которого подключены к информационным входам цифрового коммутатора и к информационным входам второй группы блока памяти, у которого выходы групп с третьей по седьмую соединешлс

соответственно, выходы регистра и счетчика являются выходами групп блообъединенными входами первых групп пер- 25 ка с первой по седьмую соответственвого делителя и третьего вычитателя, с входами второй группы первого умножителя, с входами второй группы третьего вычитателя, с входами пер- в ой группы третьего делителя и с объединенными адресными входами аналогового и цифрового коммутаторов и анализатора соответственно, выходы группы первого умножителя соединены

с входами второй группы первого де- g ход мультивибратора подключен к уп- лителя, выходы группы которого подклю- равляющему входу коммутатора, инфор- чены к входам второй группы первого г мационные входы четвертой группы ком- вычитателя, выходы группы которого и вы- мутатора соелгинены с выходами первой ходы группы третьего делителя подключе- группы узла постоянной памяти, выхо- ны соответственно к входам первой и ВТО-40 Ды группы - к информационным входам

рои групп второго умножителя, выходы группы которого соединены с входами первых групп второго вычитателя и третьего умножителя, выходы группы

которого соединены с входами первой 45 Узла оперативной памяти и к выходам

группы второго делителя, входы вто-ч рой группы которого, объединенные с входами первой группы сумматора, второй группы второго вычитателя, подключены к выходам второй группы блока памяти, выходы группы второго вычитателя соединены с входами второй группы третьего умножителя, вьз- ходы группы второго делителя coep iнены с входами сумматора второй груп- ggпаратора являются адресными, информапы и с информационными входами тре-ционными входами первой и второй

тьей группы блока памяти, второйгрупп и управляющим входом анализатоуправляющий вход которого подключенра соответственно, выход компаратора

к выходу блока индикации, информа-соединен с информационньтм входом рециоиные входы второй группы которого соединены с выходами таймера, выход блока памяти подключен к управляющему входу цифрового коммутатора, выход группы третьего вычитателя соединены с входами второй группы третьего делителя.

2. Устройство по п. 1, отличающее с я тем, что блок памясоответственно, выходы регистра и счетчика являются выходами групп блоно, выход первого элемента задержки подключен к стробирующему входу регистра и через второй элемент задержки - к счетному входу счетчика, управляющему входу узла оперативной памяти и к управляющему выходу блока, выходы счетчика через дешифратор соединены с.адресными входами узлов постоянной и оперативной памяти, выузла оперативной памяти, один выход группы - к одному информационному входу регистра, другие информационные входы которого подключены к .выходам

второй групгп:. узла постоянной памяти соответственно.

3. Устройство по. п. 1, отличающееся тем, что анализатор содержит компаратор, регистр и дешифратор, входы которого, информа- тдионные вход1 первой и второй групп компаратора и управляющий вход ком

гистра, управляющие входы которого подключены к выходам дешифратора, а

13

Фиг. 2

1325516

12

выходы являются выходами анализатора.

Готовнсс/пб

itt.

I t t 1 t t

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и управления технологическими процессами испытаний и тренировки фотоэлектронных умножителей | 1988 |

|

SU1517041A1 |

| Цифровой анализатор спектра | 1985 |

|

SU1256044A1 |

| Устройство для контроля параметров | 1985 |

|

SU1291930A1 |

| Частотный анализатор | 1990 |

|

SU1798630A1 |

| Устройство для обработки и передачи информации учета товарной нефти | 1983 |

|

SU1129625A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ДЛЯ ОПРЕДЕЛЕНИЯ ИНФОРМАЦИОННЫХ СВОЙСТВ ТЕСТА | 1991 |

|

RU2068580C1 |

| СИСТЕМА НАВИГАЦИИ ЛЕТАТЕЛЬНОГО АППАРАТА | 1992 |

|

RU2022356C1 |

| Устройство для определения закона распределения случайной величины | 1986 |

|

SU1425713A1 |

| Устройство для контроля температуры | 1988 |

|

SU1515176A1 |

| Статический анализатор | 1988 |

|

SU1727140A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в производстве фотоэлектронных приборов. Цель изобретения - повышение точности устройства. Устройств.о содержит аналоговый коммутатор 2, аналого-цифровой преобразователь 3, вычислитель 4, анализатор 6, блок индикации 7, блок памяти 5, таймер 10, цифровой коммутатор 9, третий умножитель 16, третий делитель 20, третий вычита- тель 19 и сумматор 18 с их связями. Повышение точности обеспечивается тем, что в процессе технологического управления и контроля сумматором 18 рассчитываются управляющие воздействия, необходимые для стабилизации технологических параметров, как сумма воздействия выданного ранее и поправки, вычисленной умножителем 11, делителем 12, вычитателем 13 и умножителем 14, с учетом реального коэффициента влияния, определяющего прогнозированное влияние реакции параметра на управляющее воздействие по реакции на предыдущие и рассчитываемого (ВычитателеМ 19 и делителем 20, и скорректированного по квадратичной зависимости вычитателем 15 и умножителем 16 для упреждения возможного перерегулирования. 2з.п. ф-лы, 4 ил. л 00 10 ел СП О)

Готобность

От лона /

Текущее зиаче- Hue napKXNfTi

Аварийное зна- чемие nopQHetnpd

От Sftoira S I .

Номер парапет- р9 со суелин 26

иг.

Составитель И. Алексеев Редактор Н. Тупица Техред И,Попович Корректор Н. Король

Заказ 3112/46 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

--

55

I nOKlfl

--

| Усстройство для автоматизированного управления и контроля распределенных объектов | 1973 |

|

SU460530A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для автоматического контроля технологических параметров | 1980 |

|

SU930278A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-07-23—Публикация

1986-03-28—Подача