(54) УСТРОЙСТВО ДЛЯ ПРОВЕРКИ ЛОГИЧЕСКИХ МИКРОСХЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для проверки логических микросхем | 1985 |

|

SU1242864A1 |

| Генератор импульсных сигналов | 1981 |

|

SU980026A1 |

| Согласующее устройство | 1977 |

|

SU660213A1 |

| Устройство для проверки логических микросхем | 1985 |

|

SU1285413A1 |

| Устройство для контроля электрического монтажа | 1990 |

|

SU1794258A3 |

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

| Устройство для контроля логических узлов | 1980 |

|

SU868764A1 |

| Логический пробник | 1990 |

|

SU1839242A1 |

| Функциональный преобразователь | 1980 |

|

SU922797A1 |

| УСТРОЙСТВО ЗАЩИТЫ ИНФОРМАЦИИ ОТ НЕСАНКЦИОНИРОВАННОГО ДОСТУПА | 2003 |

|

RU2263345C2 |

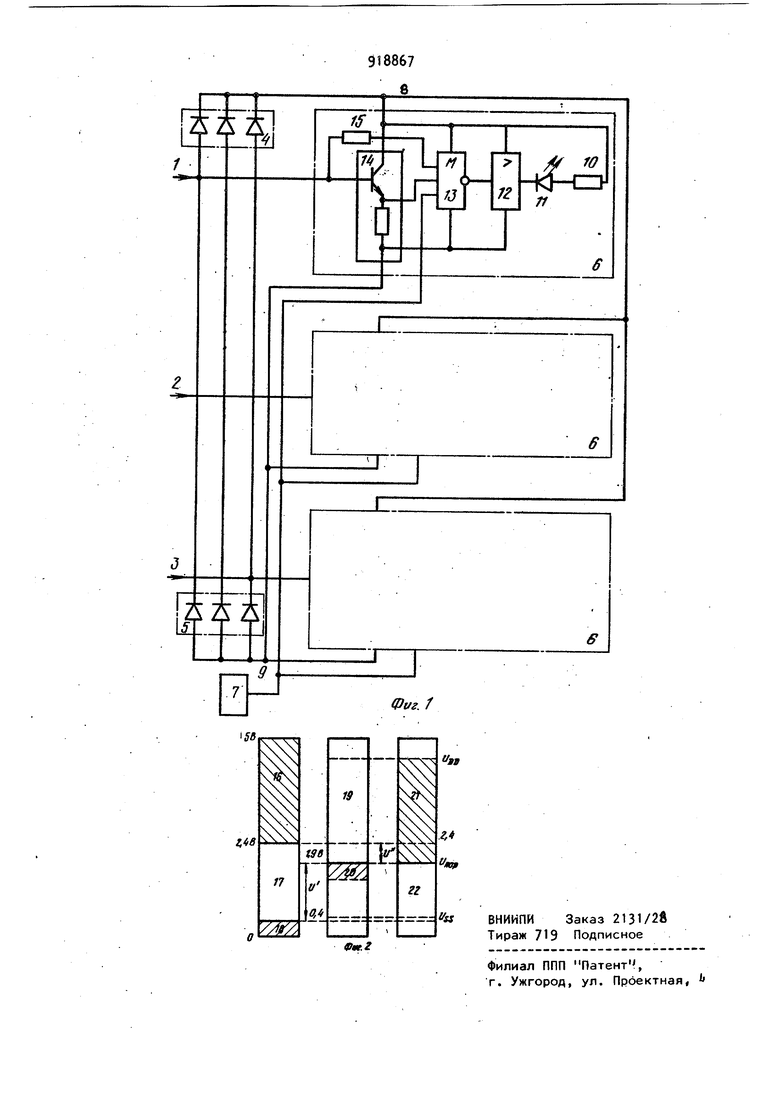

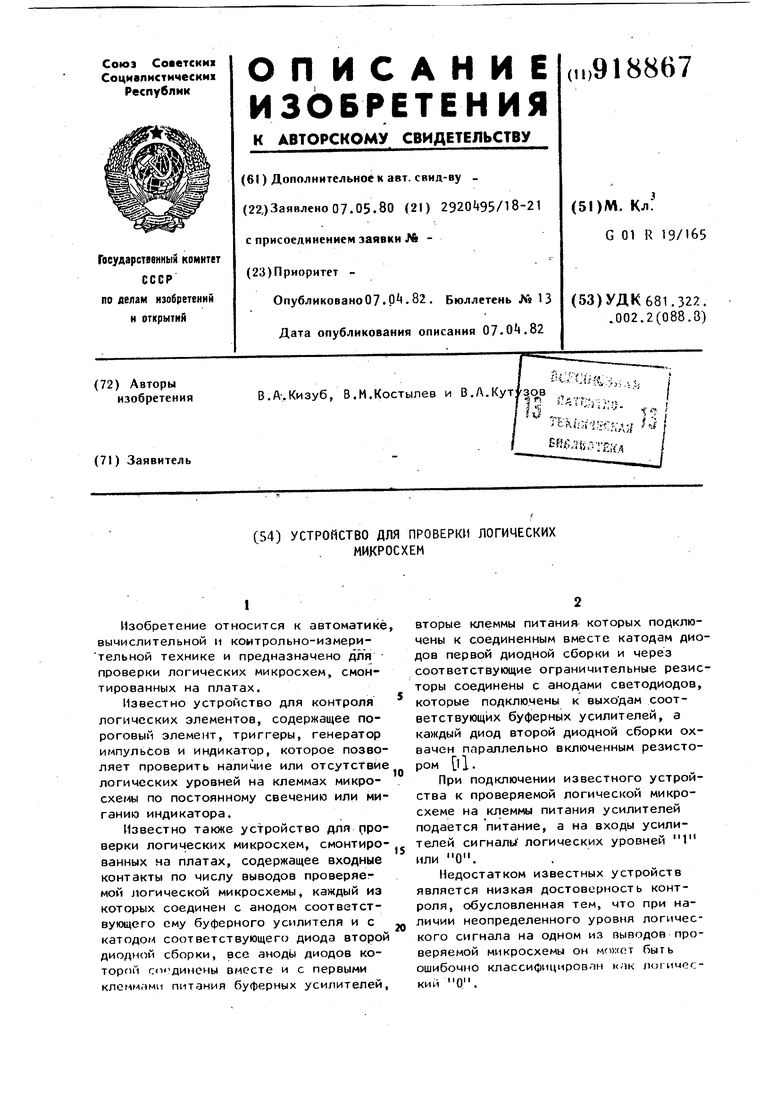

Изобретение относится к автоматике вычислительной и коитрольно-измерительной технике и предназначено для проверки логических микросхем, смонтированных на платах. Известно устройство для контроля логических элементов, содержащее пороговый элемент, триггеры, генератор импульсов и индикатор, которое позволяет проверить наличие или отсутствие логических уровней на клеммах микросхемы по постоянному свечению или миганию индикатора. Известно также устройство для рроверки логических микросхем, смонтированных на платах, содержащее входные контакты по числу выводов проверяет мой логической микросхемы, каждый из которых соединен с анодом соответствующего ему буферного усилителя и с катодом соответствующего диода второй диодн(й сборки, все аноды диодов которой г:11« динены вместе и с первыми клеммами питания буферных усилителей. вторые клеммы питания которых подключены к соединенным вместе катодам диодов первой диодной сборки и через соответствующие ограничительные резисторы соединены с анодами светодиодов, которые подключены к выходам соответствующих буферных усилителей, а каждый диод второй диодной сборки охвачен параллельно включенным резистором 01. При подключении известного устройства к проверяемой логической микросхеме на клеммы питания усилителей подается питание, а на входы усилителей сигналь логических уровней 1 или О. Недостатком известных устройств является низкая достоверность контроля, обусловленная тем, что при наличии неопределенного уровня логического сигнала на одном из выводов проверяемой микросхемы он может быть ошибочно классифицирован к;ж логический О. Цель изобретения - повышение достоверности и расширения функциональных воз.ю); ностей путем контроля вели чины неопределенного уровня логичеркого сигнала. . Поставленная цель достигается тем что в устройство для проверки логиче ких микросхем, содержащее входные за жимы по числу выводов микросхемы, каждый из которых соединен с измерительным входом соответствующей контрольной ячейкой, анодом соответствую щего диода первой диодной сборки,катоды которых -соединены между собой и образуют первую шину питания контрольныхячеек, и катодом соответству щего диода второй диодной сборки, аноды которых соединены между собой и образуют вторую шину питания контрольных ячеек, а каждя контрольная ячейка состоит из буферного усилителя, один вывод питания которого соед нен с первой шиной питания контрольных ячеек, которая через ограничител ный резистор и включенный в прямом направлении светодиод соединена с вы ходом буферного усилителя, другой вывод питания которого соединен с вт рой шиной питания контрольных ячеек, и дополнительные резисторы, введен генератор импульсов, а в каждую конт рольную ячейку введены эмиттерный повторитель и инвертирующий мажоритарный элемент, причем входы питания эмиттерного повторителя и инвертирую щего мажоритарного элемента подключены к шинам питания контрольных ячеек параллельно выводам буферного . усилителя, вход которого соединен с выходом инвертирующего ма ; оритарного элемента, первый вход которого через дополнительный резистор соединен с измерительным входом контрольной ячейки и с входом эмиттерного повторителя, выход которого соединен с вторым входом инвертирующего мажоритарного элемента, третий вход кото-рого через управляющий вход контроль ной ячейки соединен с генератором импульсов. На фиг. 1 представлена принципиальная схема устройства для проверки логических микросхем; на фиг. 2 потенциальные диаграммы логических сигналов на клеммах проверяемой логи ческой микросхемы. Устройство для контроля логических микросхем содержит входные контакты 1, 2 и 3 (входы) по числу выводов проверяемой микросхемы, первую k и вторую 5 диодные сборки, контрольные ячейки 6, генератор 7 импульсов, первую 8 и вторую 9 шины питания , контрольных ячеек, а каждая контрольная ячейка состоит из ограничительного резистора 10, светодиода 11, буферного усилителя 12, инвертирующего мажоритарного элемента 13, эмиттерного повторителя I и дополнительного резистора 15. На фиг. 2 показаны область 16 логических единиц на выводах микросхемы, область 17 неопределенного уровня на выводах микросхемы, область 18 логических нулей на выводах микросхемы. Область 19 напряжений на входе 1 мажоритарного элемента 13, соответствующая напряжению на входе устройства выше логического нуля, располагается выше элемента 1 3 и воспринимает. / ся им по входу 1 как высокий уровень. Область 20 напряжений на входе 1 мажоритарного элемента 13, соответствующая области логического нуля на входе устройства, располагается ниже элемента 13 и воспринимается им по входу 1 как низшийуровень. Область21 напря.жений на входе 2 мажоритарного элемента 13, соответствующая наличию на входе 2 yctpoйcтвa логической единицы, располагается выше Оцври воспринимается элементом 13 по входу 2 как высокий уровень. Область 22 напряжения на входе 2 мажоритарного элемента 13, соответствующая напряжению на входе устройства ниже логической единицы, располагается ниже и„орИ воспринимается мажоритарным элементом 13 по входу 2 как низкий уровень. и - падение напряжение на резисторе 15; падение напряжения на эмиттерном переходе эмиттера; потенциал Земля устройства (второй шини 9 питания) ; Цр, - потенциал первой шины 8 питания устрЪйства. Устройство работает следующим образом. 11осле подключения входов 1 - 3 к контактам микросхемы питающее напряжение на устройство подается через пару диодов диодных сборок t и 5. Падение напряжения на диодах, через которые осуществляется питание устройства, составляет около 0,5В, что вызывает смещение уровня потенциала второй шины 9 питания (Ujj) устройства по сравнению с уровнем потенциала Земля проверяемой микросхемы, так х(е, примерно на 0,5 В. Инвертирующие мажоритарные элементы 13 выполнены на базе ТТ логики, поэтому порог срабатывания по входам у этих элементов соответствует примерно 1, В, но с учетом падения напряжения на диоде второй диодной сборки 5 порог срабатывания Uпор по входам мажо ритарного элемента 13 по отношению к потенциалу Земля проверяемой микросхемы составляет около 1,9 В. Если на выводе проверяемой микросхемы присутствует высокий логический уровень UT/ 2,А В (область 16),.то он поступает через резистор 15 на пер вый вход мажоритарного элемента 13 и воспринимается им как высокий логический уровень (область 19). На второй вход мажоритарного элемента 13 логический сигнал поступает через эмиттерный повторитель , при этом на эмиттерном переходе его транзистора падает примерно 0,5 В (область 21). Таким образом, уровень напряжения на проверяемом выводе микросхемы равный или больше 2,+ В и соответствует порогу срабатывания мажоритарного элемента 13 по второму входу (область 21). Уровень напряжения на клеммах микросхемы ниже 2, В воспринимается на первом и втором входах мажоритарного элемента 13 как низкий логический уровень (область 20 и 22). При наличии на первом и втором входах мажоритарного элемента 13 вы1СОКИХ логических уровней (область 19 и 21) он срабатывает, на его выходе появляется низкий логический уровень и светодиод 11, подключенный к усили телю, зажигается. Если логический уровень на выводе проверяемой микросхемы ниже 2,4 В, то он воспринимается по второму входу мажоритарного элемента 13 с учетом падения напряжения на эмиттерном переходе транзистора эмиттерного повторителя 0,5 В как низкий логический уровень (область 22). Сопротивление резистора 15 соединяющего первый вход мажоритарного элемента 13 с вхо дом эмиттерного повторителя, выбирае ся из расчета, чтобы входной ток пер вого входа мажоритарного элемента 13 вызывал на резисторе 15 падение напря жения, примерно 1,5В, тогда уровень напря ; ения на выводе проверяемой мик росхемы, равный или больший 0,4 В, 91 7« соответствует hopory срабатывания мажоритарного элемента 13 по первому входу 1,9 В и воспринимается им как высокий уровень (область 19). Если уровень напряжения на выходе микросхемы ниже О, В, то уровень напряжения на первом входе мажоритарного элемента 13 будет меньше 1,9 В, и воспринимается им как низкий уровень, находящийся ниже порога срабатывания ПО первому входу мажоритарного элемента 13 (область 20). При наличии на первом и втором входах мажоритарного элемента 13 высоких логических уровней он срабатывает и на его выходе появляется низкий потенциал, который повторяется буферным усилителем и светодиод 11 зажигается постоянным свечением,При наличии на первом и втором входах мажоритарного элемента 13 низких логических уровней на выходе инвертирующего мажоритарного элемента сохраняется высокий потенциал и светодиод не зажигается. При высоком логическом уровне на первом входе и низком логическом уровне на втором входе- мажоритарного элемента 13 он срабатывает вследствие того, что на третий вход этого элемента периодически поступают импульсы от генератора импульсов (с частотой импульсов генератора). При этом светодиод, подключенный к выходу буферного усилителя, зажигается с такой же частотой. Мигание светодиода указывает на неопределенность потенциала на выводе микросхемы соответствующему светодиоду 11. Светодиод будет мигать и в случае обрыва вывода проверяемой микросхемы, а также в случае .отсутствия электрического контакта межДу выводами микросхемы и входными контактами устройства. Подключение входов устройства к выводам проверяемой микросхемы осуществляется через переходное устройство типа клипса. В режиме Самоконтроль клиПса отключается от проверяемой микросхемы, а к шинам 8 и 9 подается питание от внешнего источника напряжения, В исправном состоянии тестера все светодиоды зажигаются с частотой генератора. Устройство позволяет определять как наличие и отсутствие неопределенных уровней на контактах проверяемой микросхемы, так и наличие неопределенных уровней и обрывов контактов. формул-э изобретения Устройство для проверки логических микросхем, содержащее входные зажимы по числу выводов микросхемы,каждый из которых соединен с измерительным входом соответствующей контрольной ячейки, анодом соответствующего диода первой диодной сборки, катоды которых соединены между собой и образуют первую шину питания контрольных ячеек, и катодом соответствующего диода второй диодной сборки, аноды которых соединены между собой и образуют вторую шину питания контрольных ячеек, а каждая контрольная ячейка состоит из буферного усилителя, один вывод питания, которого соединен с пер вой шиной питания контрольных ячеек, которая через ограничительный резис- 20

тор и включенный в прямом направлении светодиод соединена с выходом буферного усилителя, другой вывод питания которого соединен с второй шиной питания контрольных ячеек и дополнитель-25 ные резисторы, отличающее9

управляющии вход контрольной ячейки соединен с генератором импульсов.

Источники информации, принятые во внимание при экспертизе 1. Электроника, , вып. 11, с. , рис. 2. 7О с я тем, что, с целью повышения достоверности и расширения функциональных возможностей устройства, s него введен генератор импульсов, а в каждую контрольную ячейку введены эмиттер,ный повторитель и инвертирующий мажоритарный элемент, причем входы питания эмиттерного повторителя и инвертирующего мажоритарного элемента подключены к шинам питания контрольных ячеек параллельно выводам буферного усилителя, вход которого соединен с выходом инвертирующего мажоритарного эле((ента, первый вход которого через дополнительный резистор соединен с мажоритарным входом контрольной ячейки и с входом эмиттерного повторителя, выход которого соединен с вторым входом инвертирующего мажоритарного элемента, третий вход которого через

918867 в

Авторы

Даты

1982-04-07—Публикация

1980-05-07—Подача