мультиплексоры 2,8, счетчик 9, компаратор 10, генератор 1, для достижения цели введены формирователи импульсов 3,4, инвертор 6, счетчик 12, элементы 2ИЛИ-НР 15,16, источник 3 опорных напряжений, источник 21 напряжения смещения, резисторы 13-1. ..., 13-п, светодиоды 14-1,,..,l4-n, блок 11 памяти. Введен блок 7 определения состояния входа (ОСВ)ко1

Изобретение относится к контрольно-измерительной технике и Предназначено для проверки логических микросхем.

Цель изобретения - повьшение дос- товерносгк проверки микросхем за счет сохранения точности контроля при увелотении количества выводов контролщ уемой микросхемы.

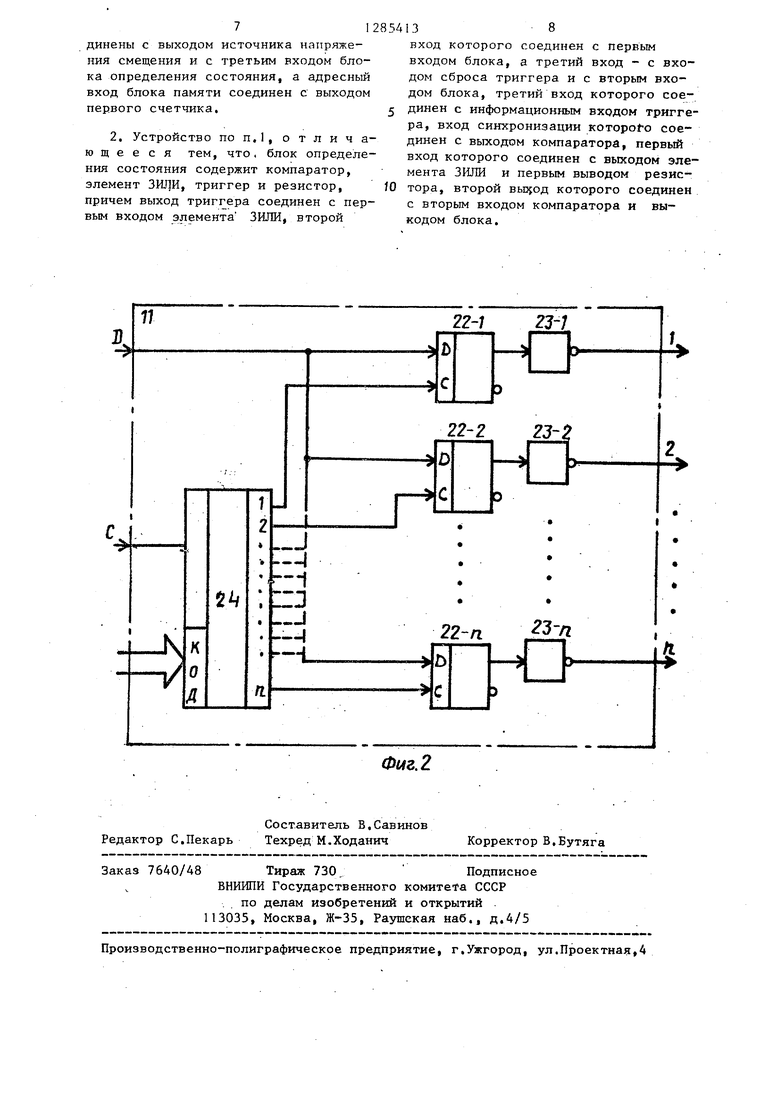

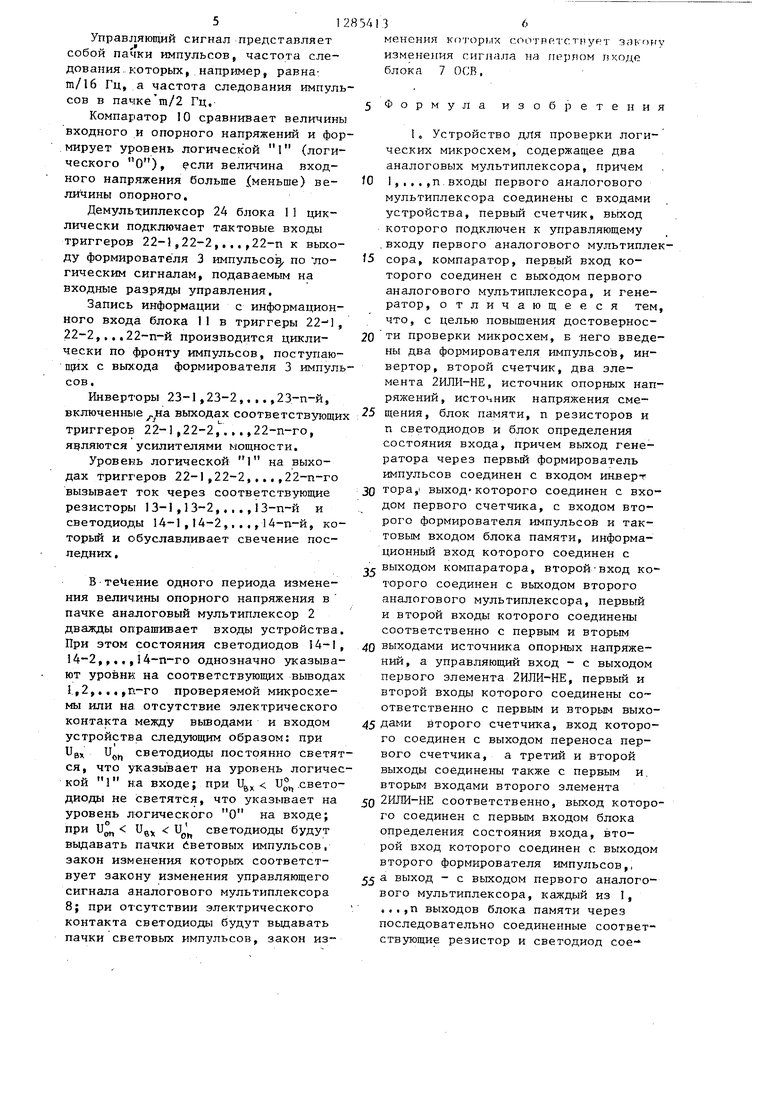

На фиг, приведена функциональная схема предлагаемого устройства; на фиг,2 - функциональная схема блока памяти.

Устройство содержит генератор 1, первь1й аналоговый мультиплексор 2, первый 3 и второй 4 формирователи импульсов, источник 5 опорных напряжений, инвертор 6, блок 7 определения состояния входа (блок ОСВ), второй аналоговый мультиплексор 8, первый счетчик 9, компаратор 10, блок |{ памяти, второй счетчик 12, резисторы 13-1, 13-2,.,,, 13-п, светодиоды 14-1, 14-2,,,,14-п, перг вый 15 и второй J6 элементы 2ИЛИ-НЕ элемент ЗИЛИ 17, резистор 18, компаратор. 18, триггер 20, источник 21 напряжения смещения.

Блок IJ памяти содержит триггеры 22-1, 22-2,,,,,22-п, инверторы 23-1, 23-2,,,,,23-п, демультиплексор 24,

Выход генератора 1 соединен с входом первого формирователя 3 импульсов, выход которого соединен с тактовым входом блока 1I памяти, через второй формирователь 4 импульсов - вторым вxoдo f блока 7 ОСВ и через инвертор 6 - с входом первого счетчика 9, выход первого счетчика 9 соединен с BxolnoM управления первого анаторый содержит элемент 3HJM 17, ре- зис,тор 18, компаратор 19, триггер 20. Блок ОСЕ 7 производит оценку состояния подключенного входа и вьщает на неинвертирующий вход компаратора 10 сигнал, значение которого зависит от произведенной сценки и от уровней сигналов, поступивщих на входы блока 1 з.п, ф-лы, 2 ил.

логового мультиплексора 2 и адресным входом блока 11 памяти, выход переноса первого счетчика 9 соединен с входом второго счетчика Г2,

первый выход которого соединен с первым входом первого элемента 2ИЛИ-НЕ 15, второй выход с первым входом второго элемента 2ИЛИ-НЕ 16, а третий - с вторыми входами первого и второго . элементов 2ИЛИ-НЕ 15 и 16, Выходы первого 15 и второго 16 элементов 2ИЛИ-НЕ соединены соответственно с управляющим входом второго аналогового мультиплексора Вис первым входом блока 7, выход первого аналогового мультиплексора 2 соединен с первым входом компаратора 10 и с выходом блока 7, первый, второй,,,,, п-й входы первого аналйгового муль- типлексора 2 соединены с первым, вторым,,.,, п-м входами устройства, второй вход компаратора 10 соединен с выходом второго аналогового мультиплексора 8, первый и второй входы которого соединены соответственно с первым и вторым выходом источника 5 опорных напряжений, выход компаратора J О соединен с информационным входом блока 11 памяти, выходы которого подключены через последовательно соединенные резисторы 13-1, 13-2,,.,, 13-п-й и светодиоды 14-1,14т2,,,,, 14-п-й с выходом источника 2I.напряжения смещения. Первый и второй входы блока 7 являются соответственно вторым и третьим входами элемента ЗШШ J7, третий вход которого соединен с входом сброса триггера 20, выход элемента ЗИЛИ 17 соединен с пер

вым входом компаратора I9 и через

312

резистор 18 с его вторым входом и с выходом блока 7, выход компаратора J9 соединен с входом синхронизации триггера 20, третий вход которого ;оединен с выходом источника 2I, а выход - с первым входом элемента ЗИЛЙ 17.

Информационный вход блока 11 памяти (фиг,2) соединен с информационными входами триггеров 22-1,22-2,..., 22-п, выходы котор 1х соединены с 1аходами соответствующих инверторов 23-1,22-2,...,23-п, тактовый вход и адресный вход блока 11 памяти являются сбответственно информационным входом и входными разрядами управления демулЬтиплексора 24, первый, второй,..., п-й вьпсоды которо

В данном случае в блоке 7 ОСВ

го соединены с соответствующими

входами синхронизации триггеров 22-1,20 протекают процессы, аналогичные опи22-2,...,22-п, выхода инверторов 23-1, 23-2,...,23-п являются соответственно первым, вторым,...п-м

санным в п.1 за исключением того, что падение напряжения, возникающее на резисторое 18 за счет входного тока компаратора 10 и тока коллекто- 25 ра, достаточно для переключения компаратора 19.

выходами блока 11.

Устройство работает следующим образом.

Аналоговый мультиплексор 2 подключает циклически с частотой mxn Гц первый, второй,... п-й входы устсанным в п.1 за исключением того, падение напряжения, возникающее н резисторое 18 за счет входн тока компаратора 10 и тока коллек 25 ра, достаточно для переключения к паратора 19.

На выходе компаратора 19 форми руется короткий отрицательный имп по фронту которого триггер 20 уст

ройства к инвертирующему входу компа- 30 навливается в состояние логичесг. ратора 10, где га - коэффициент деле- °

НИН счетчика 12.

Блок 7 ОСВ производит оценку состояния гТодключеннрго входа и выдает на неинвертируилций вход компаратора 10 сигнал, значение которого зависит от произведенной оценки и от уровней сигналов, поступивщих на 9ХОДЫ блока.

Возможны следующие состояния входа устройства и процессы, протекающие в блоке 7 ОСВ:

I. Отсутствует электрический контакт между входом устройства и выводом проверяемой схемы,

При подключении очередного -входа триггер 20 устанавливается в состояние логического 0 (стирается информация о состоянии предыдущего входа) положительным импульсом, поступающим на его вход сброса. По этому же импульсу и при наличии сигнала логического О на втором входе выход элемента ЗИЛИ 17 подключает резистор 18 к плюсу источника 21 напряжения питания,:

Падение напряжения, возникающее на резисторе 18 за счет входного

5

134

тока компаратора 10, недостаточно. для переключения компаратора 19, поэтому на его выходе логический уровень не изменится. Состояние триггера 20 также не изменится, на , его выходе останется логический О который не влияет на работу .элемента ЗИЛИ 17.

При наличии сигнала логической 1 на втором входе элемента.ЗИЛИ 17 его выход подключает резистор 18 к плюсу источника 21 на время действия логическо.й 1.

I 2. Вход устройства имеет электрический контакт с выводом проверяемой микросхемы, который соединен с открытым коллектором.

В данном случае в блоке 7 ОСВ

протекают процессы, аналогичные описанным в п.1 за исключением того, что падение напряжения, возникающее на резисторое 18 за счет входного тока компаратора 10 и тока коллекто- ра, достаточно для переключения компаратора 19.

На выходе компаратора 19 формируется короткий отрицательный импульс/ по фронту которого триггер 20 уста-

По уровню логической 1 йа перво входе элемента ЗИЛИ 17 его выход под 35 ключает резистор 18 к плюсу источника 21 до момента подключения следующего входа устройства.

3., Вход устройства имеет электрический контакт с выводом проверяе- 40 мой микросхемы, который не соединен с открытым коллектором и на котором имеется проверяемый уровень напряжения.

В данном случае высокоомный вы- 45 ход блока 7 ОСВ шунтируется низким выходным сопротивлением проверяемой микросхемы и не оказывает влияния на работу остальной части устройства

Аналоговый мультиплексор 8 под- 50 ключает инвертирующий вход компаратора 10 к первому или второму выходу источника опорных напряжений по управляющему сигналу логической 1 или логического О. Источник 5 опор- 55 ных напряжений выдает на первом и втором выходах напряжения uj, и Uj , соответствующие нижнему и верхнему iдопустимым зфовням логической I V логического О.

Управляющий сигнал представляет собой пачки импульсов, частота следования которых, например, равна- т/16 Гц, а частота следования импульсов в пачке т/2 Гц.

KoMnapiaTop 10 сравнивает величины входного и опорного напряжений и формирует уровень логической 1 (логического О), сли величина входного напряжения больше .(меньше) величины опорного.

Демультиплексор 24 блока I1 циклически подключает тактовые входы триггеров 22-1,22-2,...,22-п к выходу формирователя 3 импульсо по логическим сигналам, подаваемым на входные разряды управления.

Запись информации с информационного входа блока 1 1 в триггеры 22- 1 , 22-2,.., производится циклически по фронту импульсов, поступающих с выхода формирователя 3 импульсов.

Инверторы 23-1,23-2,...,23-п-й, включенные на выходах соответствующих триггеров 22-1,22-2, ..,22-п-го, являются усилителями мощности.

Уровень логической 1 на выходах триггеров 22-1,22-2,...,22-п-го вызывает ток через соответствующие резисторы 13-1,13-2,.,.,3-п-й и светодиоды 14-1,IA-2,...,14-п-й, который и обуславливает свечение последних .

В те 1ение одного периода изменения величины опорного напряжения в пачке аналоговый мультиплексор 2 дважды опрашивает входы устройства. При этом состояния светодиодов 14-1, 14-2,,..,I4-п-го однозначно указывают уровни на соответствующих выводах ,2,...,п-го проверяемой микросхемы или на отсутствие электрического контакта между вьшодами и входом устройства следующим образом; при Ugx , светодиоды постоянно светятся, что указывает на уровень логической 1 на входе; при Ug °

U°j .светодиоды не светятся, что указывает на уровень логического О на входе;

при и„„

URV и вХ Oh

светодиоды будут

вьщавать пачки Световых импульсов, закон изменения которых соответствует закону изменения управляющего сигнала аналогового мультиплексора 8; при отсутствии электрического контакта светодиоды будут выдавать пачки световых импульсов, закон изменения которых соотпр гствурт закону изменения сигнала на перлом л коде блока 7 ОСВ,

Формула изобретения

I, Устройство для проверки логических микросхем, содержащее два аналоговых мультиплексора, причем

1,,..,п входы первого аналогового мультиплексора соединены с входами устройства, первый счетчик, вьЬсод которого подключен к управляющему входу первого аналогового мультиплексора, компаратор, первый вход которого соединен с выходом первого аналогового мультиплексора, и генератор, отличающееся тем, что, с целью повышения достоверности проверки микросхем, в него введены два формирователя импульсов, инвертор, второй счетчик, два элемента 2ИЛИ-НЕ, источник опорных напряжений, источник напряжения смещения, блок памяти, п резисторов и п светодиодов и блок определения состояния входа, причем выход генератора через первый формирователь импульсов соединен с входом инверт

TOpa,i выход-которого соединен с входом первого счетчика, с входом второго формирователя импульсов и тактовым входом блока памяти, информационный вход которого соединен с выходом компаратора, второй вход которого соединен с выходом второго аналогового мультиплексора, первый и второй входы которого соединены соответственно с первым и вторым

выходами источника опорных напряжений, а управляющий вход - с выходом первого элемента 2ИЛИ-НЕ, первый и второй входы которого соединены соответственно с первым и вторым выхо- дами второго счетчика, вход которого соединен с выходом переноса первого счетчика, а третий и второй выходы соединены также с первым и, вторым входами второго элемента

2ИЛИ-НЕ соответственно, выход которого соединен с первым входом блока определения состояния входа, второй вход которого соединен с выходом второго формирователя импульсов,, а выход - с выходом первого аналогового мультиплексора, каждый из I, .,,,п выходов блока памяти через последовательно соединенные соответствующие резистор и светодиод соединены с выходом источника напряжения смещения и с третьим входом блока определения состояния, а адресный вход блока памяти соединен с выходам первого счетчика,

2, Устройство по п,1, отличающее с я тем, что. блок определения состояния содержит компаратор, элемент ЗИЛИ, триггер и резистор, причем выход триггера соединен с первым входом элемента ЗИЛИ, второй

Составитель В.Савинов Редактор С.Пекарь Техред М.Ходанич

Заказ 7640/48 Тираж 730, Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

854138

вход которого соединен с первым входом блока, а третий вход - с входом сброса триггера и с вторым входом блока, третий вход которого сое- 5 динен с информационным входом триггера, вход синхронизации KOTOpofo соединен с выходом компаратора, первый вход которого соединен с выходом элемента ЗИЛИ и первым выводом резис- fO тора, второй вьщод которого соединен с вторым входом компаратора и вы- кодом блока.

Фиг. 2

Корректор В.Бутяга

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для разбраковки полупроводниковых диодов | 1983 |

|

SU1164636A1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ГИБРИДНЫХ ЭЛЕКТРОННЫХ УСТРОЙСТВ | 2012 |

|

RU2493609C1 |

| Многоканальное устройство для проверки логических микросхем | 1985 |

|

SU1242864A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Устройство для автоматизированного контроля параметров реле | 1985 |

|

SU1265704A1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

| Электронные часы со звуковой сигнализацией | 1986 |

|

SU1377817A1 |

| Устройство для измерения индикатрис рассеяния света | 1990 |

|

SU1723456A1 |

| Устройство для формирования пачек импульсов | 1991 |

|

SU1812617A1 |

| Устройство регулировки осветительно-проекционных систем | 1987 |

|

SU1580307A1 |

Изобретение-относится к контрольно-измерительной технике. Целью изобретения является повышение достоверности проверки микросхем за счет сохранения точности контроля при увеличении количества выводов контролируемой микросхемы. В устройство, содержащее аналоговые

| Многоканальное устройство контроля напряжения | 1980 |

|

SU924595A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Многоканальное устройство для контроля логических сигналов цифровых схем | 1980 |

|

SU868606A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-01-23—Публикация

1985-04-17—Подача