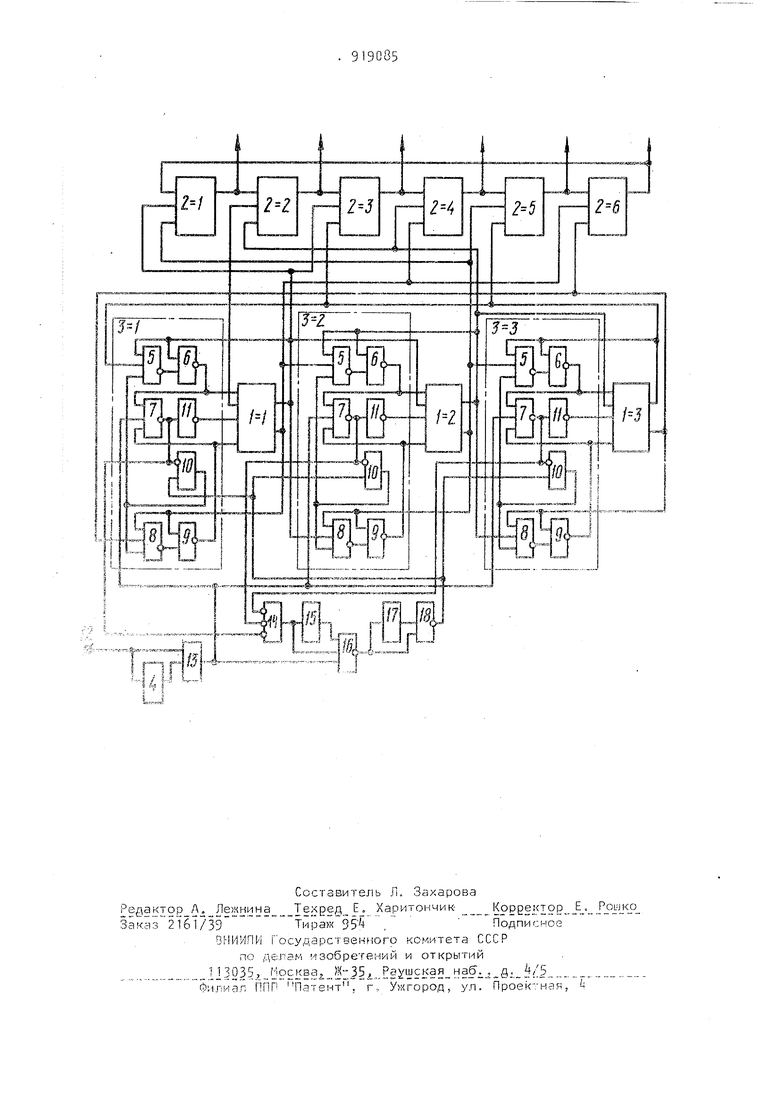

Изобретение относится к автоматике и телемеханике и может быть использовано при коммутации электричес ких Сигналов. По основному авт.св. № 733105 известен распределитель импульсов, сод жащий п триггеров, 2п элементов И, элемент задержки и п блоков управления, состоящих из .элементов И-НЕ за прета и инвертора 1. Недостаток устройства заключается в возможности возникновения сбоев пр воздействии на его информационный вход перекрестных помех от соседних линий связи. Эти перекрестные помехи носят характер импульсных помех с дл тельностью и амплитудой, достаточной для срабатывания логических микросхем. Цель изобретения - повышение помехоустойчивости . Указанная цель достигается тем, что в распределитель импульсов, содержащий п триггеров и 2п элемен- . тов и, соединенных по кольцевой схеме, элемент задержки, соединенный с входной шиной, и п блоков управления, каждый из которых состоит из элементов И, инвертора и элемента запрета, прямой выход каждого К-того триггера соединен с первым входом К-того и вторым входом (К+1)-ого блока управления, а инверсный выход - с третьим входом К-того и четвертым входом (К+1)-ого блоков управления, первый, второй и третий выходы. каждого блока управления подключены соответственно к единичному входу, входу синхронизации и нулевому входу К-того триггера, введены элемент И, элемент запрета, формирователь импульсов,дополнительный элемент задержки, элемент ИЛИ-НЕ и элемент И-НЕ, причем первый вход элемента И соединен с входной шиной, второй - с выходом элемента задержки, а выход - с пятыми входами каждого блока управления и первым входом элемента ИЛИ-НЕ, при этом второй его вход подключен к выходу элемента запрета и через формирователь импульсов к третьму входу элемента 11ЛИ-НЕ, выход которого соединен с первым входом элемента И-НЕ и через дополнительный элемент задержки с вторым его входом, причем выход элемента И-НЕ подключен к шестым входам каждого блока управления, кроме того, входы элемента запрета соединены с инверсными входами элемента запрета соответствующего блока управления. На чертеже представлена функциональная схема предлагаемого устройства. Устройство содержит потенциальные триггеры , элементы , соединенные по одному из ВХОДОЕЗ по кольцевой схеме, блоки управ ления и элемент 4 задержки. Каждый из блоков управления состоит из элементов И-НЕ , элемента 10 запрета и инвертора 11. Входная шина (вход) 12 соединена с входами элементов задержки и И 13. Дополнительно в распределитель им пульсов введены элемент И 13, элемент 1 запрета, формирователь 15 им пульсов, элемент ИЛИ-НЕ 16, элемент 17 задержки и элемент И-НЕ 18. Устройство работает следующим образом. В начале работы, до подачи входны импульсов на вход 12, подается установочный импульс, при котором ice триггеры 1 устанавливаются в исходно состояние. При этом на прямых выходах триггеров 1 устанавливается низкий уровень напряжения, а на инверсньо; - вы сокий. На всех выходах элементов И 2 кроме последнего, имеется высокий уровень напряжения, а на последнем низкий. На всех информационных входах триггеров 1, кроме первого, имеется низкий уровень напряжения, а на информационном входе первого триггера 1 - высокий, В начальный момент времени на единичных входах всех триггеров 1 имеется высокий уровень напряжения. До подачи первого входного сигнал и в паузах между входнь1ми сигналами на вход 12 могут воздействовать пере крестные помехи, представляющие собо импульсы положительной полярности ма лой длительности. При этом импульс помехи (при наличии помехи.) поступае на первый вход элемента И 13 и на зход элемента задержки. Время задержкичГ,ддВыбирается таким образом, чтобы импульс помехи на первом входе элемента И 13 заканчивался раньше,, чем на втором его входе появится этот же импульс, задержанный элементом Ц задержки. При этом на выходе элемента И 13 сигнал не изменяется, т.е. импульс помехи не воздействует на состояние триггеров 1. При разрыве входного сигнала импульсом перекрестной помехи (на входе 12 появляется низкий уровень напряжения малой длительности ) на выходе элемента И 13 появляются два коротких импульса низкого уровня напряжения, сдвинутые один относительно другого на время1,дд. Эти импульсы инвертируются элементом ИЛИ-НЕ 16 и поступают на первый вход : элемента И-НЕ 18 и на элемент 17 за-, держки, где задерживаются на время этом на втором входе элемента И-НЕ 18 задержанные импульсы появляются по окончании импульсов на первом входе элемента И-НЕ 18, а результате чего совпадения импульсов не происходит, и выходной сигнал элемента И-НЕ 18 (высокий уровень напряжения) не изменяется, т.е. разрыв сигнала импульсом помехи не влияет на состояние триггеров 1. Блок управления подготавливается к работе по установочному импульсу и окончанию шестого и третьего импульсов, а работает по началу первого и четвертого импульсов за цикл работы. При поступлении на вход 12 импульсной последовательности входных сигналов низкий уровень входного напряжения проходит через элемент И 13 и вызывает появление высокого уровня напряжения на выходе элемента ИЛИ-НЕ 1б. Этот высокий уровень напряжения проходит через элемент 17 задержки и появляется на первом и втором входах элемента И-НЕ 18, что вызывает его срабатывание. При этом на входе элемента 10 запрета блока управления появляется низкий уровень напряжения, а на выходе этого элемента - высокий уровень напряжения, который переводит элементы И-НЕ 8 и 9 данного блока управления в такое состояние, при котором на вход установки в ноль тригr-gpa 1 1 подается зьюокий уровень напряжения. Одновременно подается разрешение на вход элемента И-НЕ 7D таком состоянии только триггер 1-1 подготовлен к воздействию входных импульсов, так как на его установочных и информационном входах имеется высокий уровень напряжения, а на прямом выходе - низкий уровень напряжения. С поступлением первого входного импульса высокий уровень входного на пряжения поступает на первый и через элемент k задержки на второй вход элемента И 13, что вызывает появлени высокого уровня напряжения на выходе элемента И 13. При этом срабатывают элемент И-НЕ 7 инвертор 11 и три:- гер , который переходит во нторое устойчивое состояние, а на выходе элемента И-НЕ 6 появляется низкий уровень напряжения, который удерживает триггер в установившемся состоянии (в единичном cocтoянии. Одновременно српбатыпает элемент И , и на его выходе появляется вы сокий уровень напряжения, при этом с элемента И снимается запрет,и на его выходе появляется низкий уровень напряжения с задержкой относительно высокого уровня напряжения на выходе элемента И . Величина времени задержки определяется временем срабатывания выбранного типа микросхем и лежит в пределах от нескольких наносекунд до одной микросекунды, что вполне достаточно для вре- . менной коммутации сигналов. По окончании действия первого импульса на входе 12 происходит подготовка второго блока управления к работе. С приходом второго входного импульса переключается триггер , который затем блокируется выходным сигналом элемента И-НЕ 6 блока управления. Блок управ ления работает аналогично блоку управления. При переключении триггера срабатывают элементы И , и , на выходах которых соответственно появляются высокие и низкие уровни напряжения и т.д. Элемент 1 запрета и формирователь 15 импульсов предназначены для 9 56 формирования стробирующего импульса длительностью 2. Этот импульс положительной полярности образуется в момент переключения триггеров 1 и предназначен для устранения двойного переключения за один такт входного сигнала при наличии разрывов входного сигнала, опережающих задний фронт входного импульса на время t 4 iaAТаким образом, в предлагаемом распределителе импульсов исключатся сбои триггеров при появлении разрывов во входных сигналах и повышается помехоустойчивость при воздействии импульсов помех на вход устройства в паузах между сигналами. Формула изобретения Распределитель импульсов по авт. авт, св. fi 733105, отличающийся тем, что, с целью повышения помехоустойчивости, в него введены элемент И, элемент запрета, формирователь импульсов, дополнительный элемент задержки, элемент ИЛИ-НЕ и элемент И-НЕ, причем первый вход элемента И соединен с входной шиной, второй - с выходом элемента задержки, а выход - с пятыми входами каждого блока управления и первым входом элемента ИЛИ-НЕ, при этом второй его вход подключен к выходу элемента за- . прета и через формирователь импульсов к третьему входу элемента ИЛИ-НЕ, выход которого соединен с первым входом элемента И-НЕ и через дополнительный элемент задержк11 с вторым его входом, причем выход элемента И-Н.Е под-j ключен к шестым входам какдого блока управления, кроме того, входы элемента запрета соединены с инверсными входами элемента запрета соответствующего блока управления. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 733105, . Н 03 К 17/62, 12.10.77.

| название | год | авторы | номер документа |

|---|---|---|---|

| Распределитель импульсов | 1980 |

|

SU869041A2 |

| Распределитель импульсов | 1977 |

|

SU733105A1 |

| Устройство для управления очередностью обслуживания | 1987 |

|

SU1481765A2 |

| Распределитель импульсов | 1979 |

|

SU864563A1 |

| Устройство выделения тактовой частоты | 1980 |

|

SU932640A1 |

| Логическое переключающее устройство для раздельного управления группами тиристорного циклоконвертора | 1980 |

|

SU1010715A1 |

| ИЗБИРАТЕЛЬНОЕ УСТРОЙСТВО ИДЕНТИФИКАЦИИ ВЫЗОВА ОТ АБОНЕНТА | 1998 |

|

RU2136050C1 |

| Устройство для контроля распределителя | 1982 |

|

SU1057960A1 |

| Многоканальная время-импульсная телеизмерительная система | 1984 |

|

SU1288738A1 |

| Устройство для преобразования импульсного сигнала по длительности | 1989 |

|

SU1732446A1 |

Авторы

Даты

1982-04-07—Публикация

1980-06-12—Подача