I

Изобретение относится к автоматике и вычислительной технике и предназначено для определения в-реальном масштабе времени максимального

(минимального ) числа из множества -разрядных двоичных чисел, а также группы чисел относительно максимального {минимального) числа из этого же множества, например в системе управления базами ланынх и в устройствах децентрализованного управления сетями связи.

Известно устройство для сравнения т п -разрядных двоичных чисел, содержащее m счетчиков с обратным счетным входом, в которые записывают сравниваемые числа, а сравнение осуществляют подачей импульсов от генератора на обратные счетные входы

Недостатком устройства является большое время сравнения, обусловленное последовательным принципом действия этих устройств.

Наиболее близким к предлагаемому является устройство для сравнения ГПп -разрядных двоичных чисел,содержащее п схем ИЛИ, соединенных с п-блоками сравнения, пл п блоков последовательного опроса и блок индикации, причем первые входы блоков последовательного опроса старших П-ых разрядов объединены шиной единичного уровня первые входы других разрядов блоков последовательного опроса соединены с первыми выходами соответствующих блоков последовательного опроса, вторые и третьи входы которых подключены к выходам блоков сравнения, выходы блоков последовательного опроса соединены с блоками сравнения, а блок индикации подключен к выходам m схем ИЛИ и к выходам блоков последовательного опроса младших разрядов 2 .

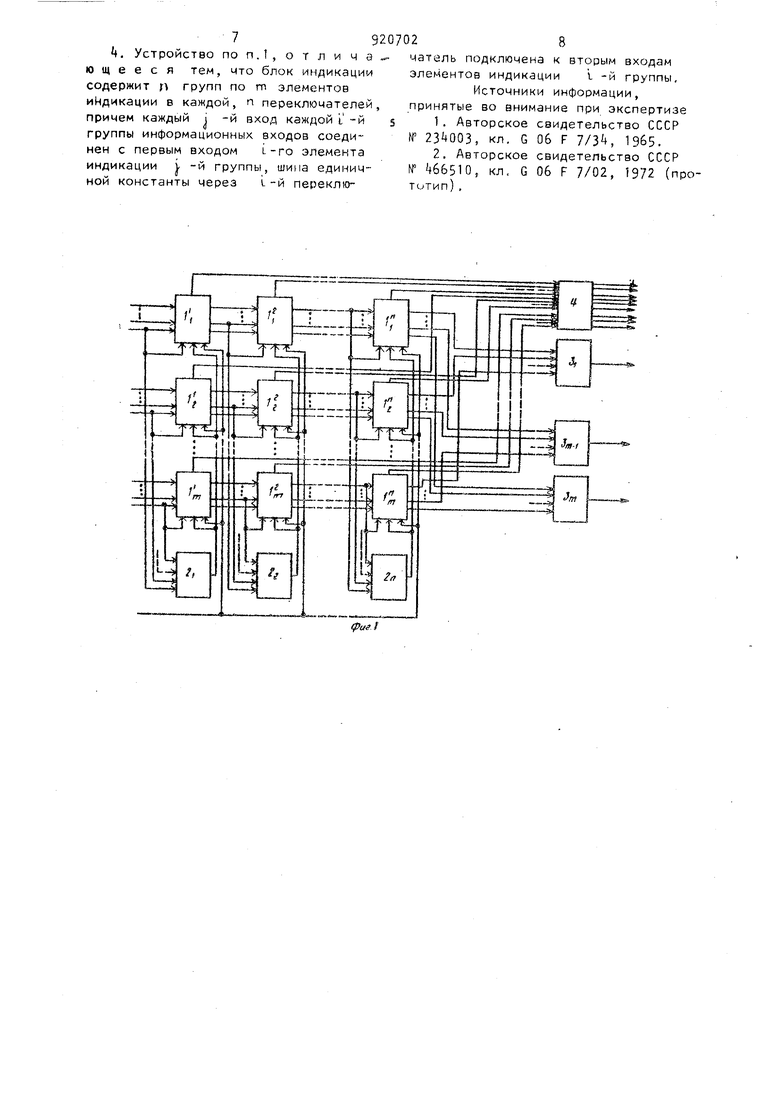

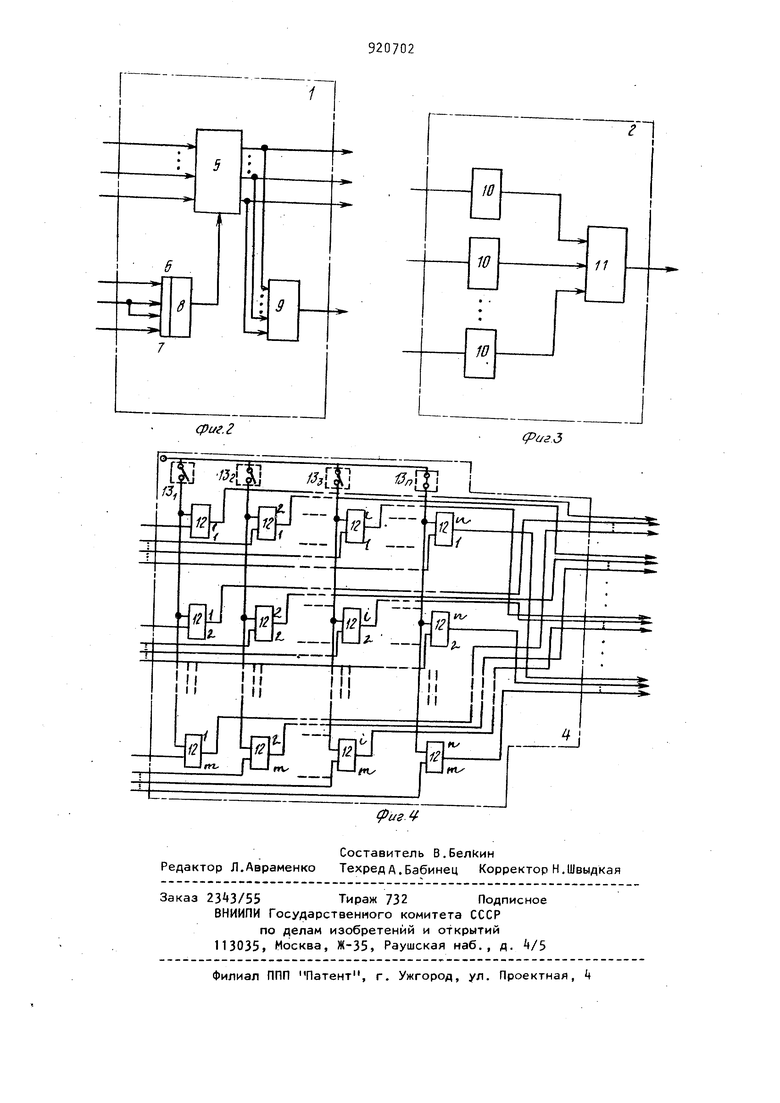

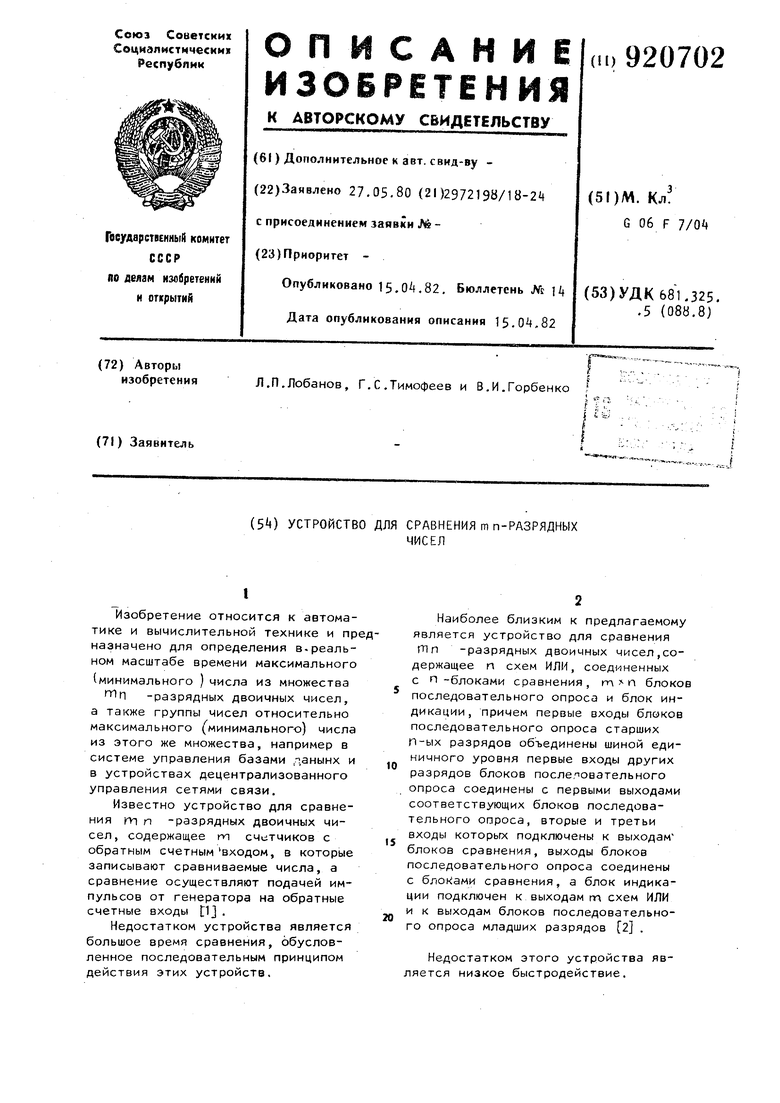

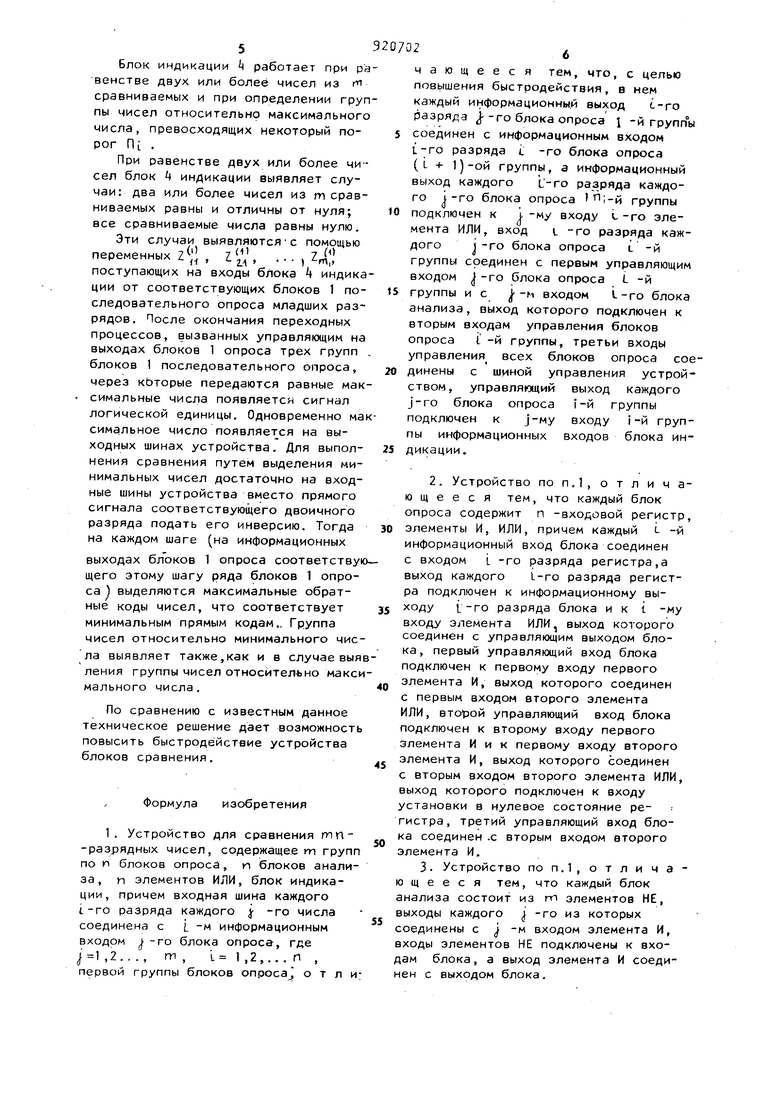

Недостатком этого устройства является низкое быстродействие. Цель изобретения - повышение быстродействия устройства. Цель достигается тем, что в устройтсве для сравнения разрядных чисел, содержащем т групп по блоков опроса, п блоков анализа , п элементов ИЛИ, блок индикации ,-причем входная шина каждого L -го разряда ка чдого I. -го числа соединена с 1 -м информационным входом -го блока опроса, где } 1 ,2 4- . m , i- 1 ,2. . . n , первой группы блоков опроса, каждый информационный выход L-го разряда j Го блока опроса L -и группы соединен с информационным входом i -го блока опроса (L +1)-й группы, а информационный выход каждого i- -го разряда каждого j-ro блока опроса п-ой группы подключен к j -му входу L-го элемента ИЛИ, вход 1-га каждого . блока опроса L-ой группы соединен с первым управляющим вхо дом |-го блока опроса I -и группы и с |-м входом I -го блока анализа, выход которого подключен ко вторым входам управления блоков опро са L -Г; группы, третьи входы упра ления всех блоков опроса соединены шиной управления устройством, управ ляющий выход каждого -го блока опроса I -и группы подключен к у -м входу L -ой группы информационых входов блока индикации. Каждый блок опроса содержит п-вх довой регистр, элементыИ, ИЛИ, при чем каждый L -ый информационный вход блока соединен с входом 1 -го разряда регистра, а выход каждого L -го разряда регистра подключен к информационному выходу i -го разряда блока и к t -му входу элемента ; ИЛИ, выход которого соединен с упра ляющим выходом блока, первый управл ющий вход блока подключен к первом входу первого элемента И, выход ко торого соединен с первым входом второ го элемента ИЛИ, второй управляющий вход блока подключен к второму входу первого элемента И и к первому входу второго элемента И, выход которого соединен с вторым входом вто рого элемента ИЛИ, выход которого подключен ко входу установки в нуле вое состояние регистра, третий упра ляющий вход блока соединен со вторы входом второго элемента И. 9 4 Каждый блок анализа состоит з гп элементов НЕ, выходы каждого t-ro из которых соединены с J--M входом элемента И, входы элементов НЕ подключены к входам блока, а выход элемента И соединен с выходом блока-. Блок индикэции содержит п групп по гп элементов индикации в каждой, П переключателей, причем каждый 1 -и вход каждой 1 -и группы информационных входов соединен с первым входом 1 -го элемента индикации | -и группы, шина -единичной константы через L -и переключатель подключена к вторым входам элементов индикации L-Й группы. На фиг,1 представлена структурная схема устройства для сравнения, mn -разрядных двоичных чисел;на фиг .2 структурная схема блока последовательного опроса; на фиг.З структурная схема блока сравнения; на фиг, блок-схема блока индикации. Устройство содержит m групп по п блоков 1 опроса, h блоков 2 анализа, п элементов ИЛИ 3 и блок индикации k, Каждый из блоков 1 опроса состоит из регистра 5, элементов И 6 и 7, элементов ИЛИ 8 и 9, а каждый блок анализа 2 имеет «пп элементов НЕ 10 и элемент И 11. Блок индикации 4 содержит элементы индикации 12 ., .12 переключатели 13 , Ui...l3n. Устройство работает следующим образом, Перед началом регистры 5 всех блоков 1 последоЕзательного опроса устанавливаются в нулевое состояние, а в блоке 4 индикации задается некоторый порог для определения группы чисел относительно максимального числа. Через входные шины устройства на информационные входы блоков 1 опроса старших h-ых разрядов поступают двоичные числа , подлежащие сравнению, а через шину управления устройства управляющий сигнал попадает на управляющие входы всех блоков 1 опроса. Каждое число Xj под действием управляющего сигнала проходит через свою J -ю группу блоков 1опроса на соответствующие входы Пгг) -входовых элементов ИЛИ 3. Блок 2анализа реализует логическую функцию признака того, что в (. -х разрядах сравниваемых чисел содержатся все нули . 5 Блок индикации k работает при р венстве двух или более чисел из гг сравниваемых и при определении гру пы чисел относительно максимальног числа, превосходящих некоторый порог RL . При равенстве двух или более чи сел блок Ц индикации выявляет случаи: два или более чисел из m срав ниваемых равны и отличны от нуля; все сравниваемые числа равны нулю. случаи выявляютсяС помощью 7(1 7 И1 7 переменных Z поступающих на входы блока k индика ции от соответствующих блоков 1 по следовательного опроса младших разрядов. После окончания переходных процессов, вызванных управляющим на выходах блоков 1 опроса трех групп блоков 1 последовательного опроса, через кЬторые передаются равные мак симальные числа появляется сигнал логической единицы. Одновременно ма симальное число появляется на выходных шинах устройства. Для выполнения сравнения путем выделения минимальных чисел достаточно на входные шины устройства вместо прямого сигнала соответствующего двоичного разряда подать его инверсию. Тогда на каждом шаге (на информационных выходах блоков 1 опроса соответству щего этому шагу ряда блоков 1 опроса ) выделяются максимальные обратные коды чисел, что соответствует минимальным прямым кодам., Группа чисел относительно минимального чис ла выявляет также,как и в случае выя ления группы чисел относительно макс мального числа. По сравнению с известным данное техническое решение дает возможност повысить быстродействие устройства блоков сравнения. Формула изобретения 1. Устройство для сравнения mn-разрядных чисел, содержащее m групп по п блоков опроса, п блоков анализа, п элементов ИЛИ, блок индикации, причем входная шина каждого i-ro разряда каждого -го числа соединена с L -м информационным входом го блока опроса, где ,2..., m , 1 1 ,2,... П , первой группы блоков onpocaj о т л и 2 чающееся тем, что, с целью повышения быстродействия, в нем каждый информационны выход с-го эазряда J--го блока опроса J -и групп°ы соединен с информационным входом L-ro разряда i -го блока опроса (L + группы, а информационный выход каждого 1-го разряда каждого блока опроса группы подключен к i -му входу С-го элемента ИЛИ, вход L -го разряда каждого то блока опроса L -и группы соединен с первым управляющим входом (f -го блока опроса L -и группы и с J-м входом L-ro блока анализа, выход которого подключен к вторым входам управления блоков опроса 1 -и группы, третьи входы управления всех блоков опроса соединены с шиной управления устройством, управляющий выход каждого j-ro блока опроса I-и группы подключен к j-му входу i-и групвходов блока инпы информационных дикации. 2. Устройство по п.1, о т л и ч аю щ е е с я тем, что каждый блок опроса содержит п -входовой регистр, элементы И, ИЛИ, причем каждый i- -1Й информационный вход блока соединен с входом L -го разряда регистра,а выход каждого L-ro разряда регистра подключен к информационному выходу -го разряда блока и к i -му входу элемента ИЛИ, выход которого соединен с управляющим выходом блока, первый управляющий вход блока подключен к первому входу первого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, второй управляющий вход блока подключен к второму входу первого элемента И и к первому входу второго элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, выход которого подключен к входу установки в нулевое состояние регистра, третий управляющий вход блока соединен .с вторым входом второго элемента И. 3. Устройство по п.1, отличащее с я тем, что каждый блок нализа состоит из m элементов НЕ, ыходы каждого -го из которых оединены с j -м входом элемента И, ходы элементов НЕ подключены к вхоам блока, а выход элемента И соедиен с выходом блока.

4, Устройство поп.1,отлича ю щ е е с я тем, что блок индикации содержит п групп по m элементов ийдикации в каждой, п переключателей, причем каждый j -и вход каждой L -и группы информационных входов соединен с первым входом i-ro элемента индикации V -и группы, шина единичной константы через i-и переключатель подключена к вторым входам элементов индикации I -и группы.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР ff , кл, G 06 F 7/3, 19б5.

2.Авторское свидетельство СССР

№ ij66510, кл. G 06 F 7/02, 1972 (прототип) ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения максимального из т двоичных чисел | 1980 |

|

SU875376A1 |

| Устройство для выбора упорядоченной последовательности данных | 1983 |

|

SU1109738A1 |

| Устройство для моделирования сетевых графов | 1981 |

|

SU1013965A1 |

| Устройство для выделения экстремальных чисел | 1983 |

|

SU1109736A2 |

| Устройство для моделирования сетевых графов | 1983 |

|

SU1151979A1 |

| Устройство для выделения экстремальных чисел | 1981 |

|

SU1003070A1 |

| Устройство для выделения экстремальных чисел | 1982 |

|

SU1059563A1 |

| Устройство для упорядочивания чисел | 1984 |

|

SU1241228A1 |

| Устройство для сортировки чисел | 1981 |

|

SU960800A1 |

| Система коммутации | 1985 |

|

SU1317447A1 |

Авторы

Даты

1982-04-15—Публикация

1980-05-27—Подача