Изобретение относится к автомати ке и вычислительной технике и может быть использовано в цифровых вычислительных машинах. Известно устройство для выделени экстремального из nm разрядных двоичных чисел, содержащее nm входовых элементов ИЛИ, nm разрядных регистров, m трехвходовых элементов И и одного m входового элемента ИЛИ на каходое из двоичных чисел. Прямые выходы регистров поразрядно соедине ны с входами п входовых элементов ИЛИ ПЗ. Недостатком этого устройства явл ется сложность. Наиболее близким по технической сущности к предлагаемому являет ся устройство для сравнения mn разрядных чисел,состоящие из элементов ИЛИ, п« блоков сравнения, mn блокоэ последовательного опроса и блока индикации 2 . Недостатком известного устройств является сложность. Цель изобретения - упрощение устройства. Поставленная цель достигается тем, что в устройстве для определения максимального из двоичных чисел содержсцдем m групп элементов И, m групп элементов памяти, m групп элементов ИЛИ, многовходовыс элементы ИЛИ, управлякхцие элементы И, регистр результата, элементы згщержки, причем вход управления началом работы устройства соединен с первым входом первого управляющего элемента И и со входом первого элемента задержки, выход каждого I-го элемента задержки, где ,2,...,(п-1), п - количество разрядов сравниваемых чисел подключен к первому входу (i +1)-го управляющего элемента И и ко входу (i+l)-ro элемента задержки, выход (n-l)-ro элемента задержки соединен с выходной шиной устройства, выход каждого j-ro управляющего элемента И, где ,2,...,n подключен к информационному входу j-ro разряда регистра результата, инверсный выход каждого первого элемента памяти К-ой группы, где ,2,...,т соединен с первым входом первого элемента И К-ой группы, выход Ксокдого из которых подключен ко входу установки в нулевое состояние второго элемента памя,ти К-ой группы и к первому входу первого элемента ИЛИ К-ой группы, выход ка;адого Р-го элемента ИЛИ каждой

К-ой группы, где ,2,...,(п-2) соединен с первым входом (Р+1) элемента ИЛИ К-ой группы, выход каждого 1-го элемента памяти К-ой группы, где ,3,.,.(п-1) подключен к первому входу 1-го элемента И К-ой группы, выход которого подключен ко второму входу (1-1)-го элемента ИЛИ К-ой группы, прямой выход каждого i-ro элемента памяти К-ой группы соединен с К-ым входом i-ro многовходового элемента ИЛИ, выход каждого из которых подключен ко второму входу

i-ro управляющего элемента И, вы- ход каждого i-го управляющего элемента И соединен со вторьоми входами

i-ых элементов И всех групп.

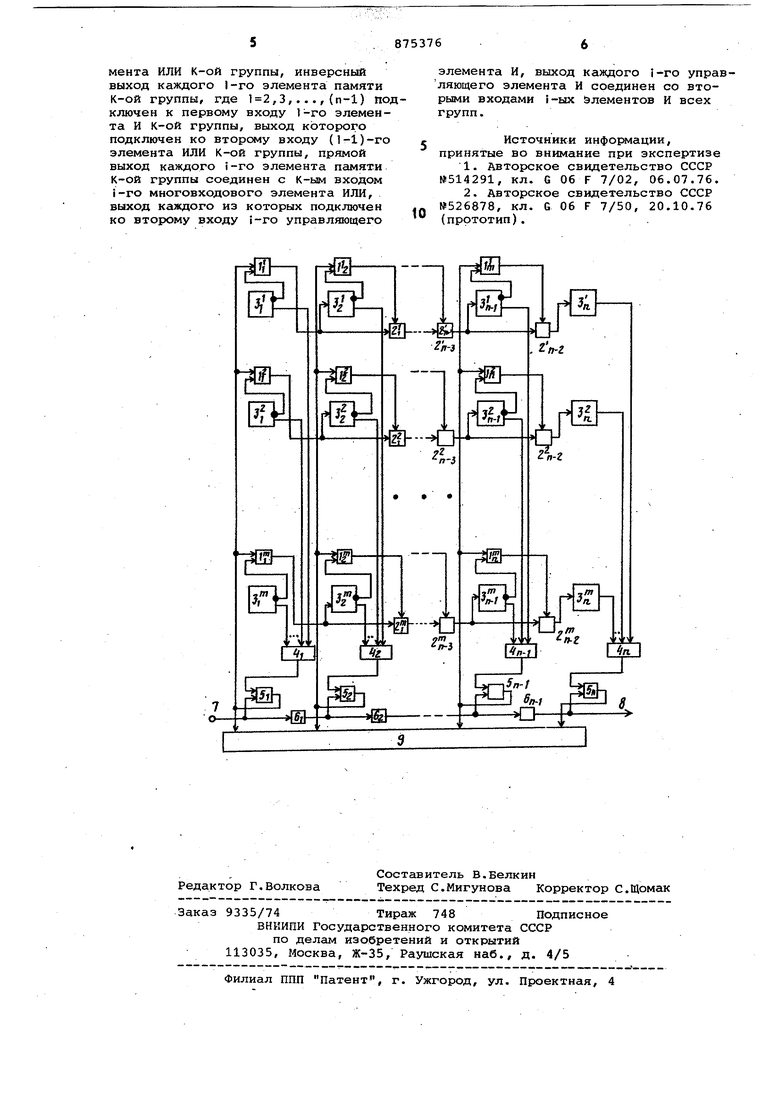

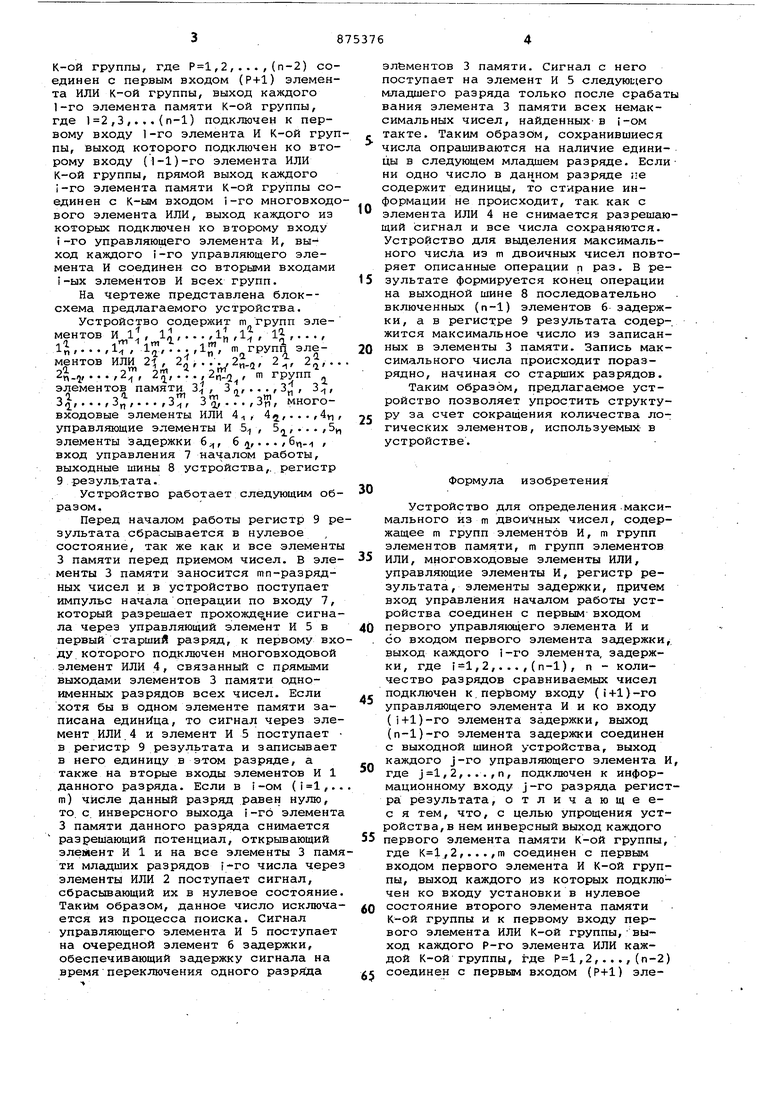

На чертеже представлена блок-схема предлагаемого устройства.

Устройство содерхшт m групп элементов , 1,..., i;, ,1, 1|,...,

,..., , 1 , ... ,1;;, m групп элементов ИЛИ 2i( , 2,... ,2.2 2, 2,.. 2., ...,27, 25;, . . . , 2;j22 групп , элементов памяти 3, Зп,., 3,

з1Э -ollloni om мнот-оJ,...,Jf,,...,J, qj,.., много

входовые элементы ИЛИ 4 , 4,. . . ,4vi, управляющие элементы И 5 , 5,j,.. .,5„ элементы задержки 6, 6 /i,. .. , 6,. , вход управления 7 началом работы, выходные шины 8 устройства,, регистр 9 реэультата.

Устройство работает следующим образом.

Перед началом работы регистр 9 результата сбрасывается в нулевое состояние, так же как и все элементы 3 памяти перед приемом чисел. В элементы 3 памяти заносится mn-разрядных чисел и в устройство поступает импульс начала операции по входу 7, который разрешает прохожд,ние сигнала через управляющий элемент И 5 в первый старший разряд, к первому входу которого подключен многовходовой элемент ИЛИ 4, связанный с прямыми выходами элементов 3 памяти одноименных разрядов всех чисел. Если хотя бы в одном элементе памяти записана единица, то сигнал через элемент ИЛИ 4 и элемент И 5 поступает в регистр 9 результата и записывает в него единицу в этом разряде, а также на вторые входы элементов И 1 данного разряда. Если в i-ом (,. m) числе данный разряд равен нулю, то с инверсного выхода i-г6 элемента 3 памяти данного разряда снимается разрешающий потенциал, открьтающий элемент И 1 и на все элементы 3 памяти младших разрядов -го числа через элементы ИЛИ 2 поступает сигнал, сбрасывающий их в нулевое состояние Таким образом, данное число исключается из процесса поиска. Сигнал управляющего элемента И 5 поступает на очередной элемент б задержки, обеспечивающий задержку сигнала на время переключения одного разряда

элементов 3 памяти. Сигнал с него поступает на элемент И 5 следуюьчего младшего разряда только после срабаты вания элемента 3 памяти всех немаксимальных чисел, найденных-в |-ом такте. Таким образом, сохранившиеся числа опрашиваются на наличие единицы в следующем младшем разряде. Если ни одно число в данном разряде i-e содержит единицы, то стирание информации не происходит, так. как с элемента ИЛИ 4 не снимается разрешающий сигнал и все числа сохраняются. Устройство для выделения максимального числа из m двоичных чисел повторяет описанные операции р раз. В результате формируется конец операции на выходной шине 8 последовательно включенных (п-1) элементов 6 задержки, а в регистре 9 результата содержится максимальное число из записанных в элементы 3 памяти. Запись максимального числа происходит поразрядно, начиная со старших разрядов. Таким образом, предлагаемое устройство позволяет упростить структу5 РУ счет сокращения количества логических элементов, используемых в устройстве.

Формула изобретения

Устройство для определения-максимального из m двоичных чисел, содержащее m групп элементов И, m групп элементов иамятк, m групп элементов

5 ИЛИ, многовходовые элементы ИЛИ, управляющие элементы И, регистр результата, элементы задержки, причем вход управления началом работы устройства соединен с первым входом

0 первого управляквдего элемента И и . со входом первого элемента задержки,, выход каждого i-ro элемента, задержки, где ,2,...,(п-1), п - количество разрядов сравниваемых чисел

подключен к.перйому входу (i+l)-ro управляющего элемента И и ко входу (i+l)-ro элемента задержки, выход (п-1)-го элемента задержки соединен с выходной шиной устройства, выход каждого j-ro управляющего элемента И, где ,2,...,п, подключен к информационному входу j-го разряда регистра результата, отличающеес я тем, что, с целью упрощения устройства, в нем инверсный выход каждого

5 первого элемента памяти К-ой группы, где ,2,...,т соединен с первым входом первого элемента И К-ой группы, выход каждого из которых подключен ко входу установки в нулевое

0 состояние второго элемента памяти К-ой группы и к первому входу первого элемента ИЛИ К-ой группы, -выход каждого р-го элемента ИЛИ каждой К-ой группы, где ,2,...,(п-2)

5 соединен с первым входом (Р+1) элемента ИЛИ К-ой группы, инверсный выход каждого 1-го элемента памяти К-ой группы, где ,3,...,(п-1) поключен к первому входу 1-го элемента И К-ой группы, выход которого подключен ко второму входу (1-1)-го элемента ИЛИ К-ой группы, прямой выход каждого i-го элемента памяти К-ой группы соединен с К-ым входом i-ro многовходового элемента ИЛИ, выход каждого из которых подключен ко второму входу i-ro управляющего

элемента И, выход каждого i-ro управляющего элемента И соединен со вторыми входами i-ых Элементов и всех групп.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР №514291, кл. G Об F 7/02, 06.07.76.

2.Авторское свидетельство СССР №526878, кл. G 06 F 7/50, 20.10.76

0 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения максимального из @ чисел | 1981 |

|

SU999041A1 |

| Устройство для сравнения @ @ -разрядных двоичных чисел | 1981 |

|

SU983703A1 |

| Устройство для выделения максимального числа | 1982 |

|

SU1043634A1 |

| Устройство для определения максимального из @ -двоичных чисел | 1983 |

|

SU1173408A1 |

| Устройство для определения наименьшего из @ чисел | 1980 |

|

SU903864A1 |

| Устройство для определения максимального числа из группы чисел | 1980 |

|

SU877523A1 |

| Генератор псевдослучайных чисел | 1980 |

|

SU907548A1 |

| Устройство для сравнения мN-разрядных чисел | 1980 |

|

SU920702A1 |

| Цифровой фильтр | 1985 |

|

SU1350823A1 |

| Устройство для выделения экстремального из -разрядных двоичных чисел | 1978 |

|

SU752326A1 |

Авторы

Даты

1981-10-23—Публикация

1980-02-15—Подача