Изобретение относится к импу.Л ьсной технике и может быть использовано в различных отраслях машиностроения, в частности в атомном машиностроении и котлостроении, а т.акже в металлургическом производстве при сборе и обработке информации о ходе технологических процессов, например сварки,термообработки, выплавки и внепечной обработки стали, а также в автоматизированных системах управления технологическими процессами.

При сборке и обработке информации о ходе технологических процессов, а также управления технологическими процессами возникает необ}содимость задержки на заданный отрезок времени информации, представлен ной в виде импульсной последовательности с переменным интервалом импульсов и характеризующей параметры процесса. Причем время задержки может превышать несколько интервалов следования импульсов.

Известна полупроводниковая линия задержки, содержащая п последовательно соединенных сложных инверторов, резистори в эми,ттерных цепях тран- зисторов парафазных каскадов всех инвсрюров соединены с общей линией через ч ofiiiiHH резистор 1.

Недостатком известного устройства является его сложность.

Наиболее близким к изобретению является дискретно-аналоговая линия задержки, содержащая блок управления, ключи записи и считывания, запоминающие ячейки, состоящие из ключа и запоминающего конденсатора, Олок преобразования, операционные усипители,

10 подключенные между выходами и входами запоминающих, звеньев, образованных из двух параллельно включенных четных и нечетных запоминающих ячеек, каждая из которых состоит из

5 ключа записи., сигнальный вход которого является входом ячейки, ключа считывания, выход которого является выходом ячейки, и параллельно соединенных запоминающего конденсатора и

20 ключа, выход которых подключен к общей шине, а вход - к выходу ключа записи к входу ключа считывания, при этом блок преобразования подключен своим сигнальным входом к источ25нику сигналов, выходом - к входу первого запоминающего звена, дополнительным выходом - к нулевому отводу линии задержки и управляющими входами - к дополнительным выходам

30 блока управ.1ения, а дополнительные

выходы всех операционных усилителей- к соответствующим отводам линии задержки , управляющие входы ключей четных и нечетных запоминающих ячеек подсоединены соответственно к третьему и первому выходам блока управления, управляющие входы ключей считывания четных запоминающих ячеек - соответственно к четвертому и второму входам блока управления, управляющие входы ключей считывания четных запоминающих ячеек - к первому и второму выходам блока управления, управляющие входы ключей считывания нечетных запоминающих ячеек - к третьему и четвертому выходам блока управления 2.

Недостатки этого устройства следующие: число ячеек в устройстве задержки во много раз превышает число импульсов, поступающих на вход устройства за время задержки, что приводит к значительному усложнению устройства, трудностям реализации, снижению надежности; устройство не позволяет плавно регулировать величину за держки, поскольку для этого требуетс синхронное регулирование параметров ячеек на одну и ту же величину, что весьма сложно и не представляется воможным. Целью изобретения является повышение надежности путем сокращения числа запоминающих ячеек с одновременным обеспечением плавности регулировки величины задержки, .

Поставленная цель достигается тем что в устройство для задержки импульсных сигналов, содержащее ключи и запоминающие ячейки, состоящие из разрядного ключа и конденсатора, введены компаратор, источник эталонного напряжения, элемент И, элемент ИЛИ,, а в каждую ячейку - триггер и зарядный резистор, причем число ячеек определяется максимальным числом импульсов, приходящихся ца. вход устройства за время задержки, при этом входом устройства являются входы ячеек, соединенные параллельно, а входом каждой из ячеек является единичный вход триггера, нулевой выход которого соединен с управляющим входом разрядного ключа, подключенного параллельно конденсатору, соединен, ному через зарядный резистор с источником питания, единичный выход триггера подключен к стробирующему входу ключа сброса, а нулевые входы триггеров через ключи сброса соединены с выходом компаратора, информационные входы которого подключены к конденсаторам ячеек, а вход источника опорного напряжения - с источником эталонного напряжения, ячейки соединены в кольцо посредстврм соединения единичного .выхода триггера предьщущей ячейки с входом синхронизации триггера

последующей ячейки, при этом единичный выход триггера последней ячейки соединен с входом синхронизации триггера первой ячейки через элемент ИЛИ второй вход которого подключен через элемент И к нулевым выходам триггеров ячеек, кроме того, нулевой выход триггера каждой предыдущей ячейки соединен с управляющим входом сброса каждой последующей ячейки , выход компаратора соединен с выходной клеммой устройства.

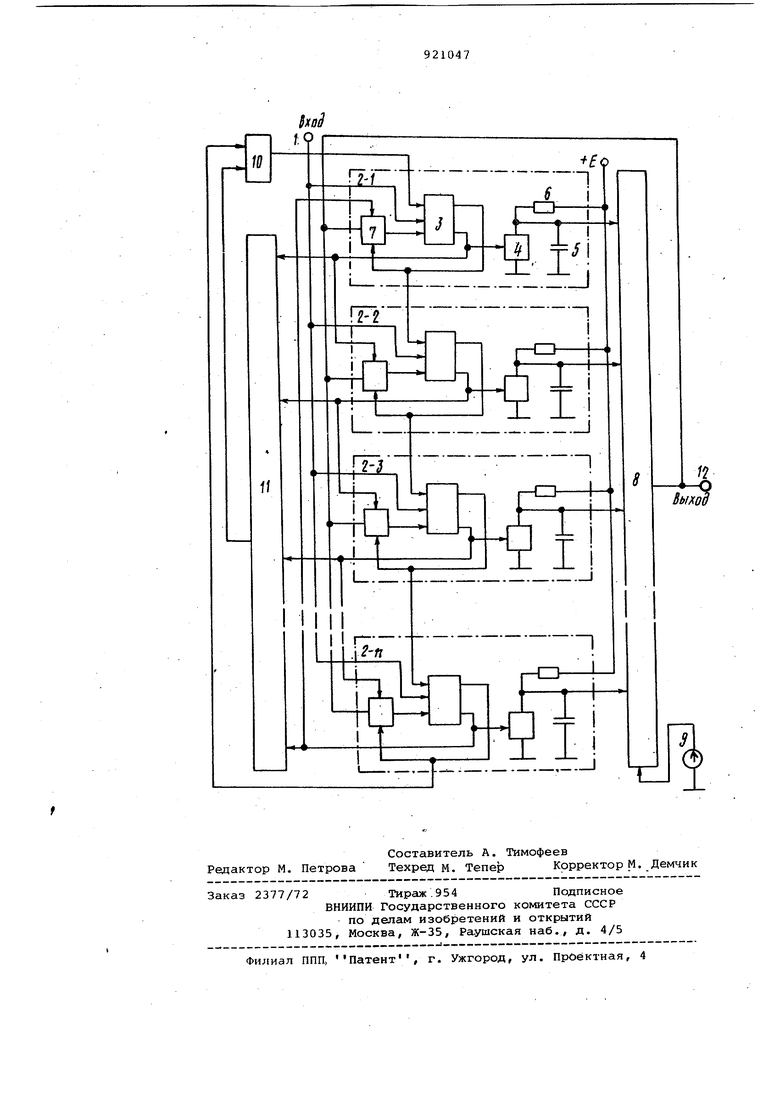

На чертеже представлена функциональная схема устройства.

Устройство содержит входную клемму 1 дли подключения источника сигнала, ячейки (2-1) - (2-п), число которых определяется максимальным числом импульсов импульсной последовательности, поступающих на вход устройства за время задержки . Каждая из ячеек (2-1) - (2-п) содержит триггер 3, разрядный ключ 4, конденсатор 5, зарадный резистор 6,. ключ сброса 7, единичный вход триггера 3 подключен к входной клемме устройства, нулевой выход триггера 3к входу управления разрядного ключа 4, подключенного параллельно конденсатору 5, которлй через зарядный резистор 6 соединен с источником питания ЕЛ, единичный выход .триггера подключен к стробирующему входу ключа 7 сброса, компаратор 8, информационные входы которого подключены к конденсатору 5 ячеек, выход компаратора через ключ 7 сброса соединен о нулевыми входами триггеров 3 ячеек, источник опорного напряжения 9, подключенный к входу опорного напряжения компаратора 8, ячейки соединены в кольцо посредством подключения единичного выхода триггера 3. каждой предьщущей ячейки к входу синхронизации триггера 3 каждой последующей ячейки, при этом единичный выхсд триггера последующей ячейки подключе к входу синхронизации первичной ячейки через элемент -10 ИЛИ, второй вход которого через элемент 11 И подключе к нулевым в э1ходам триггеров ячеек, кроме того, нулевой выход триггера каждой предыдущей ячейки подключен к входу управления ключа.сброса каждой последующей ячейки. Выход 12 устройства подключен к выходу компаратора 8.

Устройство работает следующим образом.

в исходном состоянии триггеры 3 ячеек сброшены и находятся в нулевом состоянии, разрядные ключи 4 открыты высоким потенциалом, поступающим с нулевых выходов триггеров, конденсаторы 5 разряжены. Причем триггер первой ячейки открыт по единичному входу высоким потенциалом, поступающим с элемента 10 ИЛИ и образующимся в результате .высоких потенциалов на все входы элемента И 11 с нулевых выходов ячеек, разрешая прием информации по единичному входу триггером 3 ячейки 2-1, а прием информации триггерами остальных ячеек запрещен низкими потенциалами, поступающими с единичных выходов предыдущих ячеек. В момент времени То первый импульс импульсной последовательности поступает на входную клемму 1 устройства и переводит триггер 3 ячейки 2-1 из нулевого состояния в единичное. При этом разрядный ключ 4 первой ячейки закрывается и начинается заряд конденсатора 5 через резистор б, что приводит к линейному нарастанию напряжения на первом вход компаратора 8. Кроме того, высокий потенциал, поступающий с единого выхода триггера 3 первой ячейки, разре шает прием информации триггером 3 ячейки 2-2 и разрешает управление ключом 7 сброса ячейки 2-1, высокий потенциал, поступающий с нулевого выхода триггера 3 ячейки 2-п, открывает ключ 7 сброса, при этом нулевой вход триггера 3 ячейки 2-1 под ключается к выходу компаратора 8, Низкий потенциал, поступающий на пер вый вход элемента И 11 с нулевого SKt хода триггера 3 ячейки 2-1, запрещает прием информации триггером 3 ячей ки 2-1 пО единичному входу. Второй и пульс импульсной последовательности переводит в единичное состояние триг гер 3 ячейки 2-2. При этом разрядный ключ 4 ячейки 2-2 закрывается и натчинается заряд конденсатора 5 через регулятор, что приводит к линейному нарастанию напряжения на втором вход компаратора 6. Кроме того,.разрешается управление .ключом 7 сброса ячей ки 2-2, низкий потенциал, поступающий с нулевого выхода триггера 3 ячейки 2г1, сохраняет закрытое соато яние ключа 7 сброса ячейки .2-2 и раз решается прием информации по единичному входу триггера 3 ячейки 2-3. . Через время л Т дт+ дт на входе устройства появляется третий импульс При этом триггер 3 ячейки 2-3 устанавливается в единичное состояние/ начинается заряд конденсатора 5 ячей ки 2-3, разрешается управление ключом сброса 7 ячейки 2-3 и прием информации триггером 3 ячейки 2-4. Через время д.Т Tj напряжение HS первом входе компаратора 8 достигает эталонного, при этом на выходе компаратора 8 появляется высокий потенциал, поступающий через открытый . ключ 7 сброса на триггер 3 ячейки 2и устанавливающий триггер 3 в нулево состояние, разрядный ключ 4 открывается и конденсатор 5 ячейки 2-1 быстро разряжается, компаратор 8 возвращается в исходное состояние. При этом на выходе 12 устройства формируется импульс, задержанный относительно первого входного импульса на время Tj. Через время лТ Т«+ дт напряжение на втором входе компаратора достигает величины эталонного напряжения, и на выходе компаратора 8 появляется высокий потенциал, триггер 3 ячейки 2-2 устанавливается в нулевое состояние, конденсатор 5 ячейки 2-2 быстро разряжается через открывшийся ключ 4, компаратор 8 устанавливается в исходное состояние, на выходе устройства формируется импульс, задержанный относительно второго входного импульса на время дТ Т . Через время Т Те + лТ+ дТ на выходе устройства аналогичным образом сформулируется импульс, задержанный относительно третьего входного импульса на время аТ Tj. Через время Т, равное временному интервалу между первым и к-импульсом, увеличенному на время задержки Т|, на выходе устройства появится импульс, задержанный относительно к-го входного импульса на время задержки Tj. Таким образом, на выходе устрой- ства через время Т после поступления к-го импульса на выходе устройства формируется импульсная последова.тельность из к импульсов, каждый из которых задержан относительно соответствующего входного на время задержки Щ . Регулируя величину эталонного напряжения, можно плавно изменять величину Тя времени задержки. Предлагаемое устройство позволяет задерживать импульсы с переменным интервалом следования на время Т|., за которое на вход устройства поступает к импульсов при количестве ячеек устройства задержки, не превышающем к, т.е. Сократить количество ячеек устройства задержки в 5 + 15 раз по сравнению с известными устройствами. Это упроцает конструкцию, уменьшает габариты и повышает надежность устройства. Кроме того, устройство позволяет плавно регулировать величину задержки, что расширяет функциональные возможности устройства задержки. . Формула изобретения Устройство для задержки импульсных сигналов, содержащее ключи и запомингиощие ячейки, состоящие из ключа и конденсатора, отличающеес я тем, что, с целью повышения надежности путем сокращения числа запоминающих ячеек с одновременнымобеспечением плавности регулировки величины задержки, в него введены компаратор, источник эталонного напряжения, элемент И,элемент ИЛИ, а в каждую ячейку - триггер и заь ядный резистор, при этом к входной клемме устройства подключены входы ячеек, соединенные параллельно, а входом каждой из ячеек является единичный вход триггера, нулеврй выход которого соединен с управляющим входом разрядного ключа, подключенного параллельно конденсатору, соединенному, через разрядный резистор с источником питания, единичный выход триггера подключен к стробирующему входу ключа сброса, а нулевые входы триггеров через ключи сброса соединены с выходом компаратора, информацион-, нце входы которого подключены к конденсаторам ячеек, а вход источника опорного напряжения соединен с источником эталонного напряжения; ячейки соединены а кольцо посредством соединения единичного выхода триггера

предыдущей ячейки с входом синхронизации триггера последующей ячейки, при этом единичный выход триггера последней ячейки соединен с входом синхронизации триггера первой ячейки через элемент ИЛИ, второй вход которого подключен через элемент И к нулевым выходам триггеров ячеек, кроме того, нулевой выход триггера каждой предыдущей ячейки .соединен с управляющим входом ключа сброса каждой последующей ячейки, выход компаратора соединен с выходной клеммой устройства.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 478430, кл. Н 03 Н 7/30,27.10.72.

2.Авторское свидетельство СССР № 665393, кл. Н 03 Н 7/30, 06.12.76 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода во временной интервал | 1985 |

|

SU1300637A1 |

| Устройство для определения экстремальной точки температурно-частотной характеристики кварцевых резонаторов | 1982 |

|

SU1034149A2 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

| Аналого-цифровой преобразователь узкополосных сигналов | 1983 |

|

SU1115224A2 |

| Устройство для измерения гистерезиса @ характеристик | 1985 |

|

SU1247797A1 |

| Генератор трапецеидального сигнала | 1986 |

|

SU1324093A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С САМОКОНТРОЛЕМ | 2010 |

|

RU2431233C1 |

| Устройство автоматического контроля монтажа с радиоэлементами | 1984 |

|

SU1190312A1 |

| Преобразователь амплитудного значения импульсного напряжения в постоянное напряжение | 1990 |

|

SU1716599A2 |

Авторы

Даты

1982-04-15—Публикация

1980-07-07—Подача