Область техники

Изобретение относится к вычислительной технике и может быть использовано в системах автоматизированного контроля, сбора и обработки информации.

Уровень техники

Известен аналого-цифровой преобразователь (авт. св. №1529454, кл. Н03К 1/48, 1987), содержащий три компаратора, реверсивный счетчик, преобразователь кода в напряжение, элементы И, ИСКЛЮЧАЮЩЕЕ ИЛИ, коммутатор, генератор импульсов, триггер, источники опорных напряжений. Недостатками АЦП являются низкие точность, быстродействие преобразования, большое количество компараторов.

Известен преобразователь напряжения в код (авт. св. СССР №711677, кл. Н03К 13/17, 1980), содержащий буферный усилитель, сравнивающее устройство, регистр, узел разрядных переключателей, резистивную матрицу, устройство управления, логическое устройство и два переключателя. Недостатками устройства являются низкое быстродействие и точность контроля, так как контрольная операция состоит из двух контрольных тактов, а введение разрядных переключателей снижает точность контроля.

Известно устройство аналого-цифрового преобразования (авт. св. СССР №809554, кл. Н03К 13/17, 1979) содержащее два сравнивающих устройства, регистр, узел разрядных переключателей, две резистивные матрицы, логические элементы И, ИЛИ, элемент задержки, два триггера, переключатели, устройство управления, логический блок. Недостатком устройства является недостаточно высокое значение достоверности контроля за счет низкой полноты контроля.

Известно устройство аналого-цифрового преобразования (патент РФ №2020751, кл. Н03М 1/46, 1991), содержащее регистр последовательного приближения, двуматричный преобразователь кода в напряжение, генератор импульсов, элементы И, ИЛИ, НЕ, триггеры, элементы задержки, источники эталонных напряжений. Недостатком устройства является реконфигурация устройства только при неисправностях или погрешностях, относящихся к младшему разряду устройства, а также относительно невысокая полнота контроля.

Наиболее близким по технической сущности к предлагаемому устройству является АЦП (патент РФ №2251209, кл. Н03М 1/46, 2004), содержащее четыре компаратора, регистр последовательного приближения, двуматричный преобразователь кода в напряжение, генератор импульсов, элементы И, ИЛИ, НЕ, триггеры, элементы задержки, источники эталонных напряжений. Недостатком устройства являются невысокая полнота контроля, так как не выявляются неисправности, при возникновении которых обеспечивается компенсация измеряемого сигнала, однако погрешность кодирования выходит за допуск.

Сущность изобретения

Задача предлагаемого устройства состоит в повышении быстродействия контроля и достоверности контроля за счет увеличения полноты контроля при возникновении, например, таких неисправностей, как изменения «весов» разрядов, а также отказов разрядных ключей типа «константный нуль».

Поставленная задача решается тем, что в предлагаемый АЦП с самоконтролем, содержащий два компаратора, первые входы которых соединены с входной шиной, вторые входы первого компаратора соединены с выходом первой (m+1)-ой разрядной резистивной матрицы R-2R, (m+2)-ой резистор 2R которой подсоединен к источнику эталонного напряжения отрицательной полярности, вторые входы второго компаратора соединены с выходом второй (m+1)-ой разрядной резистивной матрицы R-2R, (m+2)-ой резистор 2R которой подсоединен к источнику эталонного напряжения положительной полярности, входы m-разрядных резистивных матриц R-2R с первого по m через электронные ключи подсоединены к выходам регистра последовательных приближений с первого по m, а входы коммутации электронных ключей соответственно подсоединены к корпусной шине и источнику эталонного напряжения положительной полярности, выход второго компаратора соединен с первым входом первого элемента ИЛИ, второй вход которого через первый элемент НЕ соединен с выходом второго компаратора, выход первого элемента ИЛИ подсоединен к первому входу первого элемента И, а через второй элемент НЕ к первому входу второго элемента ИЛИ, выход которого подсоединен к нулевому входу первого триггера, второй вход второго элемента ИЛИ подсоединен к единичному входу второго триггера, нулевой вход которого соединен с шиной «СБРОС», единичный вход первого триггера соединен с шиной «начало преобразования», блок индикации неисправностей, подсоединенный к единичному выходу первого триггера, второй вход первого элемента И соединен с выходом второго компаратора, а выход - с входом D регистра последовательного приближения, С вход которого подсоединен к выходу генератора импульсов, вход  - к корпусной шине, a

- к корпусной шине, a  вход - к нулевому выходу первого триггера, в него введены три элемента И, один элемент ИЛИ, три элемента задержки, шесть электронных ключа и сдвигающий регистр, входы которого подключены к выходам с 1 до m регистра последовательного приближения, а выходы - к управляющим входам с 1 до m+1 разрядных электронных ключей, шина «СДВИГ» соединена с выходом второго элемента И, первый вход которого через первый элемент задержки подсоединен к выходу второго элемента НЕ, второй вход - к нулевому выходу второго триггера, шина «СБРОС» подсоединена к шине «установка 0» сдвигающего регистра, m выход регистра последовательного приближения соединен с первым входом третьего элемента И через второй элемент задержки, второй вход третьего элемента И соединен с выходом первого элемента ИЛИ и первым входом четвертого элемента И, второй вход которого соединен с m+1 выходом регистра последовательных приближений и входом третьего элемента задержки, выходы третьего и четвертого элементов И подсоединены к соответствующим входам третьего элемента ИЛИ, выход которого соединен с единичным входом второго триггера, при этом выход электронного ключа старшего разряда соединен с входами коммутации первого и второго электронных ключей, а выходы - с первыми выводами резисторов 2R старших разрядов резистивных матриц R-2R, вторые выводы которых подсоединены соответственно к входам коммутации третьего и четвертого электронных ключей, а выходы - ко вторым выводам резисторов 2R вторых старших разрядов, управляющие входы первого и второго электронных ключей подсоединены к единичному выходу первого триггера, а управляющие входы третьего и четвертого ключей к нулевому выходу первого триггера, выход (m+1)-го электронного ключа к первому входу коммутации пятого электронного ключа, второй вход - к источнику эталонного напряжения положительной полярности, а выход - к первому выводу (m+1)-го резистора 2R второй резистивной матрицы R-2R и первому входу коммутации шестого электронного ключа, второй вход - к источнику эталонного напряжения отрицательной полярности, а выход - к первому выводу (m+1)-го резистора 2R первой резистивной матрицы R-2R, выходы сдвигающего регистра со 2 по m+1 подсоединены на вторые входы группы элементов И, третьи входы - к выходу третьего элемента задержки.

вход - к нулевому выходу первого триггера, в него введены три элемента И, один элемент ИЛИ, три элемента задержки, шесть электронных ключа и сдвигающий регистр, входы которого подключены к выходам с 1 до m регистра последовательного приближения, а выходы - к управляющим входам с 1 до m+1 разрядных электронных ключей, шина «СДВИГ» соединена с выходом второго элемента И, первый вход которого через первый элемент задержки подсоединен к выходу второго элемента НЕ, второй вход - к нулевому выходу второго триггера, шина «СБРОС» подсоединена к шине «установка 0» сдвигающего регистра, m выход регистра последовательного приближения соединен с первым входом третьего элемента И через второй элемент задержки, второй вход третьего элемента И соединен с выходом первого элемента ИЛИ и первым входом четвертого элемента И, второй вход которого соединен с m+1 выходом регистра последовательных приближений и входом третьего элемента задержки, выходы третьего и четвертого элементов И подсоединены к соответствующим входам третьего элемента ИЛИ, выход которого соединен с единичным входом второго триггера, при этом выход электронного ключа старшего разряда соединен с входами коммутации первого и второго электронных ключей, а выходы - с первыми выводами резисторов 2R старших разрядов резистивных матриц R-2R, вторые выводы которых подсоединены соответственно к входам коммутации третьего и четвертого электронных ключей, а выходы - ко вторым выводам резисторов 2R вторых старших разрядов, управляющие входы первого и второго электронных ключей подсоединены к единичному выходу первого триггера, а управляющие входы третьего и четвертого ключей к нулевому выходу первого триггера, выход (m+1)-го электронного ключа к первому входу коммутации пятого электронного ключа, второй вход - к источнику эталонного напряжения положительной полярности, а выход - к первому выводу (m+1)-го резистора 2R второй резистивной матрицы R-2R и первому входу коммутации шестого электронного ключа, второй вход - к источнику эталонного напряжения отрицательной полярности, а выход - к первому выводу (m+1)-го резистора 2R первой резистивной матрицы R-2R, выходы сдвигающего регистра со 2 по m+1 подсоединены на вторые входы группы элементов И, третьи входы - к выходу третьего элемента задержки.

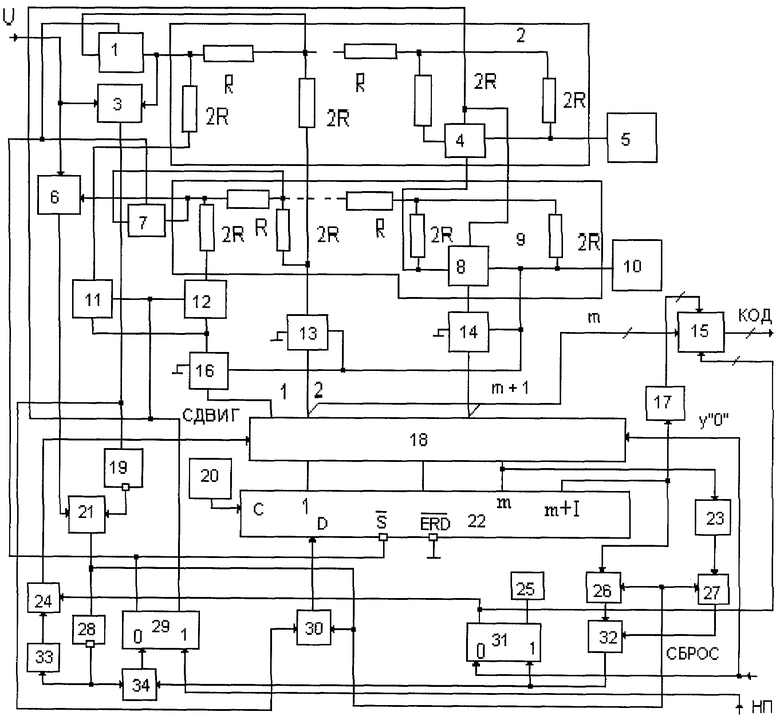

Сущность предлагаемого изобретения поясняется чертежом. На чертеже представлена функциональная схема аналого-цифрового преобразователя с самоконтролем.

Перечень фигур

На чертеже изображены:

1 - электронный ключ,

2 - первая (m+1)-разрядная резистивная матрица R-2R,

3 - первый компаратор,

4 - электронный ключ,

5 - источник эталонного напряжения отрицательной полярности,

6 - второй компаратор,

7, 8 - электронные ключи,

9 - вторая (m+1)-разрядная резистивная матрица R-2R,

10 - источник эталонного напряжения положительной полярности,

11, 12, 13, 14 - электронные ключи,

15 - группа элементов И,

16 - электронный ключ,

17 - элемент задержки,

18 - сдвигающий регистр, с асинхронной параллельной установкой данных и сбросом, а также с тактовым сигналом только для сдвига вправо данных,

19 - элемент НЕ,

20 - генератор импульсов,

21 - элемент ИЛИ,

22 - регистр последовательного приближения,

23 - элемент задержки,

24 - элемент И,

25 - блок индикации неисправностей,

26, 27 - элементы И,

28 - элемент НЕ,

29 - триггер,

30 - элемент И,

31 - триггер,

32 - элемент ИЛИ,

33 - элемент задержки,

34 - элемент ИЛИ.

Сведения, подтверждающие возможность осуществления изобретения

Функциональная схема АЦП приведена на чертеже. Преобразование напряжения в код производится с сокращенным циклом кодирования и самоконтролем в процессе функционирования. Устройство работает следующим образом. При поступлении сигнала «начало преобразования» (НП) триггер 29 устанавливается в состояние «1», а по шине «СБРОС» нулевой вход триггера 31 и сдвигающий регистр 18 в состояние «0». При этом на входе  регистра последовательного приближения (РПП) 22 устанавливается уровень «0» и на выходе РПП 22 формируется код

регистра последовательного приближения (РПП) 22 устанавливается уровень «0» и на выходе РПП 22 формируется код  . Кроме того, от единичного выхода триггера 29 срабатывают электронные ключи 4, 8 и (m+1)-е, (m+2)-е резисторы 2R двух (m+1) разрядных резистивных матриц R-2R 2 и 9 подключаются соответственно к источникам эталонных напряжений Uэт, -Uэт. Такое подключение резисторов позволяет сформировать на выходах двух резистивных матриц R-2R 2 и 9 соответственно напряжения -Uмл.р и Uмл.р. На выходе двух резистивных матриц 2 и 9 сформируются соответственно напряжения: Uкомп+Uмл.р и Uкомп-Uмл.p. В момент, когда Uкомп-Uмл.р≤Uизм+Uкомп+Uмл.p, на выходе компаратора 6 формируется уровень «0», а на выходе компаратора 3 - уровень «1». Тогда на выходе элемента 21 установится уровень «1», который через элемент 28 установит триггер 29 в состояние «0». Сигнал с выхода элемента 24 произведет сдвиг кода, содержащегося в сдвигающем регистре 18 на один разряд вправо. При этом запрещающий уровень «0» с единичного выхода триггера 29, поступив на управляющие входы электронных ключей 4 и 8, произведет размыкание цепей коммутации между (m+1)-ым и (m+2)-ым резисторами 2R резистивных матриц 2 и 9, а электронный ключ 4 произведет подключение (m+1)-го резистора 2R резистивной матрицы 2 ко входу электронного ключа 8, который произведет коммутацию (m+1)-го резистора 2R резистивной матрицы 9 к выходу электронного ключа 14. Таким образом, (m+1)-ый разряд становится рабочим, а оконечные резисторы 2R двух резистивных матриц 2 и 9 сформируют постоянно включенные напряжения младшего разряда Uмл.р и -Uмл.р.

. Кроме того, от единичного выхода триггера 29 срабатывают электронные ключи 4, 8 и (m+1)-е, (m+2)-е резисторы 2R двух (m+1) разрядных резистивных матриц R-2R 2 и 9 подключаются соответственно к источникам эталонных напряжений Uэт, -Uэт. Такое подключение резисторов позволяет сформировать на выходах двух резистивных матриц R-2R 2 и 9 соответственно напряжения -Uмл.р и Uмл.р. На выходе двух резистивных матриц 2 и 9 сформируются соответственно напряжения: Uкомп+Uмл.р и Uкомп-Uмл.p. В момент, когда Uкомп-Uмл.р≤Uизм+Uкомп+Uмл.p, на выходе компаратора 6 формируется уровень «0», а на выходе компаратора 3 - уровень «1». Тогда на выходе элемента 21 установится уровень «1», который через элемент 28 установит триггер 29 в состояние «0». Сигнал с выхода элемента 24 произведет сдвиг кода, содержащегося в сдвигающем регистре 18 на один разряд вправо. При этом запрещающий уровень «0» с единичного выхода триггера 29, поступив на управляющие входы электронных ключей 4 и 8, произведет размыкание цепей коммутации между (m+1)-ым и (m+2)-ым резисторами 2R резистивных матриц 2 и 9, а электронный ключ 4 произведет подключение (m+1)-го резистора 2R резистивной матрицы 2 ко входу электронного ключа 8, который произведет коммутацию (m+1)-го резистора 2R резистивной матрицы 9 к выходу электронного ключа 14. Таким образом, (m+1)-ый разряд становится рабочим, а оконечные резисторы 2R двух резистивных матриц 2 и 9 сформируют постоянно включенные напряжения младшего разряда Uмл.р и -Uмл.р.

Кроме того, запрещающий уровень с единичного выхода триггера 29, поступив на управляющие входы электронных ключей 11 и 12, отсоединит резисторы 2R старших разрядов резистивных матриц 2 и 9 от выхода электронного ключа 16. Таким образом, первые старшие разряды двух резистивных матриц 2 и 9 будут выключены. Разрешающий уровень с нулевого выхода триггера 29, поступив на управляющие входы электронных ключей 1, 7, произведет замыкание резисторов R между первым и вторым резисторами двух старших разрядов 2R. При этом вторые входы компараторов 3 и 6 будут соответственно подключены к резисторам 2R вторых старших разрядов двух резистивных матриц 2 и 9. Применение электронных ключей 11 и 12 можно было бы исключить, если входное сопротивление каждого компаратора 3 и 6 превышало бы величину резистора R резистивных матриц 2 и 9 не менее чем в 1000 раз. Поэтому, чтобы исключить критичность величин входного сопротивления компараторов 3, 6 и резисторов R двух резистивных матриц R-2R, в устройство введены электронные ключи 11 и 12.

При работоспособном АЦП сдвиг кода на один разряд вправо в сдвигающем регистре и отключение старшего разряда не приведут к изменению величин компенсирующих напряжений Uкомп±Uмл.р.

В случае, если значение измеряемого напряжения выходит за допуск в моменты времени от первого такта до m-го включительно, то с задержкой, определяемой элементом задержки 23, триггер 31 установится в состояние «1» и блок 25 индицирует сигнал «АЦП не годен». В случае, если значение измеряемого напряжения выходит за допуск после сдвига кода на один разряд вправо, то на первом входе элемента 26 будет уровень «1», который через элемент 32 установит триггер 31 в состояние «1» и блок 25 индицирует сигнал «АЦП не годен». В этих двух случаях код не будет считан из элемента 18 во внешнее устройство. Если U>Uкомп-Uмл.р и U<Uкомп+Uмл.р, то триггер 31 останется в состоянии «0» и (m+1)-ый импульс с необходимой задержкой, определяемой элементом задержки 17, считает параллельный код из сдвигающего регистра 16 во внешнее устройство через группу элементов И 15.

Таким образом, в данном АЦП производится процесс преобразования и одновременно самоконтроль с полнотой самоконтроля, меньшей единицы (поскольку не выявляются такие неисправности АЦП, при возникновении которых обеспечивается компенсация измеряемого сигнала - отказы разрядных переключателей типа «константный нуль» и такие неисправности, как изменения «весов» разрядов). После окончания преобразования и сдвига кода в сдвигающем регистре на один разряд вправо на дополнительном контрольном такте производится самоконтроль АЦП с полнотой контроля, равной единице, так как выявляются неисправности, при возникновении которых обеспечивается уравновешивание измеряемого напряжения компенсирующими.

Рассмотрим неисправности в АЦП, приводящие к обеспечению уравновешивания измеряемого напряжения компенсирующим.

1. Неисправность типа «константный нуль» в младшем разряде. Пусть U=4,98 В, число разрядов - m=10 (диапазон входных напряжений от 0 до 10 В). В результате преобразования напряжения получаем код 0111111110 (результат самоконтроля - положительный, так как 4,97 В<4,98 В<4,99 В). При этом неисправность младшего разряда не обнаруживается. Затем на дополнительном такте производится сдвиг кода, и на выходе резистивных матриц 2 и 9 формируются соответственно напряжения 4,95 В и 4,97 В, так как после сдвига на один разряд вправо в сдвигающем регистре сформировался код 0111111100, эквивалентный напряжению 4,96 В. Поскольку в резистивных матрицах 2 и 9 добавляются соответственно величины - Uмл.р и Uмл.р, то на их выходах будут соответственно напряжения 4,95 В и 4,97 В. Так как 4,98 В>4,95 В и 4,98 В>4,97 В, то на выходе элемента ИЛИ 21 сформируется уровень «1». Триггер 31 будет установлен в состояние «1» и высветится сигнал «АЦП не годен». При этом выходной код не будет считываться из АЦП во внешнее устройство, так как он хотя и верный, но в АЦП имеется неисправность «константный нуль» в младшем разряде.

2. Неисправность, вызванная изменением «веса» второго старшего разряда АЦП. Пусть U=7,49 В, «вес» второго старшего разряда равен 2,509 В, вместо 2,5 В. Производим преобразование входного напряжения в код и получаем код 101111111. На выходах резистивных матриц 2 и 9 формируются соответственно напряжения 7,48 В и 7,5 В. Сравнение входного напряжения с компенсирующими дает положительный результат. После сдвига кода на один разряд вправо на выходах резистивных матриц 2 и 9 формируются соответственно напряжения 7,498 В и 7,518 В. Так как 7,49 В<7,498 В и 7,49 В<7,518 В, то формируется сигнал «АЦП не годен». Выходной код не будет считываться из АЦП во внешнее устройство, так как выходной код является верным, но в АЦП «вес» второго старшего разряда выходит за пределы допустимых значений, т.е. 2,509 В вместо 2,5 В.

Для оценки достоверности самоконтроля АЦП воспользуемся обобщенным показателем достоверности контроля (самоконтроля), предложенным М.Н.Селуяновым в статье «Обобщенный показатель достоверности контроля аналоговых и цифровых устройств». //Радиоэлектронные системы. - Сер. Общетехническая. - 1993 - Вып.1. - С.56-73.

D=Рск[Рацп+νc(Qaцп-β-кα)-α(1-к)]+Pацпqи+Qацп[qн+qни(1-νc)],

где Рацп - вероятность работоспособного состояния АЦП;

Рск - вероятность работоспособного состояния средств самоконтроля АЦП;

qи, qн - вероятность такого отказа средств самоконтроля АЦП, при котором они признают АЦП соответственно работоспособным, неработоспособным независимо от его действительного состояния;

qни - вероятность такого отказа средств самоконтроля АЦП, при котором выдаваемая ими оценка противоположна истинному состоянию АЦП;

νc - полнота самоконтроля;

α - вероятность ложного отказа;

β - вероятность необнаруживаемого отказа;

При расчете достоверности самоконтроля на этапе проектирования, когда закон распределения вероятностей qи, qн, qни неизвестен, можно принять, что их распределение происходит по закону равной вероятности. Тогда можно считать, что qи=qн=qни=Qск/3. Тогда

D1=Рск[Рацп+νc(Qацп-β-кα)-α(1-к)]+0,33Qск[1+Qацп(1-νс)].

В случае, если νc=1, то

D2=[Рск(1-α-β)]+0,33Qск,

При Рск=0,99975; Рацп=0,997; νс=0,9; β=4,6*10-4; α=1,2*10-4 имеем

D1=0,9984912;

При νc=1 имеем

D2=0,9992526. Следовательно D2>D1.

Таким образом, в данном устройстве после окончания преобразования и сдвига кода в сдвигающем регистре на один разряд вправо на дополнительном контрольном такте производится самоконтроль АЦП в двустороннем допуске (а не в одностороннем допуске за два такта) с полнотой контроля, равной единице, и выявляются неисправности, при возникновении которых обеспечивается уравновешивание измеряемого напряжения компенсирующими (т.е. неисправности типа «константный нуль» и изменения «весов» разрядов АЦП), что показано на вышеуказанных примерах. Следовательно, повышается достоверность контроля (методическая его составляющая - полнота контроля) и быстродействие самоконтроля.

Изобретение относится к вычислительной технике. Технический результат заключается в повышении быстродействия и достоверности контроля. Аналого-цифровой преобразователь с самоконтролем содержит два компаратора, регистр последовательного приближения, сдвигающий регистр, двуматричный преобразователь кода в напряжение, генератор импульсов, элементы И, ИЛИ, НЕ, триггеры, элементы задержки, электронные ключи, индикатор неисправностей, источники эталонных напряжений. 1 ил.

Аналого-цифровой преобразователь с самоконтролем, содержащий два компаратора, первые входы которых соединены с входной шиной, вторые входы первого компаратора соединены с выходом первой (m+1)-й разрядной резистивной матрицы R-2R, (m+2)-й резистор 2R которой подсоединен к источнику эталонного напряжения отрицательной полярности, вторые входы второго компаратора соединены с выходом второй (m+1)-й разрядной резистивной матрицы R-2R, (m+2)-й резистор 2R которой подсоединен к источнику эталонного напряжения положительной полярности, входы m-разрядных резистивных матриц R-2R с первого по m через электронные ключи подсоединены к выходам регистра последовательных приближений с первого по m, а входы коммутации электронных ключей соответственно подсоединены к корпусной шине и источнику эталонного напряжения положительной полярности, выход второго компаратора соединен с первым входом первого элемента ИЛИ, второй вход которого через первый элемент НЕ соединен с выходом первого компаратора, выход первого элемента ИЛИ подсоединен к первому входу первого элемента И, а через второй элемент НЕ к первому входу второго элемента ИЛИ, выход которого подсоединен к нулевому входу первого триггера, второй вход второго элемента ИЛИ подсоединен к единичному входу второго триггера, нулевой вход которого соединен с шиной «СБРОС», единичный вход первого триггера соединен с шиной «начало преобразования», блок индикации неисправностей, подсоединенный к единичному выходу первого триггера, второй вход первого элемента И соединен с выходом второго компаратора, а выход - с входом D регистра последовательного приближения, С вход которого подсоединен к выходу генератора импульсов, вход  - к корпусной шине, a

- к корпусной шине, a  вход - к нулевому выходу первого триггера, группу элементов И, первые входы которых подсоединены к нулевому выходу второго триггера, а выход - к шине «КОД», отличающийся тем, что, с целью повышения быстродействия и достоверности контроля, в него введены три элемента И, один элемент ИЛИ, три элемента задержки, шесть электронных ключей и сдвигающий регистр, входы которого подключены к выходам с 1 до m регистра последовательного приближения, а выходы - к управляющим входам с 1 до m+1 разрядных электронных ключей, шина «СДВИГ» соединена с выходом второго элемента И, первый вход которого через первый элемент задержки подсоединен к выходу второго элемента НЕ, второй вход - к нулевому выходу второго триггера, шина «СБРОС» подсоединена к шине «установка 0» сдвигающего регистра, m выход регистра последовательного приближения соединен с первым входом третьего элемента И через второй элемент задержки, второй вход третьего элемента И соединен с выходом первого элемента ИЛИ и первым входом четвертого элемента И, второй вход которого соединен с m+1 выходом регистра последовательных приближений и входом третьего элемента задержки, выходы третьего и четвертого элементов И подсоединены к соответствующим входам третьего элемента ИЛИ, выход которого соединен с единичным входом второго триггера, при этом выход электронного ключа старшего разряда соединен с входами коммутации первого и второго электронных ключей, а выходы - с первыми выводами резисторов 2R старших разрядов резистивных матриц R-2R, вторые выводы которых подсоединены соответственно к входам коммутации третьего и четвертого электронных ключей, а выходы - ко вторым выводам резисторов 2R вторых старших разрядов, управляющие входы первого и второго электронных ключей подсоединены к единичному выходу первого триггера, а управляющие входы третьего и четвертого ключей к нулевому выходу первого триггера, выход (m+1)-го электронного ключа к первому входу коммутации пятого электронного ключа, второй вход - к источнику эталонного напряжения положительной полярности, а выход - к первому выводу (m+1)-го резистора 2R второй резистивной матрицы R-2R и первому входу коммутации шестого электронного ключа, второй вход - к источнику эталонного напряжения отрицательной полярности, а выход - к первому выводу (m+1)-го резистора 2R первой резистивной матрицы R-2R, выходы сдвигающего регистра со 2 по m+1 подсоединены на вторые входы группы элементов И, третьи входы - к выходу третьего элемента задержки.

вход - к нулевому выходу первого триггера, группу элементов И, первые входы которых подсоединены к нулевому выходу второго триггера, а выход - к шине «КОД», отличающийся тем, что, с целью повышения быстродействия и достоверности контроля, в него введены три элемента И, один элемент ИЛИ, три элемента задержки, шесть электронных ключей и сдвигающий регистр, входы которого подключены к выходам с 1 до m регистра последовательного приближения, а выходы - к управляющим входам с 1 до m+1 разрядных электронных ключей, шина «СДВИГ» соединена с выходом второго элемента И, первый вход которого через первый элемент задержки подсоединен к выходу второго элемента НЕ, второй вход - к нулевому выходу второго триггера, шина «СБРОС» подсоединена к шине «установка 0» сдвигающего регистра, m выход регистра последовательного приближения соединен с первым входом третьего элемента И через второй элемент задержки, второй вход третьего элемента И соединен с выходом первого элемента ИЛИ и первым входом четвертого элемента И, второй вход которого соединен с m+1 выходом регистра последовательных приближений и входом третьего элемента задержки, выходы третьего и четвертого элементов И подсоединены к соответствующим входам третьего элемента ИЛИ, выход которого соединен с единичным входом второго триггера, при этом выход электронного ключа старшего разряда соединен с входами коммутации первого и второго электронных ключей, а выходы - с первыми выводами резисторов 2R старших разрядов резистивных матриц R-2R, вторые выводы которых подсоединены соответственно к входам коммутации третьего и четвертого электронных ключей, а выходы - ко вторым выводам резисторов 2R вторых старших разрядов, управляющие входы первого и второго электронных ключей подсоединены к единичному выходу первого триггера, а управляющие входы третьего и четвертого ключей к нулевому выходу первого триггера, выход (m+1)-го электронного ключа к первому входу коммутации пятого электронного ключа, второй вход - к источнику эталонного напряжения положительной полярности, а выход - к первому выводу (m+1)-го резистора 2R второй резистивной матрицы R-2R и первому входу коммутации шестого электронного ключа, второй вход - к источнику эталонного напряжения отрицательной полярности, а выход - к первому выводу (m+1)-го резистора 2R первой резистивной матрицы R-2R, выходы сдвигающего регистра со 2 по m+1 подсоединены на вторые входы группы элементов И, третьи входы - к выходу третьего элемента задержки.

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1991 |

|

RU2020751C1 |

| ДВУХКАНАЛЬНЫЙ РЕЗЕРВИРОВАННЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2003 |

|

RU2251209C2 |

| Устройство аналого-цифрового преобразования с самоконтролем | 1989 |

|

SU1695498A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1277396A1 |

| US 6075478 A, 13.06.2000 | |||

| US 4800364 A, 24.01.1989 | |||

| EP 1887702 A1, 13.02.2008. | |||

Авторы

Даты

2011-10-10—Публикация

2010-06-11—Подача