Изобретение огносится к вычислительной технике и автоматике и может быть использовано в системах контроля цифре- вьпс вычислительных устройств. Известно устройство для контроля дешифратора, содержащее элемент ИЛИ, выход которого соединен с выходом устройства, блок аналогового суммирования, пер вый и второй пороговые элементы, причем входы устройства соединены с входами блока аналогового суммирования, выход которого через первый и второй пороговые элементы соещнен с входами элемента ИЛИ {1. Известно также устройство встроенного контроля дешифратора на п выходов, содержашее диодные ячейки, логические схемы НЕ и резисторы. Устройство состоит из двух диодных ячеек, имеющих по п входов каждая, и двух логических схем НЕ, соединенных между собой так, что каждый из п выходов дешифратора подключен к одному из п входов первой диодной ячейки через резистор и к одному из Y1 ВХОДОВ второй диодной ячейки - непосредственно, выход первой диодной ячейки соединен со входом первой логической схемы НЕ, а выход второй диодной ячейки через резистор - со входом второй логической схемы НЕ, выход первой схемы НЕ Через решстор подключен также ко входу второй логической схемы НЕ, выход которой является выходом устройства 21Недостатком указанных устройств является недостаточная полнота контроля дешифратораНаиболее близким по технической сущности к изобретению является устройство для контроля дешифратора, содержащее преобразователи код-аналог и сравнивающее устройство, причем входы и выходы дешифратора подключены через преобразователи к ось-аналог ко входам сра&нивающего устройства ГЗ. Однако это устройство обладает недостаточной точностью контроля ошибок типа перерождения, при котором возбуждаются две или более ложных вькопньк шин аешифратора, а сигнал на выхояной шнне соответствующей коровой комбинации отсутствует,

Ошибка не обнаруживается, если ошибочно возбужденные выходные шины Ьеши4 ратора вызывают на выхопе преобразователя коа аналог реакцию, эквивалентную реакции вызываемой правильно возбужде ной шиной.10

Для данного известного устройства реакция выходного преобразователя коданалог будет Неизменной , если вместо одной (1равильно возбуждённой выходной

ШИНЬ, будут ОШИбоШО возбуждены шины, 15

сумма номеров которых равна номеру, правильно возбужденной шины, и значит на выходе схемы сравн 1ия в обоих слу чаях будет сигнал нормы.

Так, например, если вместо выхода JQ дешифратс;)а соответсгаующего 6 возбужоены два выхода 2 и 4, то выходное напряжение в обоих случаях будет одним и тем же и известное устройство не сможет обнаружить неисправности.25

Анализ показывает, что при постро&г ИИ схем преобразователей код-аналог, обеспечивающих изменение выходного напряжения фопорциснально входному Коду, федставлвенноМу одноразрядным числом jo (так. Как на выходе дешифратсра), всегда будет иметь место возможность полу чения одного и того же или близкого по . величине выходного напряжения при замене однора ядного кода подачей управляюших сигналов на два и более входов.

Цедш изобретения - повышение точности Контроля дешифратора.

Поставленная цель достигается тем, что в устройство для контроля деигафратора, содержащее первый и второй 1чэеобразователи код-аналог и схему сравнения, причем входы и выходы контролируемого дешйфратфа соединены соответственно со входами первого и второго преобразователей код-аналог, выход первогО преобразователя копганалог соединен с первым входом схемы сравнения, выход которой является выходом устройства, введены источник эталонного напряжения и сумматор, причем выход источника эталон - ® ного на|Ц}Яжения соединен соответственно с первым входом сумматора, выход которого соединен со вторым входом схемы сравнения, выход первого 15 есбразоват&ля код-аналог соедини со вторым входом сумматора.

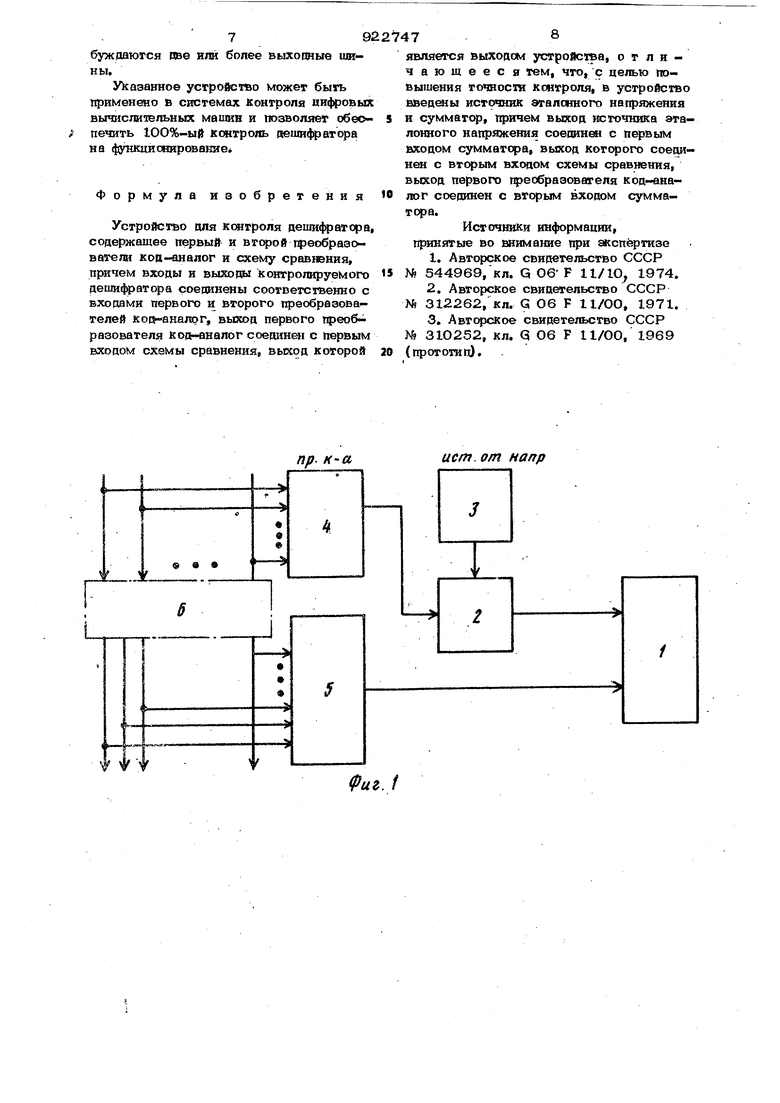

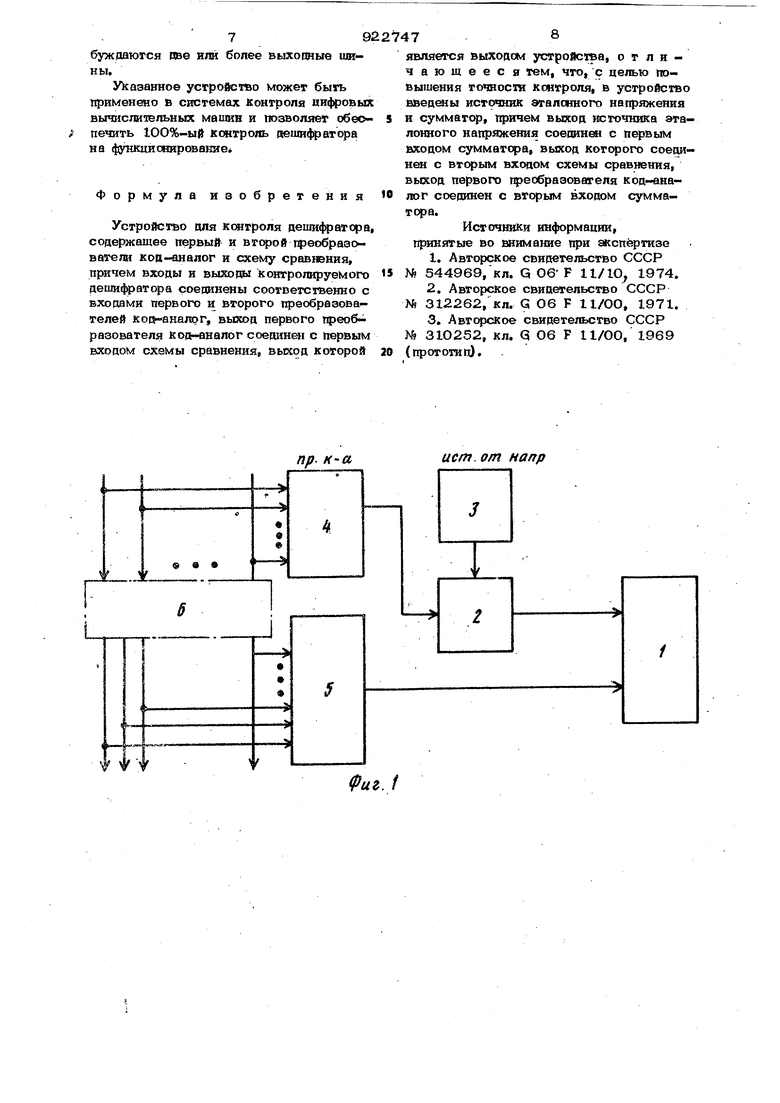

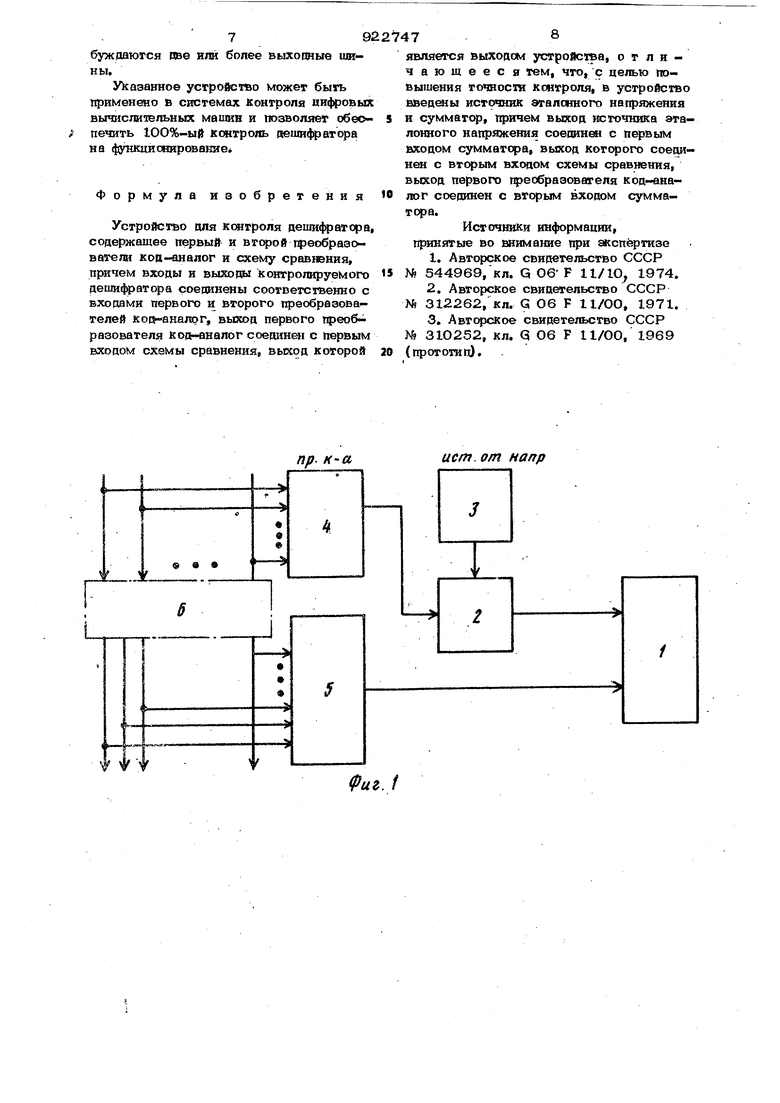

На фиг. 1 представлена блок- ;хема устройства для контроля дешифратора;

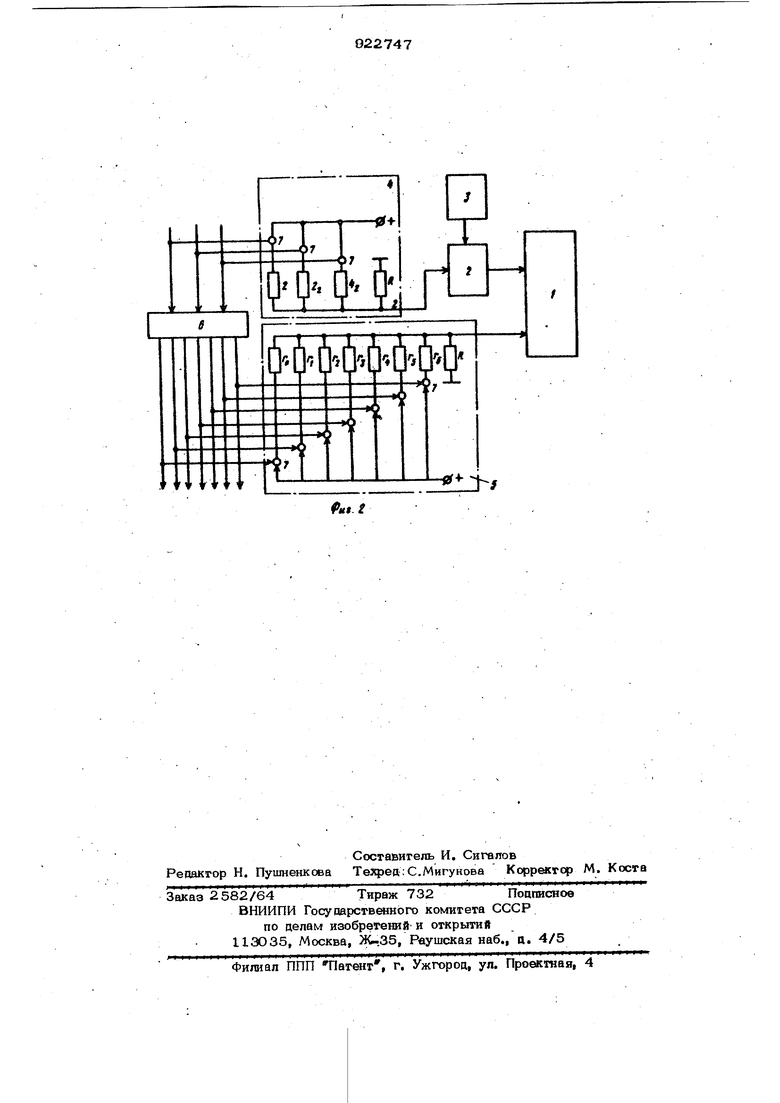

на фиг. 2 - .пример выполнения устрой ства на три входа.

Устройство содержит схему I сравнения, сумматор 2, истоиик 3 эталонного напряжения, первый и второй преобразователи 4 и 5 коп-аналог, де.шифратор 6. элементы И 7 входящие в преобразователи 4, 5. , Входы и выкоды деши4 тора 6 сооъветсгвенно подключены к входам преобразователя 4 и 5 коа-аналог. Выход образоваЕгеля 4 и выход историка 3 эталонного напряжения - к соответствующим входам сумматфа, а выход сумматора 2 . и выход преобразователя 5 кось-аналог подКлючетсы Ко входам схемы 1 сравнения.

Устройство работает следующим образом.

I Коды, поступающие на вход деши(й атфа 6, одновременно посту.пают на вход преобразователя 4 код-аналог. Преобразователь 4 код-аналог преобразует коды в пропорциональные им напряжения.С выхода преобразсеателя 4 код-аналог напряжение поступает на первый вход сумматора 2, на второй вход которого поддается эгалшное напряжа1ие UjfOT источника 3 эталонного напрямсения. Величина эталонного напряжения выбирается таким образом, чтобы она была больше величины напряжения формируемого преобразователем 4 Kof -аналог при максимальном коде на величину F|n , где. к дискретность преобразования. Суммарное напряжение поступает на вход устройства сравнения. С вьдходов дeшифpaтqpa сигналы, представляюише собой одноразрядный код, nociyпают на преобразователь 5 ко№-аналрг. В тфеобразователе 5 корнаналог величин резистфов выбраны так, что он преобразовывает оцщоразрядный код с выхода дешифратора в напряжение, величина которого равна величине эталонного напряжения увеличенной на величину, пропорциональную поданному Коду с дискретноС1ъю преобршзования.

Сигнал с выхода преобразователя 5 коп-аналог поступает на второй вход схемы 1 сравнения, котфое вырабать вает на своем выходе сигнал ошибки только в том случае, если напряжение

на его входах отличаются на величину большую UU .А это либо вместо требуемой будет возбуждена одна ложная шина (в этом случае выходное напряжение преобразователя 5 аналог -«од не будет соответствовать напряжению на выходе сумматора), либо возбуждены вместо требуемой две или более ложHbixjamH, либо будет воабуждена гребуемая и ложные шины. В цвух поспеаi-HHX случаях на выхоае преобразователя ,5 коре-аналог будет напряжение больше по величине напряжения Соответствующег максимальному как в этом случае в реаисторной сетке преобразователя 5 ко|% налог резисторы включаются параллельно, либо буоет отсутствовать ва бужоенная шина, преобразователь 4 KOCV аналог преобразует двоичный код в напрапкение. При выполнении по параллельной схеме веса резистсров в каждом раз ряде соответствуют весам соответствующих разрядов от О до л и образуют ряд 2 , ... 2р соответственно, где г -«& личина сопротивления определяаощая дискретность преобразования. Если примем, что Uj -rE/Q. , максимальная величина напряжения при наибо льшем коде Е /7 и величина напряжения на выходе преобразователя 4 код-аналог определяется вьфажением: 0.-Д. 1И т .f+R где 1 - числовое значение двоичного кода,-вьфаженного в десятично V системе счисления, равное ном ру выхода дешифратора; П - номер старшего разряда двоичного крда (начиная с О разряда); - напряженке источника питания; R- величина общего резистора параллельного преобразователя ,Напряжение на выходе сумматора будет равно напряжению на выходе преоб , разователя 5 кодг-аналог при правильном возбуждении шины и определяется еледующим образом l.p(Ai ) Е(еличина сопротивления резисторов в каждом резисторе выходного преобразователя 5 код-аналог определяется из следующего выражения i(a;.-u) ) Для выхода дешифратора соответству. ющего нулевому входному коду (т.е. гри i О) сопротивление резистора преобразователя 5 коснаналог будет равно Го«Л. При этом напряжение на выходе прео&разователя 5 код-аналог будет равно Е/2. С ростом выходное натзяжеяие бу дет увеличиваться до (4 1 )Е. Пусть, натфимер, на вход оеши атора поступил коц 1О1. В десятичной системе счисления эквивалент этого кода равен 5. Код включает разряды О, I, 2. .Единичные сигналы этого кода откроют соответствующие элементы и в ueriscc г и 4 . Через них потечет ток и на выходе сумматора появится напряжение ( 5R .С JHr+R) 5, Все выходные идшы дешифратора также связаны со входами элементов И 7, к выходам которых подключены резисторы. При правильно возбужде1шой шине в данном случае откроется клапан в цепи резистора Tj . Величина резистора г с , подключенного и к выходной шине дешифратора равна U ) Напряжение на выходе преобразователя 5 Koct-аналог будет равно o-i5 5-Г5СГ . Сигнал ошибки на выходе устройства сравнения будет отсутсовать. При несоответствию выходной возбужденной шины входному коду, возбуждение одной или нескольких выходных шин или отсутствие врзбужд«1ной шины равенства напряжения на выходе устройства сравнения не будет, а на выходе сравнивающего устройства появится сигнал ошибки. Как показал схемно-технический анализ и результаты испытаний устройства, предлагаемое устройство обеспечивая, как и известное, контроль ошибок дешифратора, характеризующихся отсутствием возбужденной шины несоответствия возбужденной выходной шины входному коду, кроме того, обеспечивает 10О% контроль ошибок типа перерождение при которых воз-

бужоаются две или более выхопные шины.

ykasaHHoe устройство может быть {фимеиено в системах контроля цифровых вычислительных машин и позволяет обес почить 1ОО%-ый контроль neura f)втора на функционирование

Формула изобретения

Устройство цля кштроля дешифратора, содержащее первый и преобразователи код-аналог и схему сравнения, причем входы и выходы контролируемого) дешифратора соединены соответственно с входами первого и второго преобразователей код-аналог, выхоп первого преоб« разователя кось налог соеанкеи с первым входом схемы сравнения, выход которой

является выходом устройства, отличающееся тем, что, с целью повышения точности контроля, в устройство введены источник эталшного напряжения и сумматор, причем выход источника эталонного напрязкения соединен с первым входом сумматора, выход которого соединен с вторым входом схемы сравнения, выход первого преобразователя код-аналог соединен с вторым входом сумматфа.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР N 544969,кл. Q Об F 11/Ю, 1974.

2.Авторское свидетельство СССР М 312262, кл. G Об F 11/ОО, 1971.

3.Авторское свидетельство СССР М 310252, кл. Q Об F 11/ОО, 1969 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| Устройство для моделирования разрывных функций | 1975 |

|

SU525125A1 |

| РЕЗЕРВИРОВАННЫЙ ИСТОЧНИК ТОКА | 2013 |

|

RU2512890C1 |

| ВСЕСОЮЗНАЯ Л. А. Шойхет, А. С. Белима, А. Г. Мелик-Аскаров, }j^,..^,..,.. ^^^,,,,.,.^^В. М. Гаврилюк, Б. И. Семеняк и А. А. Казьмина р^"—"!Н1'~1':ХН'''-;5\?{ЛЯ | 1970 |

|

SU287550A1 |

| Адаптивный классификатор | 1984 |

|

SU1220004A1 |

| ПРЕОБРАЗОВАТЕЛЬ АНАЛОГ ~ КОД | 1969 |

|

SU254220A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| СПОСОБ АВТОМАТИЧЕСКОГО КОНТРОЛЯ АККУМУЛЯТОРНОЙ БАТАРЕИ, СОСТОЯЩЕЙ ИЗ N ГАЛЬВАНИЧЕСКИ СВЯЗАННЫХ АККУМУЛЯТОРНЫХ ЭЛЕМЕНТОВ И УСТРОЙСТВО ДЛЯ ОСУЩЕСТВЛЕНИЯ АВТОМАТИЧЕСКОГО КОНТРОЛЯ | 2014 |

|

RU2557014C1 |

| Устройство для отображения информации (его варианты) | 1984 |

|

SU1262564A1 |

| Преобразователь цифрового кода в последовательность импульсов | 1989 |

|

SU1672566A1 |

. ff-a

ист. от напр

Фиг. /

Авторы

Даты

1982-04-23—Публикация

1980-01-17—Подача