(54) ИНТЕГРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегратор с автокоррекциейКОэффициЕНТА пЕРЕдАчи | 1978 |

|

SU805346A1 |

| Интегрирующий аналого-цифровой преобразователь | 1985 |

|

SU1279069A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1800616A1 |

| Способ интегрирующего аналого-цифрового преобразования и устройство для его осуществления | 1985 |

|

SU1381709A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Аналого-цифровой преобразователь параметров диэлькометрического датчика | 1985 |

|

SU1242801A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1200421A1 |

| Нелинейный преобразователь | 1988 |

|

SU1674172A1 |

| Аналого-цифровой преобразователь с промежуточным преобразованием в частоту | 1989 |

|

SU1644382A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1246376A1 |

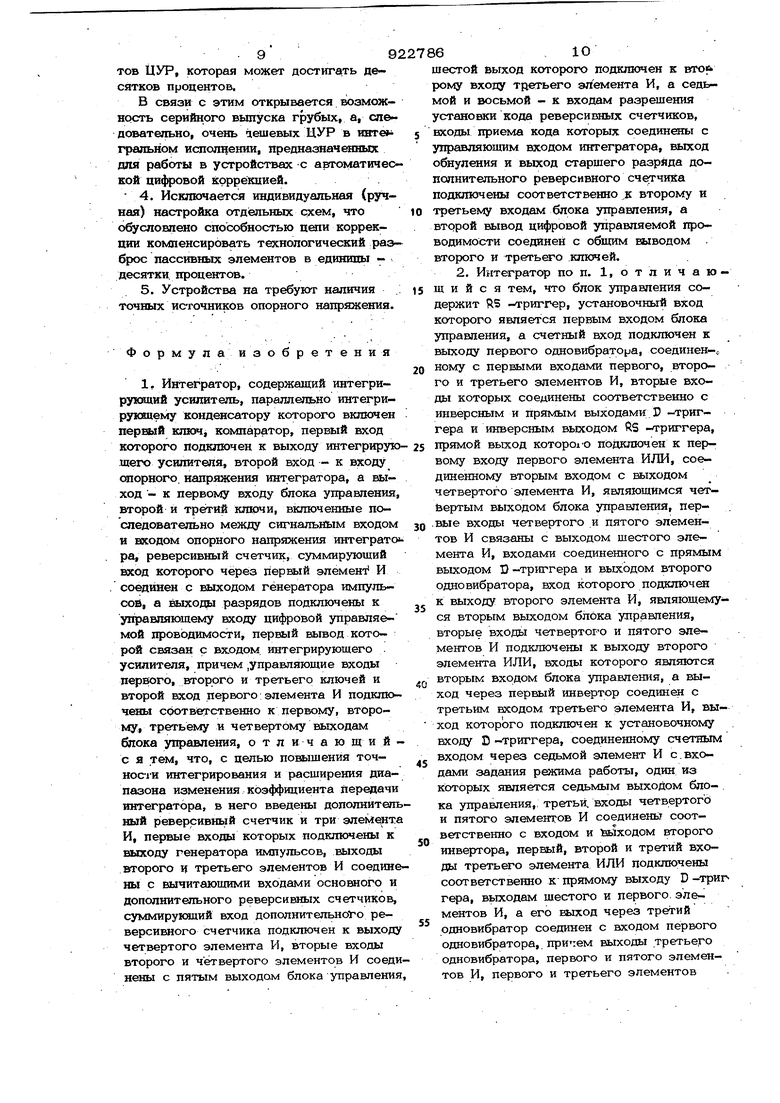

5 6227866

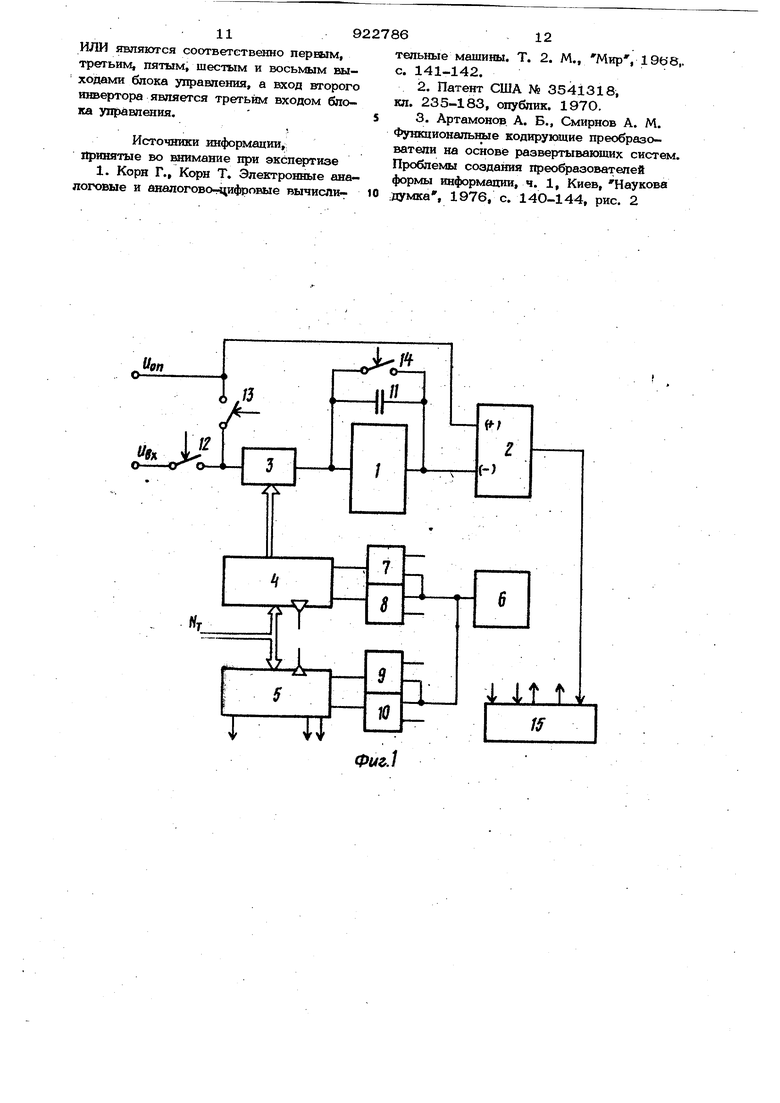

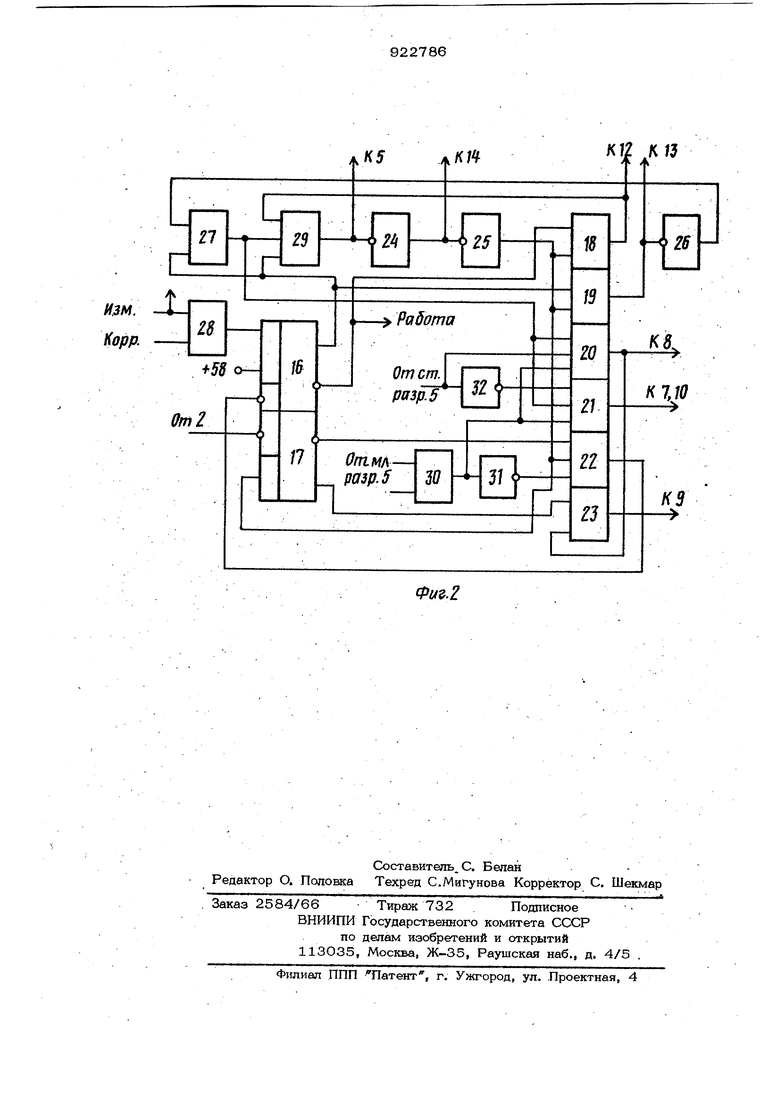

один из которых является седьмым выхо- входами ключей 12-14, входами разрешедом блока управления, третьи входы ния установки.кода счетчиков 4 и 5 и вертого и пятого элементов И соединены соответственно с входом и выходом второго инвертора, первый, второй и третий входы третьего элемента ИЛИ подключены соответственно к прямому выходу В триггера, выходам шестого и первого элементов И, а его выход через третий одновибратор соединен с входом первого одновибратора, причем выходы третьего одновибратора, первого и пятого элементов И, первого и третьего элементов ИЛИ являются соответственно первым, третьим, пятым, шестым и восьмым вь1- ходами блока управления, а вход второго инвертора является третьим входом блока управления. На фиг. 1 дана функциональная схема предлагаемого интегратора; на фиг. 2 -, один из возмо5КЕа.1х вариантов блока управления. Интегратор (фиг. 1) содержит интегрирующий усилитель 1, компаратор 2, цифровую управляемую проводимость . . (ЦУП) 3, реверсивные счетчики 4 и 5, генератор 6 импульсов, элементы И 710, интегрирующий конденсатор 11, клю чи 12-14 и блок 15 управления. Первый вход ЦУП 3 через ключи 12 и 13 соединен соответственно с сигнальным входом Ujj( и входом опорного напряжения Don интегратора, а второй вход подключен к инвертирующему входу интегрирующего усилителя 1. Конденсатор 11 и параллельно включенный ему ключ 14соединяют инвертирующий вход усилителя 1 и его. выход,. которйй прдключён к инвертирующему входу компаратора 2. Неинвертирующий вход компаратора 2 соединен с входом опорного напряжения интегратора. Выход генератора 6 подключен к первым входам элементов. И 7-10, выходы элементов И 7 и 8 со динены соответственно с вычитающим и су олирующим входами реверсивного счетчика 4, а выходы элементов И 9 и 10 подключены соответственно к вычитающему и суммирующему входам реверсивного счетчика 5. Входы приема кода счетчиков 4 и 5 соединены с управляьо.щим входом интегратора. Выходы раз-, рядов счетчика 4 подключены к управляв щим входам цифровой управляемой прово димости 3. Выход компаратора 2, а так же выход обнуления и выход старщего разряда счетчика 5 .подключены к вх.одам блока 15 управления, а выходы блока 15управления соединены с управляющим вторыми входами элементов И 7-10. Блок 15 управления (фиг. 2) содержит В-триггер 16, RS -триггер 17, выходы которых соединены с входами элементов И 18-22 и элемента ИЛИ 23, одновибраторы 24, 25 и 26, элементы И 27, 28, элементы ИЛИ 29, 30 н инверторы 31, 32. Входы элемента И 28 являются входами задания режима работы. Интегратор работает в трех режимах; первый - рабочий режим, когда интегратор выполняет интегрирование входного сигнала, второй - изменение КПИ, третий - коррекции КПИ. . .Для пояснения функционирования интегратора рассмотрим второй режим, так как первый выполняется обычным образом, а третий входит как составная часть во второй. Цикл работы в режиме изменения КПИ состоит из четырех различных тактов; в первом такте- производится прием кода, задающего значение требуемого 1Ш второй такт предназначен для установки нут левых начальных условий интегратора, в третьем такте вычисляется разность межДУ реальным и требуемым КПИ, четвертый такт - коррекция кода, задающего значение КПИ при условии его отличия от требуемого. Далее, если полученная после коррекции погрешность превышает заданную величину, такты 2, 3, 4 повторяются до уменьшения погрещности до требуемой. В третьем режиме работы устройства выполняются такты 2, 3 и 4. В первом такте на вход разрешения установки кода счетчика 4 подается сих нал, разрешаю.щий запись параллельного кода NT , з:адающего значение требуемого КПИ, на счетчик 4. Выходы счетчика управляют ключами ЦУП 3. Реальный КПИ, полученный после приема кода Nf . имеет приведенную погрешность, выраженную формулой ,т,,ЬЛА1., ц где л Ч - погрешность температурного и временного ухода конденсатора обратной связи и входного резистора, а также по-. грешность изготовления этих элементов, приведенная к эквивалентному измени1ию входной проводимости; дУд - погрешность, вносимая в ЦУП . . где - относительная погрешность ЦУП (погрешность изготовления); Уц, - макЬимальное значение,проводимости ЦУП, Во второмтакте замйквется ключ 1 (остальные разомкнуты) и разряжает конденсатор 11 до нуля. Одновременно код NT принимается на счетчик 5 подачей сигнала на вход разрешения установ ки кода счетчика 5. В третьем такте замыкается ключ 1 (остальные разомкнуты), а на второй вход элемет-а И 9 подается сигнал, раз решающий прохождение импульсов с гене ратора 6 на вычитающий вход счетчика 5. Интервал времени с момента подачи на вход интегратора напряжения OQ до момента сравнения, фиксируемого компа ратором 2, равен реальной постоянной времени интегратора. Частота генератора 6 выбирается таким образом, чтобы к моменту времени, равному требуемой постоянной времени, состояние счетчика 5 бьшо нулевым, тогда ко времени появления сигнала сравнения с компаратора на счетчик 5 прекращается подача импульсов и на нем фиксируется код, пропорциональный разности реальной и требуемой постоянной . Если состояние счетчика 5 нулевое, то коррекдня закончена, если нет - У9тройство переходит к четвертому такту рабочът, В четвертом такте, в зависимости от знака разности, находящейся в счетчике 5, подаются сигналы на элементы И 7 и 9 или на 8 и 10, разрешающие прохож дение импульсов с Генератора 6 на сумм рующие или вычитающие входы счетчико 4 и 3, а в момент равенства нулю содержимого счетчика 5 сигналы снимаются. Таким образом, в этом такте код разности, пропорциональный погрешности КПИ, вычитается или складывается с со держимым счетчика 4. Погрешность КПИ после первого такта коррекции определяется из формулы Д(ДЧ+йХ. ) .(uV4u4u,) гЛТ V t(6V+uXj Y,) ,(У(ЛУи,) 1t((AY-KA4u,) где ) - погрешность, вносимая оцсемой коррекции при компенсации погрешносги КПИ, равной(йУ i равИД .)c(uN+u4 ). После п такта коррекции погрешность КПИ выражается следующим образом:/,K rKWYj n(fX + ,)t...) -Иц)К)Число тактов коррекции определяется из выражения . gtf( 0 у,- (,) К,- I j f . I Ч Где о - дискретность изменения лроводимости ЦУП.. Число тактов коррекции для реальных устройств оказывается равным 2-4. Из сравнения формул видно, что при равных начальных условиях (в выражениях можно положить с ЧхсЛТ) уже на втором таасте коррекции предлагаемое устройство обеспечивает большую точность КПИ, чем известное. - Таким образом, предложенное устройство имеет следующие отличительные особенности, обусловливакивие эффективность его применения. 1.Возможность работы с ЕЫСОКОЙ точностью в широком температурном диапазоне, что объясняется способностью схем автоматически сохранять установленный КПИ вне зависимости от изменения внешних условий и характ истик : пассивных элементов устройства. 2.Возможность автоматической установки коэффициента передачи интегратора по сигналу, представленному в двоичном коде. 3.Отсутствие в схеме прецизионных и термостабильныэс пассивных элементов, что существенно рбпегчает изготовление устройств в интегральном-исполнении. К примеру, аналоговые юпочи, применяемые в пифроуправляемых резисторах, могут быть: а)с большим временем коммутации, так как эти ключи переключаются лишь в специально отведеннь1е моменты времени в режиме коррекции; б)с большим разбросом сопротивления открытого канала, потому что эта величина входит в погрешность элемен; тов ЦУР, которая может достигй1ть десятков процентов. В связи с этим открывается возможность серийного выпуска грубых, а, сяе доватепьно, очень чешевых ЦУР в инте гральном исполнении, предназначенных для работы в устройствах с автоматичес кой цифровой коррекцией. 4. Исключается индивидуальная (ручная) настройка отдельных схем, что обусловлено способностью цепи коррекции компенсировать технологический разброс пассивных элементов в едингаш десятки, процентов. 5. Устройства на требуют наличия точных источников опорного напряжения. Формула изобретения 1. Интегратор, содержащий интегрирующий усилитель, параллельно интегрирующему конденсатору которого включен первый клкн, компаратор, первый вход которого подключен к выходу интегрирую щехх) усилителя, второй вход - к входу опорного, напряжения интегратора, а выход - к первому входу блока управления второй и третий ключи, включенные последовательно между сигнальным входом и входом опорного напряжения интеграто ра, реверсивный счетчик, суммирующий вход которого через первый элемент И соединен с выходом генератора импульсое, а выходы разрядов подключены к управляющему входу цифровой управляемой проводимости, первый вьгеод которой связан с входом интегрирующего усилителя, причем .управляющие входы первого, второго и третьего ключей и второй вход первого; элемента И подключены соответственно к первому, второму, третьему и четвертому выходам блока управления, отличающийс я тем, что, с целью повыщения точНОС-1-И интегрирования и расщирения диапазона изменения коэффициента Передачи интегратора, в него введены дополнитель ный реверсивнь1Й счетчик и три элемента И, первые входы которых подключены к выходу генератора импульсов, выходы второго и третьего элементов И соедине ны с вычитающими входами основного и дополнительного реверсивных счетчиков, суммирующий вход дополнительного реверсивного счетчика подключен к выходу четвертого элемента И, вторые входы второго и четвертого элементов И соеди нены с пятым выходам блока управления шестой выход которого подключен к BTOI рому входу третьего элемента И, а седьмой и восьмой - к входам разрещения установки кода реверсивных счетчиков, входы приема кода которых соединены с управляющим входом интегратора, выход обнуления и выход старшего разрйда дополнительного реверсивного счетчика подключены соответственно ,к второму и третьему входам блока управления, а второй вывод цифровой управляемой проводимости соединен с общим выводом . второго и третьего ключей. 2. Интегратор по п. 1, о т л и ч а ю - щ и и с я тем, что блок управления содержит R5 -триггер, установочный вход которого является первым входом блока управления, а счетный вход подключен к выходу первого одновибратора, соединен-с ному с первыми входами первого, второго и третьего элементов И, вторые входы которых соединены соответственно с инверсным и прямым выходами Г -триггера и инверсным выходом RS -триггера, прямой выход KOTopoi-o подключен к первому входу первого элемента ИЛИ, соединенному вторым входом с выходом четвертого элемента И, являющимся четвертым выходом блока управления, первые входы четвертого и пятого элементов И связаны с выходом шестого элемента И, входами соединенного с прямым выходом D -триггера и выходом второго одновибратора, вход которого подключен к выходу второго элемента И, являющемуся вторым выходом блока управления, вторые входы четвертого и пятого элементов И подключены к выходу второго элемента ИЛИ, входы которого являются вторым входом блока управления, а выход через первый инвертор соединен с третьим входом третьего элемента И, выход которого подключен к установочному входу D -триггера, соединенному счетным входом через седал юй элемент И с.входами задания работы, один из которых является седьмым выходом бло- . ка управления,: третьи, входы четвертого и пятого элеме1ггов И соединены соответственно с входом и выходом второго инвертора, первый, второй и третий входы третьего элемента ИЛИ подключены сосхгветственно к прямому выходу D -триг , выходам щестого и первого, элементов И, а его выход через третий одновибратор соединен с входом первого одновибратора, причем выходы третьего одновибратора, первого и пятого элементов И, первого и третьего элементов или являются соответственно первым, третьим, пятым, шестым и восьмым выходами блока управления, а юсод второго инвертора является третьим входом блока управления. Источники информации. Принятые во внимание при экспертизе 1. Корн Г., Корн Т. Электронные аналоговые и аналоговот 4ифровые вычисли9

Фиг.1 612 тельные машины. Т. 2. М., Мир, 19Ь8,. с. 141-142. 2. Патент США № 3541318, кл. 235-183, опублик. 1970. 3. Артамонов А. Б., Смирнов А. М. Функционалызпые кодирующие преобразователи на основе раэвертываюших систем. Проблемы создания преобразователей формы информации, ч. 1, Киев, Наукова :Думка, 1976, с. 14О-144, рис. 2

изм. Корр.

Фи.2

Авторы

Даты

1982-04-23—Публикация

1980-08-25—Подача