(54) УСТРОЙСТВО ДЛЯ ПОДАВЛЕНИЯ ПОМЕХ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для защиты от импульсных помех | 1983 |

|

SU1095427A1 |

| Устройство для подавления помехпРи цифРОВОй пЕРЕдАчЕ иМпульСНОйпОСлЕдОВАТЕльНОСТи | 1977 |

|

SU840745A1 |

| Цифровой фильтр | 1978 |

|

SU748803A1 |

| Устройство для подавления помех | 1985 |

|

SU1324095A1 |

| Формирователь импульсов | 1978 |

|

SU744943A1 |

| Устройство синхронизации | 1985 |

|

SU1285577A1 |

| Устройство для подавления помех | 1978 |

|

SU698128A2 |

| Устройство для воспроизведения цифровой информации с магнитной ленты | 1980 |

|

SU949792A1 |

| Электронный музыкальный звонок | 1988 |

|

SU1748176A1 |

| Двоично-десятичный счетчик | 1977 |

|

SU743206A1 |

Изобретение относится к 1 мпулъс/ной технике, в частности к формирователям импульсов с подавлением кратковременных помех, и может быть использовано в вычислительной технике и автоматике.

Известно устройство для подавления помех, содержащее два триггера, каждый из которых имеет входы.нулевой, единичный,синхронизации и раздельной установки в О, причем входы установки в о обоих триггеров объединены, вход синхронизации первого триггера является входом устройства, а единичный выход второго триггера -.выходом устройства

Однако это устройство отличается конструктивной сложностью и невысокой надежностью.

Известно также устройство для подавления помех, содержащее соединенные между собой два триггера со счетными входами 2.

Недостатком этого устройства является то, что оно подавляет кратковременные помехи только в том случае, когда управляющий сигнал имеет нулевой уровень, а при единичном уровне управляющего сигнала кратковременные импульсы помехи проходят на, выход

устройства, т.е. известное устройство подавляет помехи только одной полярности.

Целью изобретения является увеличение помехоустойчивостиустройства.

Поставленная цель достигается тем, что в устройство для подавления помех, содержащее два триггера, счетные входы которых подключены к тактовой ши10не и к входам первого и второго элементов совпадения, другие входы которых подсоединены соответственно к выходам первого и второго триггеров, вход сброса первого триггера подклю15чен к управляющей шине непосредственно а вход другого триггера - через ивертор, введены третий триггер и третий элемент совпадения, один вход которого соединен с выходом первого

20 элемента совпадения, другой вход подключен к выходу третьего триггера, а выход подключен к счетному входу третьего триггера, вход сброса которого соединен с инверсным выходом

25 второго элемента совпадения..

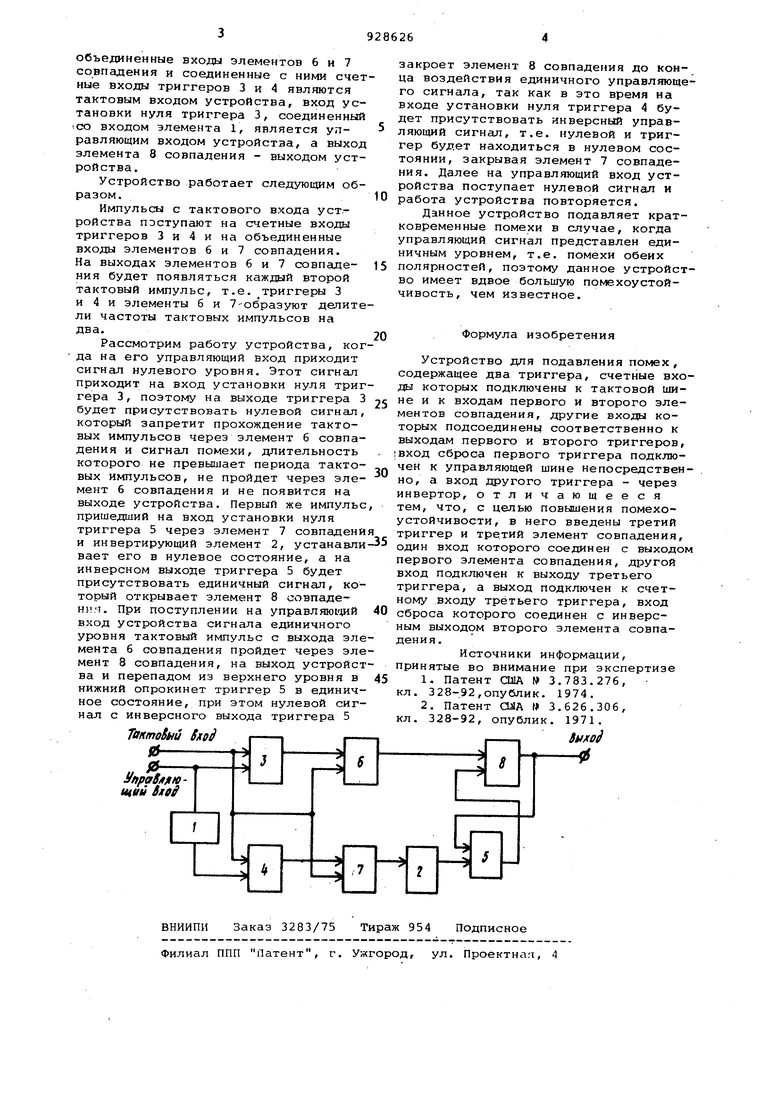

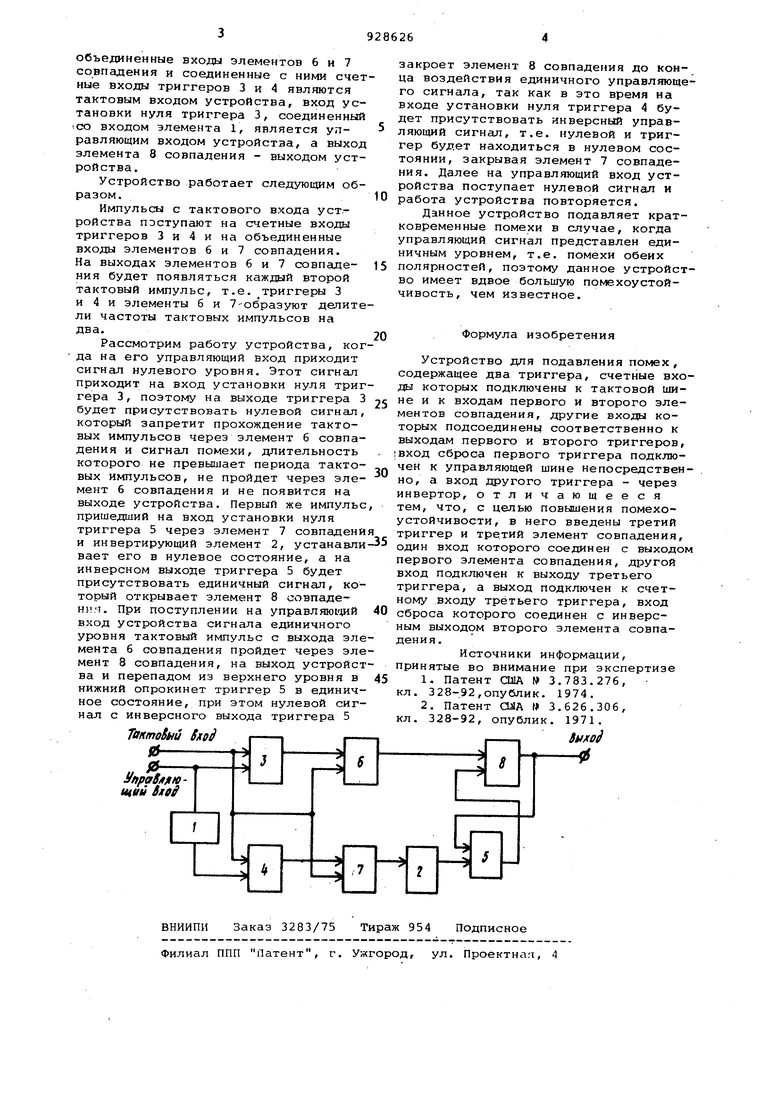

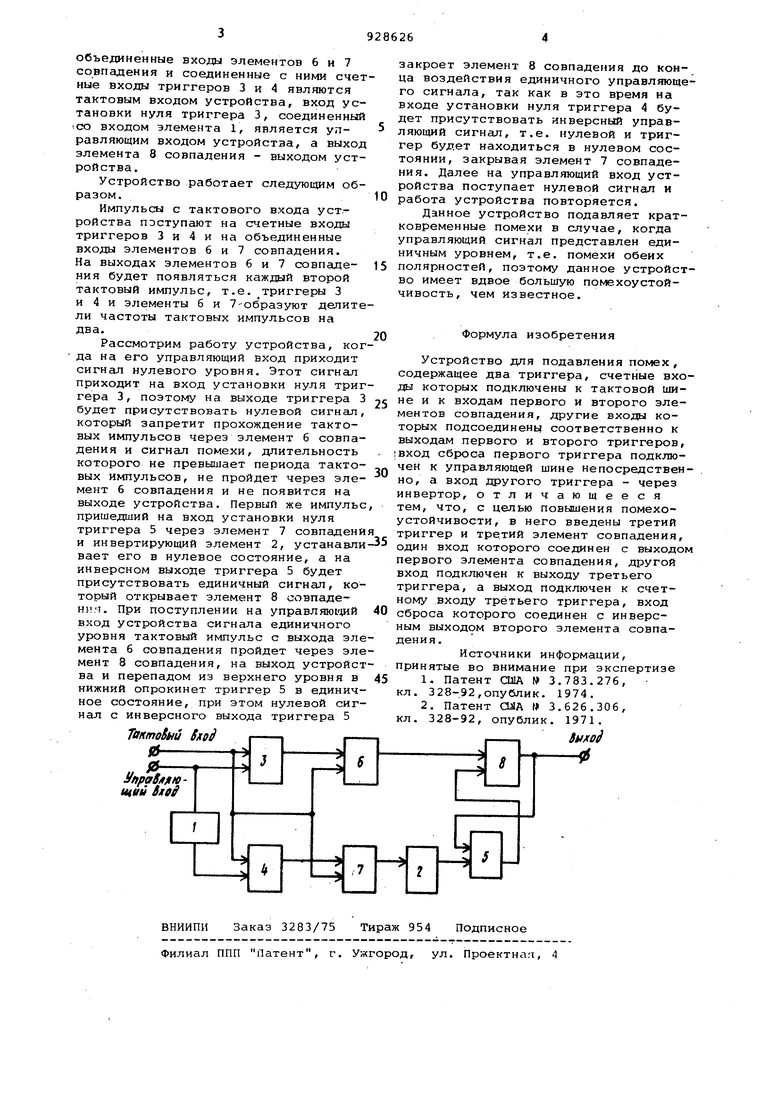

На чертеже представлена функциональная схема данного устройства.

Устройство содержит инвертирующие элементы 1 и 2, триггеры 3-5 и

30 элементы 6-8 совпадения. При этом объединенные входды элементов 6 и 7 совпадения и соединенные с ними счет ные входы триггеров 3 и 4 являются тактовым входом устройства, вход установки нуля триггера 3, соединенный .со входом элемента 1, является управляющим входом устройства, а выход элемента 8 совпадения - выходом устройства. Устройство работает следующим образом. Импульсы с тактового входа уст.ройства поступают на счетные входы триггеров 3 и 4 и на объединенные входы элементов 6 и 7 совпадения. На выходах элементов 6 и 7 совпадения будет появляться каждый второй тактовый импульс, т.е. триггеры 3 и 4 и элементы б и 7Обраэуют делите ли частоты тактовых импульсов иа два. Рассмотрим работу устройства, ког да на его управляющий вход приходит сигнал нулевого уровня. Этот сигнал приходит на вход установки нуля триг гера 3, поэтому на выходе триггера 3 будет присутствовать нулевой сигнал который запретит прохождение тактовых импульсов через элемент 6 совпадения и сигнал помехи, длительность которого не превышает периода тактовых импульсов, не пройдет через элемент 6 совпадения и не появится на выходе устройства. Первый же импульс пришедший на вход установки нуля триггера 5 через элемент 7 совпадени и инвертирующий элемент 2, устанавли вает его в нулевое состояние, а на инверсном выходе триггера 5 будет присутствовать единичный сигнал, ко торый открывает элемент 8 совпадения. При поступлении на управляю1Д1й вход устройства сигнала единичного уровня тактовый импульс с выхода эл мента 6 совпадения пройдет через эл мент 8 совпадения, на выход устройс ва и перепадом из верхнего уровня в нижний опрокинет триггер 5 в единич ное состояние, при этом нулевой сиг нал с инверсного выхода триггера 5 закроет элемент 8 совпадения до конца воздействия единичного управляющего сигнала, так как в это время на входе установки нуля триггера 4 будет присутствовать инверсный управляющий сигнал, т.е. нулевой и триггер будет находиться в нулевом состоянии, закрывая элемент 7 совпадения. Далее на управляющий вход устройства поступает нулевой сигнал и работа устройства повторяется. Данное устройство подавляет кратковременные помехи в случае, когда управляющий сигнал представлен единичным уровнем, т.е. помехи обеих полярностей, поэтому данное устройство имеет вдвое большую помехоустойчивость, чем известное. Формула изобретения Устройство для подавления помех, содержащее два триггера, счетные входы которых подключены к тактовой шине и к входам первого и второго элементов совпадения, другие входы которых подсоединены соответственно к выходам первого и второго триггеров, 1ВХОД сброса первого триггера подключен к управляющей шине непосредственно, а вход другого триггера - через инвертор, отличающееся тем, что, с целью повышения помехоустойчивости, в него введены третий триггер и тре.тий элемент совпадения, один вход которого соединен с выходом первого элемента совпадения, другой вход подключен к выходу третьего триггера, а выход подключен к счетному входу третьего триггера, вход сброса которого соединен с инверсным выходом второго элемента совпадения. Источники информации, принятые во внимание при экспертизе 1.Патент США № 3.783.276, кл. 328-92,опублик. 1974. 2.Патент ОНА № 3.626.306, кл. 328-92, опублик. 1971.

Авторы

Даты

1982-05-15—Публикация

1980-08-25—Подача