(54) УСТРОПСТВО ДЛЯ ПОДАВЛЕНИЯ ПОМЕХ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для подавления помех | 1974 |

|

SU519857A1 |

| Устройство для подавления помех | 1984 |

|

SU1203692A2 |

| Формирователь импульсов | 1979 |

|

SU839034A1 |

| Аналого-цифровой преобразователь | 1977 |

|

SU684735A1 |

| Устройство для подавления помех | 1980 |

|

SU928626A1 |

| Формирователь импульсов | 1978 |

|

SU744943A1 |

| УСТРОЙСТВО ДЛЯ БЕСКОНТАКТНОГО ИЗМЕРЕНИЯ ИМПУЛЬСНЫХ ТОКОВ | 1990 |

|

RU2024025C1 |

| Триггерное устройство | 1981 |

|

SU1003304A1 |

| Устройство для настройки и поверки импульсной электроразведочной аппаратуры | 1988 |

|

SU1679444A2 |

| Устройство для защиты от импульсных помех | 1983 |

|

SU1095427A1 |

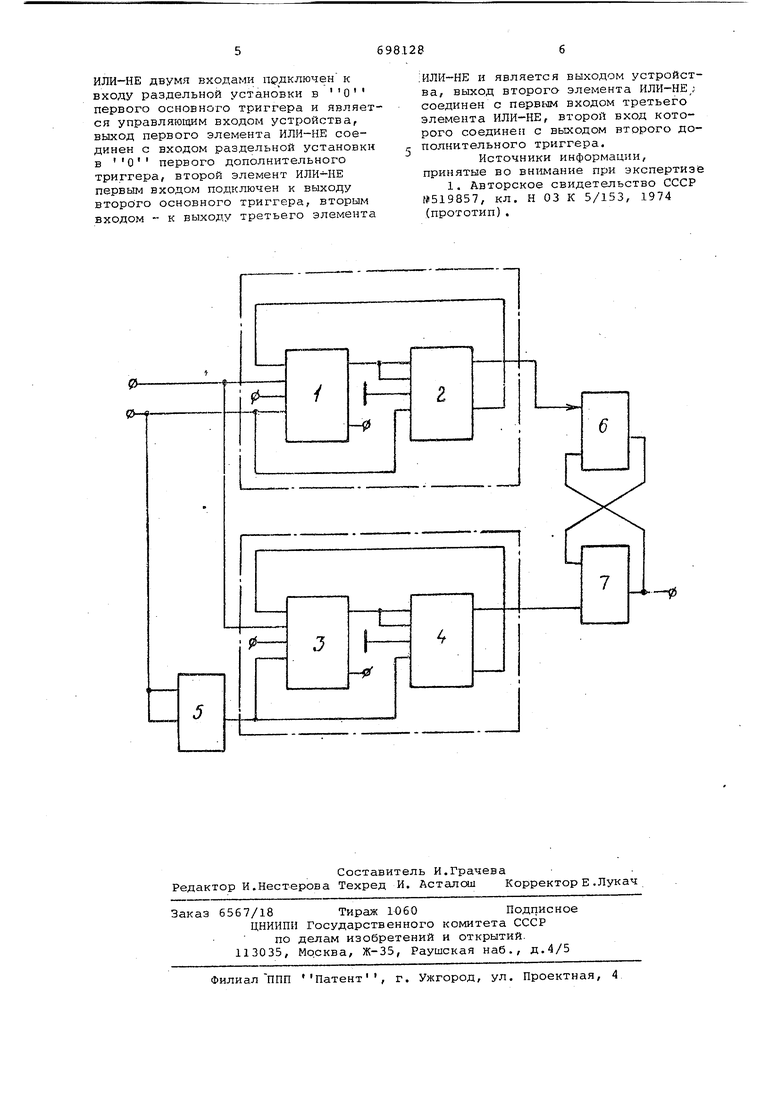

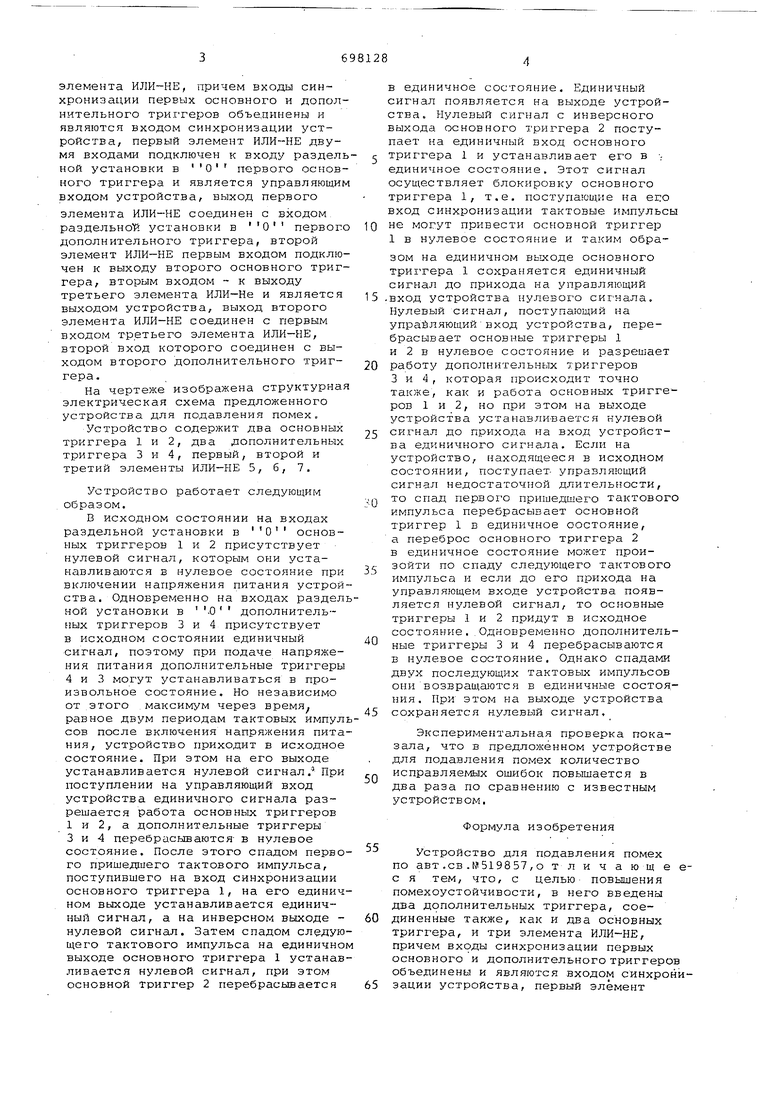

Изобретение относится к импульсн технике, в частности к формирователям импульсов с подавлением кратковременных помех и может использоват ся в вычислительной технике и автом тике , По основному авт.ев, №519857 известно устройство для подавления помех, содержащее два триггера, каждый из которых имеет выходы нуле вой, единичный, синхронизации и раз дельной установки в и выходы единичный и инверсный, причем входы раздельной установки в триггеров объединены,вход синхрониз ции первого триггера является входо устройства, единичный выход второго триггера является выходом устройства, а единичный выход первого триггера соединен с единичным входом.второго триггера, единич ный вход второго триггера объедине с его входом синхронизации, нулевой его вход заземлен, а инверсный выход соединен с единичным входом первого триггера, причем объединенные входы раздельной установки в обоих триггеров являются управляющим входом устройства 1. Однако известное устройство подавляет только кратковременные помехи положительной полярности, что снижает его помехоустойчивость. Цель изобретения - повьлиение помехоустойчивости. Для этого в устройство для подавления помех, содержащее три триггера, каждый из которых имеет выходы нулевой, единичный, синхронизации и раздельной установки в О и выходы единичный и инверсный, причем входы раздельной установки в О обоих триггеров объединены, вход синхронизации первого триггера является входом устройства, единичный выход второго триггера является вькодом устройства,а единичный выходпервого триггера соединен с единичным входом второго триггера, единичный вход второго триггера объединен с его входом синхронизации, нулевой его вход зазекшен, а инверсный выход соединен с единичным входом первого триггера, причем объединенные входы раздельной установки в О обоих триггеров являются управляющим входом устройства, введены два дополнительных триггера, соединенные также, как и два основных триггера, и три элемента ИЛИ-НЕ, причем входы синхронизации первых основного и допол нительного три.ггеров объединены и являются входом синхронизации устройства, первый элемент ИЛИ-НЕ двумя входами подключен к входу раздел ной установки в первого основ ного триггера и является управляющим входом устройства, выход первого элемента ИЛИ-НЕ соединен с входом раздельной установки в О первог дополнительного триггера, второй элемент ИЛИ-НЕ первым входом подклю чен к выходу второго основного триг гера, вторым входом - к выходу третьего элемента ИЛИ-Не и является выходом устройства, выход второго элемента ИЛИ-НЕ соединен с первым входом третьего элемента ИЛИ-НЕ, второй вход которого соединен с выходом второго дополнительного триггера. На чертеже изображена структурна электрическая схема предложенного устройства для подавления помех. Устройство содержит два основных триггера 1 и 2, два дополнительных триггера 3 и 4, первый, второй и третий элементы ИЛИ-НЕ 5, 6, 7. Устройство работает следующим образом. В исходном состоянии на входах раздельной установки в основных триггеров 1 и 2 присутствует нулевой сигнал, которым они устанавливаются в нулевое состояние при включении напряжения питания устрой ства. Одновременно на входах раздел ной установки в дополнительных триггеров 3 и 4 присутствует в исходном состоянии единичный сигнал, поэтому при подаче напряжения питания дополнительные триггеры 4 и 3 могут устанавливаться в произвольное состояние. Но независимо от этого максимум через вpeмя равное двум периодам тактовых импул сов после включения напряжения пита ния, устройство приходит в исходное состояние. При этом на его выходе устанавливается нулевой сигнал. При поступлении на управляющий вход устройства единичного сигнала разрешается работа основных триггеров 1 и 2, а дополнительные триггеры 3 и 4 перебрасываются- в нулевое состояние. После этого спадом перво го пришедшего тактового импульса, поступившего на вход синхронизации основного триггера 1, на его единич ном выходе устанавливается единичный сигнал, а на инверсном выходе нулевой сигнал. Затем спадом следую щего тактового импульса на единично выходе основного триггера 1 устанав ливается нулевой сигнал, при этом основной триггер 2 перебрасывается в единичное состояние. Единичный игнал появляется на выходе устройтва. Нулевый сигнал с инверсного ыхода основного триггера 2 поступает на единичный вход основного триггера 1 и устанавливает его в . единичное состояние. Этот сигнал осуществляет блокировку основного триггера 1, т.е. поступающие на есо вход синхронизации тактовые Рмпульсы не могут привести основной триггер 1 в нулевое состояние и таким образом на единичном выходе основного три1гера 1 сохраняется единичный сигнал до прихода на управляющий ВХОД устройства нулевого сигнала. Нулевый сигнал, поступающий на управляющий вход устройства, перебрасывает основные триггеры 1 и 2 в нулевое состояние и разрешает работу дополнительных триггеров 3 и 4 , {оторая происходит точно также, как и работа основных триггеров 1 и 2, но при этом на выходе устройства устанавливается нулевой сигнал до прихода на вход устройства единичного сигнала. Если на устройство, находящееся в исходном состоянии, поступгчет- управляющий сигнал недостаточной длительности, то спад первого пришедшего тактового импульса перебрасывает основной триггер 1 Б единичное состояние, а переброс основного триггера 2 в единичное состояние может произойти по спаду следующего тактового импульса и если до его прихода на управляющем входе устройства появляется нулевой сигнал, то основные триггеры 1 и 2 придут в исходное состояние..Одновременно дополнительные триггеры 3 и 4 перебрасываются в нулевое состояние. Однако спадаг ш двух последующих тактовых импульсов они возвращаются в единичные состояния. При этом на выходе устройства сохраняется нулевый сигнал. Экспериментальная проверка показала, что в предложенном устройстве для подавления помех количество исправляемых ошибок повышается в два раза по сравнению с известным устройством. Формула изобретения Устройство для подавления помех по авт.ев.№519857,о т л и ч а ю щ е ес я тем, что, с целью повышения помехоустойчивости, в него введены два дополнительных триггера, соединенные также, как и два основных триггера, и три элемента ИЛИ-НЕ, причем входы синхронизации первых основного и дополнительного триггеров объединены и являются входом синхронизации устройства, первый элемент

ИЛИ-НЕ двумя входами прдключен к входу раздельной установки в О первого основного триггера и является управляющим входом устройства, выход первого элемента ИЛИ-НЕ соединен с входом раздельной установки

О

первого дополнительного

триггера, второй элемент ИЛИ-НЕ первым входом подключен к выходу второго основного триггера, вторым входом к выходу третьего элемента

:ИЛИ-НЕ и является выходом устройства, выход второго элемента ИЛИ-НЕ ; соединен с первым входом третьего элемента ИЛИ-НЕ, второй вход которого соедине с выходом второго дополнительного триггера.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1979-11-15—Публикация

1978-03-16—Подача