(54) НИЗКОЧАСТОТНЫЙ ЧАСТОТОМЕР

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь частоты в напряжение | 1983 |

|

SU1117834A1 |

| Управляемый генератор гармоническихКОлЕбАНий | 1979 |

|

SU801263A1 |

| Способ измерения частоты и устройство для его осуществления | 1986 |

|

SU1467519A1 |

| Способ измерения частоты | 1988 |

|

SU1597762A1 |

| Датчик разности фаз | 1980 |

|

SU962817A1 |

| Цифровой частотомер | 2019 |

|

RU2730047C1 |

| Низкочастотный цифровой частотомер | 1980 |

|

SU924601A1 |

| Способ формирования опорных сигналов для многоканальной системы управления преобразователем частоты | 1988 |

|

SU1589355A1 |

| Широтно-импульсный преобразователь | 1986 |

|

SU1413715A1 |

| Следящая система | 1985 |

|

SU1290251A1 |

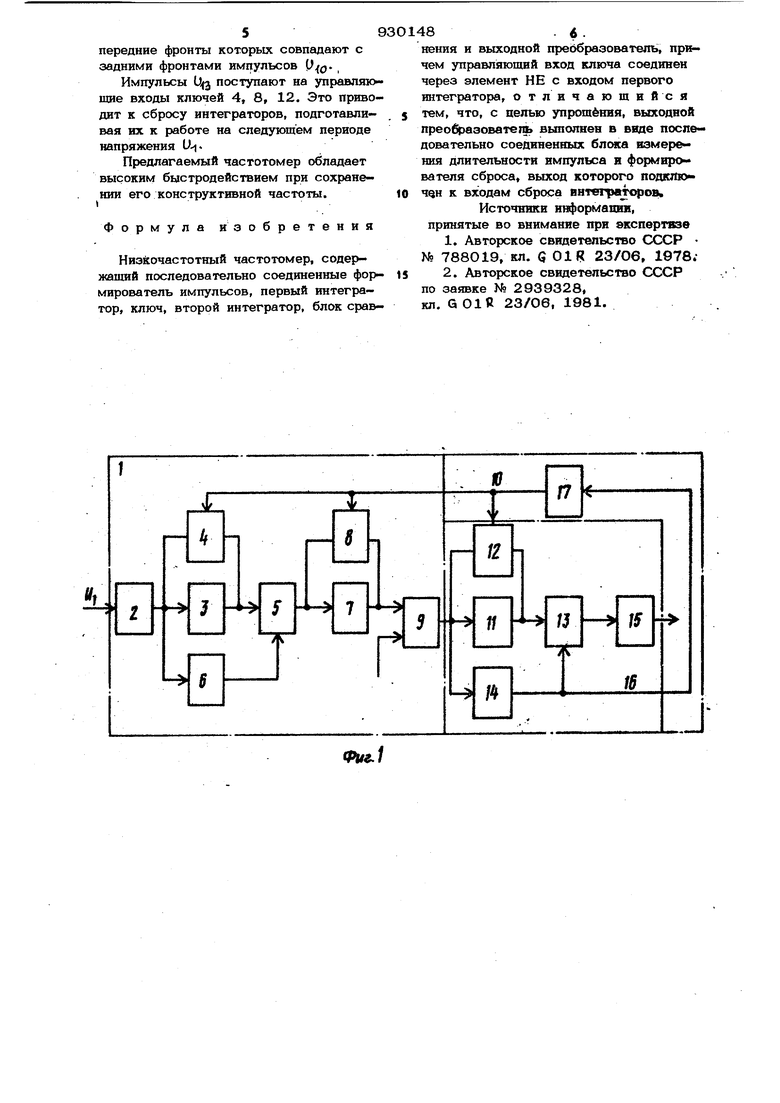

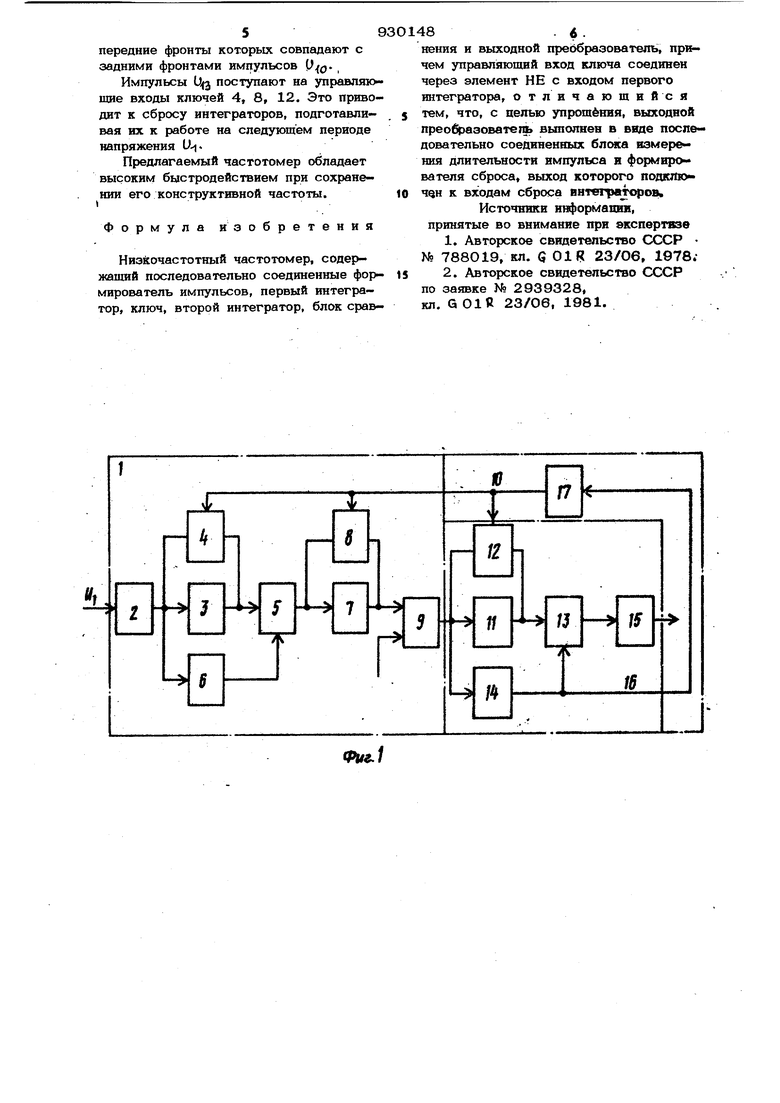

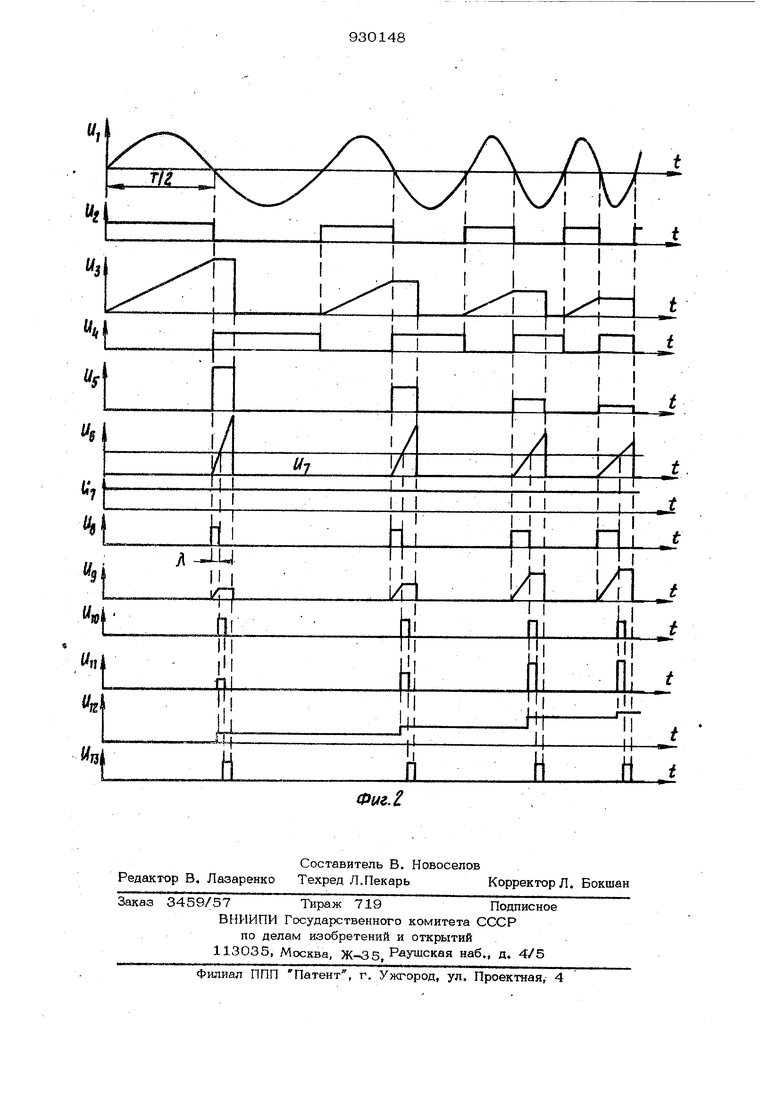

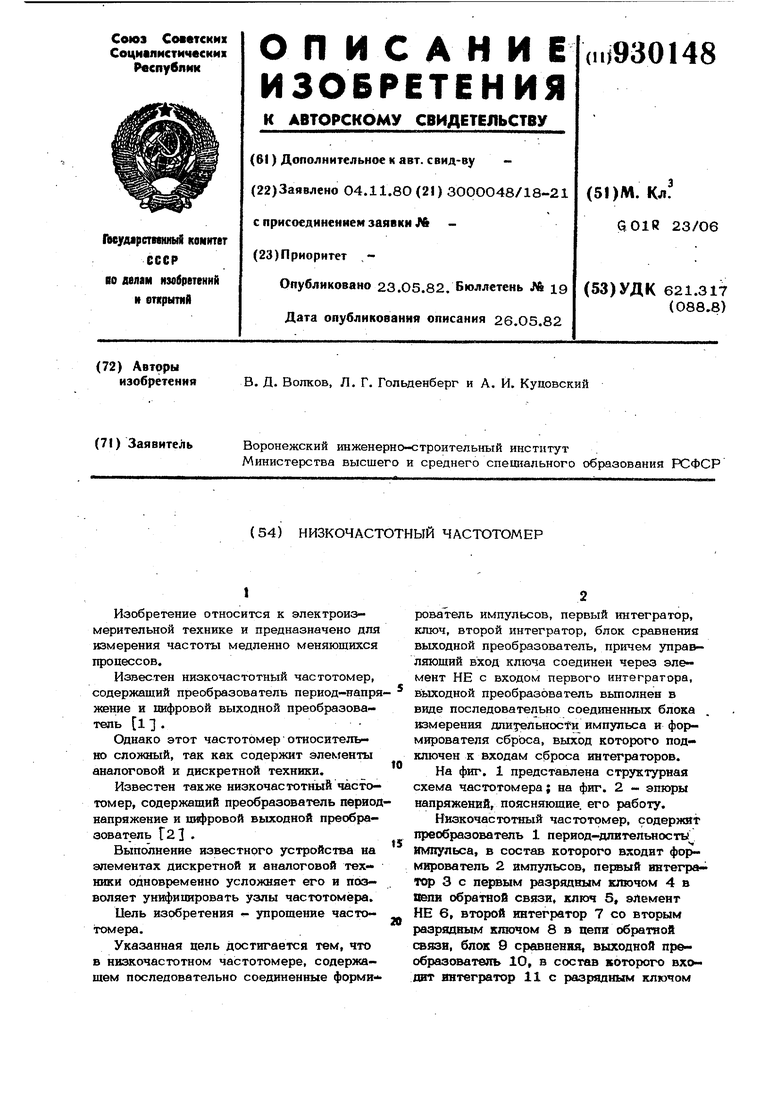

Изобретение относится к электроизмерительной технике и предназначено для измерения частоты медленно меняющихся процессов. Известен низкочастотный частотомер, содержащий преобразователь период-напря жвние и цифровой выходной преобразователь 11. Однако этот частотомер относительно спожный, так как содержит элементы аналоговой и дискретной техники. Известен также низкочастотный частотомер, содержащий преобразователь период напряжение и цифровой выходной преобразователь Г21 . Выполнение известного устройства на элементах дискретной и аналоговой техники одновременно усложняет его и позволяет унифицировать узлы частотомера. Цель изобретения - упрощение частотомера. Указанная цель достигается тем, что в низкочастотном частотомере, содержащем последовательно соединенные формирователь импульсов, первый интегратор, ключ, второй интегратор, блок сравнения выходной преобразователь, причем управляющий вход ключа соединен через элемент НЕ с входом первого интегратора, выходной преобразователь выполнен в виде последовательно соед1шенных блока измерения длиуельнос и импульса и формирователя сброса, выход которого подключен к входам сброса интеграторов. На фиг. 1 представлена структурная схема частотомера; на фиг. 2 - эпюры напряжений, поясняющие, его работу. Низкочастотный частотомер, содержит преобразователь 1 период-длительность 11Мпульса, в состав которого входит формирователь 2 импульсов, первый ввтегра тор 3 с первым разрядным ключом 4 в Пепн обратное связи, ключ 5, элемент НЕ 6, второй интегратор 7 со вторым разрядным ключом 8 в цепи обратной связи, блок 9 сравнения, выходной преобразователь 10, в состав которого входвт интегратор 11 с разрядным ключом 12 в цепи обратной связи, ключ 13, фор мирователь 14 импульсов, запоминающий .блок 15, образующие блок 16 измерения длительности импульса и формирователь 17 сброса. На фиг. 2 обозначены эпюры напрял«ений, где U - преобразуемое напряжение; Un - напряжение на выходе формирователя 2 импульсов; U-j - напряжени на выходе первого интегратора 3; пряжение на выходе элемента ,НЕ 6; с - напряжение на выходе ключа 5 ; и - напряжение на выходе второго интегратора 7; U-j- опорное напряжение Dg - напряжение на выходе блока 9 сравнения; Ug- напряжение на выходе интегратора 11; Цд - напряжение на выходе формирователя 14 импульсов; Од -напряжение на выходе ключа 13 ; напряжение на выходе запоминающего блока 15; (Ji3 - напряжение на выходе формирователя 14 импульсов. t .. Устройство работает следующим образом. Преобразуемое напряжение U {фиг. частота которого подлежит преобразованию Б постоянное напряжение, поступа ет на вход формирователя 2 (фиг. 1) импульсов, на выходе которого формируется напряжение Uf2 (фиг. 2) в виде прямоугольных импульсов постоянной амплитуды, длительности которых равны длительности интервалов положительност напряжения U- . Напряжение On посту пает на вход первого интегратора 3 (фиг. 1). На выходе первого интегратора 3 формируется напряжение U (фиг. 2 линейно изменяющееся во времени на интервале действия импульса , Таким образом, уровень напряжения U достигаемый к концу интервала положительности напряжения 0 ,пропорционален его периоду Т, т. е. обратно пропор ционален частоте . Напряжение U-j поступает на сигнальный вход ключа 4, на управляющий вход которого поступает напряжение Уд (фиг. с выхода элемента НЕ 5. Напряжение (Jj имеет вид прямоугольных импульсов, передние фронты которых совпадают с задними фронтами импульсов Uij, а задние фронты - с передними фронтами импульсов и, . т. е. длительности импулъ сов Од равны длительностям интервалов отрицательности напряжения 0 . Напряжение (JA включает ключ 4 и на его выходе форми| уется напряжение Uc (фиг. 2) 93 8 уровни в виде прямоугольных импульсов которых -равны уровням напряжения Uj , достигаемым к концам интервалов положительности напряжения 0 , передние фронты совпадают с передними фронтами импульсов 0 , а длительности определяются работой последующих элементов устройства. Напряжение 5 интегрируется вторым интегратором 7, на выходе которого формируется напряжение U/ (фиг.2), линейно изменяющееся во времени на интервале действия импульса Uj. Напряжение LLg поступает на первый вход блока 9 сравнения, на второй вход которого поступает постоянное опорное напряжение U-j (фиг. 2). На выходе блока 9 сравнения формируется напряжение VQ (фиг. 2) в виде импульсов прямоугольной формы, передние фронты которых совпадают с передними фронтами импульсов а задние - с моментами совпадения напряжений и и Таким образом, в блоке 1 происходит преобразование периода входного сигнала в длительность импульса, пропорционального частоте. Напряжение UQ интегрируется интегратором 11 блока 10, на выходе которого формируется напряжение Ug (фиг. 2), линейно изменяющееся во времени на интервале действия импульса Ug . Уровень .напряжения Ug , достигаемый к концу действия импульса OQ, пропоргшонален частоте входного сигнала. Напряжение Ug поступает на сигнальный вход второго ключа 13 (фиг. 1), на управляющий вход которого с выхода формирователя 14 (фиг. 1) поступает напряжение (фиг. 2) в виде последовательности импульсов фиксированной длительности, передние фронты которых совпадают с передними фронтами импульсов U0 . Импульсы Ц- включают ключ 13, на выходе которого формируется напряжение Цц{фиг. 2) в виде последовательности прямоугольных импульсов, длительности которых равны длительностям импульсов Цд, а уровень - величине напряжения Од , достигаемого к концам действия импульсов Ug , т. е. пропорциональны частоте преобразуемого напряжения Ц . Импульсы Цф поступают на запоминающий блок 15 (фиг. 1), где фиксируются. На выходе формирователя 17 сброса формируется напряжение (Jfj (фиг. 2) в виде последовательности прямоугольных импульсов фиксированной длительности.

передние фронты которых совпадают с задними фронтами импульсов .

Импульсы Цз поступают на управляк щие входы ключей 4, 8, 12. Это приводит к сбросу интеграторов, подготавливая их к работе на следующем периоде напряжения ЩПредлагаемый частотомер обладает высоким быстродействием при сохранении его конструктивной частоты.

Формула изобретения

Низкочастотный частотомер, содержащий последовательно соединенные фо1 мирователь импульсов, первый интегратор, ключ, второй интегратор, блок сравнения и выходной преобразователь, причем управляющий вход ключа соединен через элемент НЕ с входом первого интегратора, отличающийся тем, что, с целью упрощения, выходной прео6разоввте ь выполнен в виде последовательно соединенных блсжа взмерения длительности импульса в формиро вателя сброса, выход которого подклю 4QH к входам сброса BHTeiparc oBk

Источники информации, принятые во внимание при експертязе

кл. GOlR 23/06, 1981.

./

Авторы

Даты

1982-05-23—Публикация

1980-11-04—Подача