(54) ДАТЧИК РАЗНОСТИ ФАЗ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения коэффициента нелинейности пилообразного напряжения | 1981 |

|

SU978077A1 |

| Регулятор компенсирующего устройства | 1990 |

|

SU1721705A2 |

| Цифровой измерительный неуравновешанный мост | 1978 |

|

SU789767A1 |

| Устройство для управления вентильным преобразователем | 1983 |

|

SU1094129A1 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

| Цифровой интегрирующий вольтметр | 1983 |

|

SU1093984A2 |

| Преобразователь угла поворота вала в напряжение | 1983 |

|

SU1124360A1 |

| Устройство для определения частоты основного резонанса головки громкоговорителя | 1985 |

|

SU1415471A1 |

| Цифровой измеритель относительной разности скоростей | 1977 |

|

SU717657A1 |

| Устройство для стабилизации частоты вращения электродвигателя | 1989 |

|

SU1686681A1 |

1

Изобретение относится к фаэокзмервтельной технике и автоматике и может быть использовано при создании устройств синхронно-синфазного управления i электро- и виброприводами, противоаварийной автоматики энергосистем и т.д., требующих информацтоо о фазовся сдвиге мивду двумя периодическтоли-.: сигналами одинаковой частоты.

Известен фазометр, содержащий два усилителя-ограничителя, два усилителя-j интегратора с разрядными ключами в цепях обратных связей и блок фиксации аналогового сигнала, состоящий из двух ключей и запоминающего блока Г1 J«

Недостатком указанного устройства является зависимость напряжения, пропорционального величине разности фаз, от частоты входных сигналов. Это не позволяет применять устройство в тех случаях, когда частота входных сигналов принципиально должна изменяться, например в системах автоматического управления электро- и виброприводами

резонансных объектов, в которых нвменение частоты необходимо для поиска резонансных режнмов.

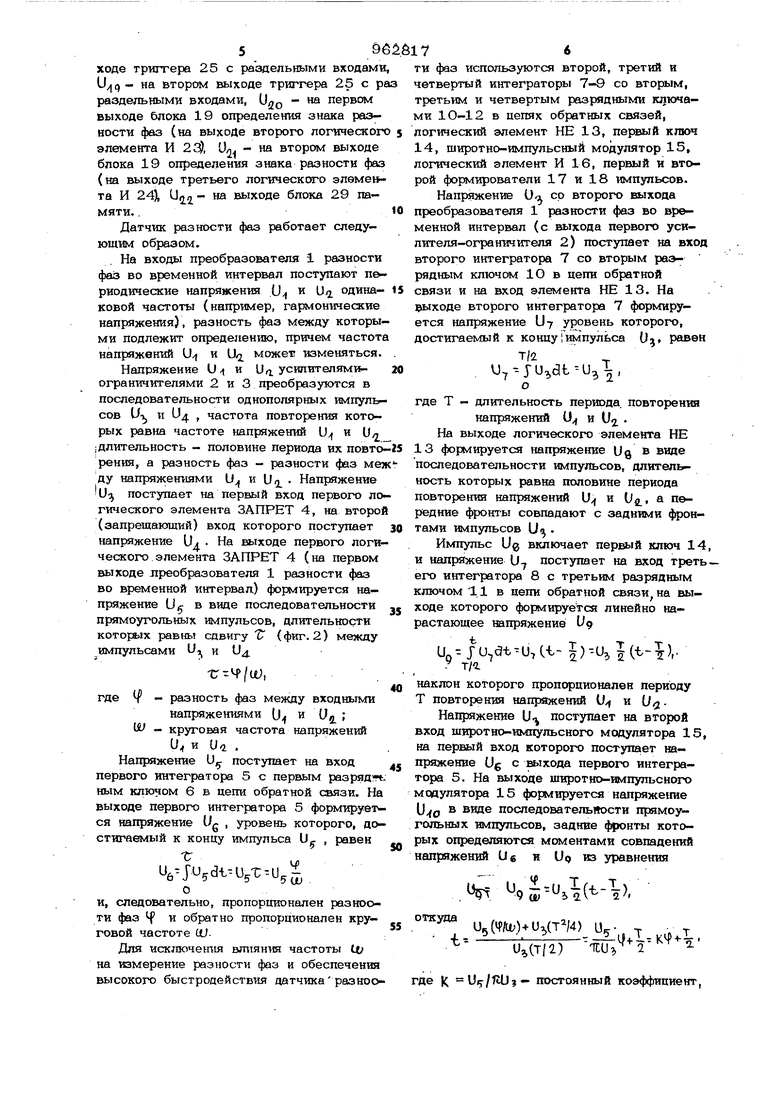

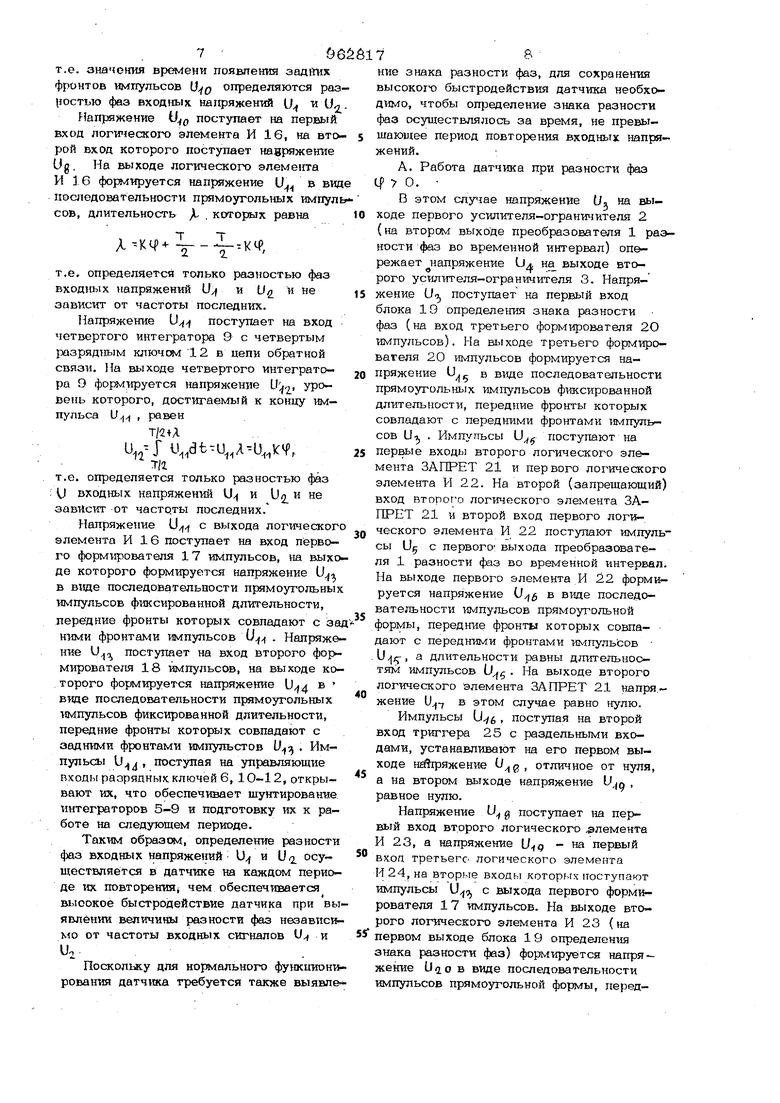

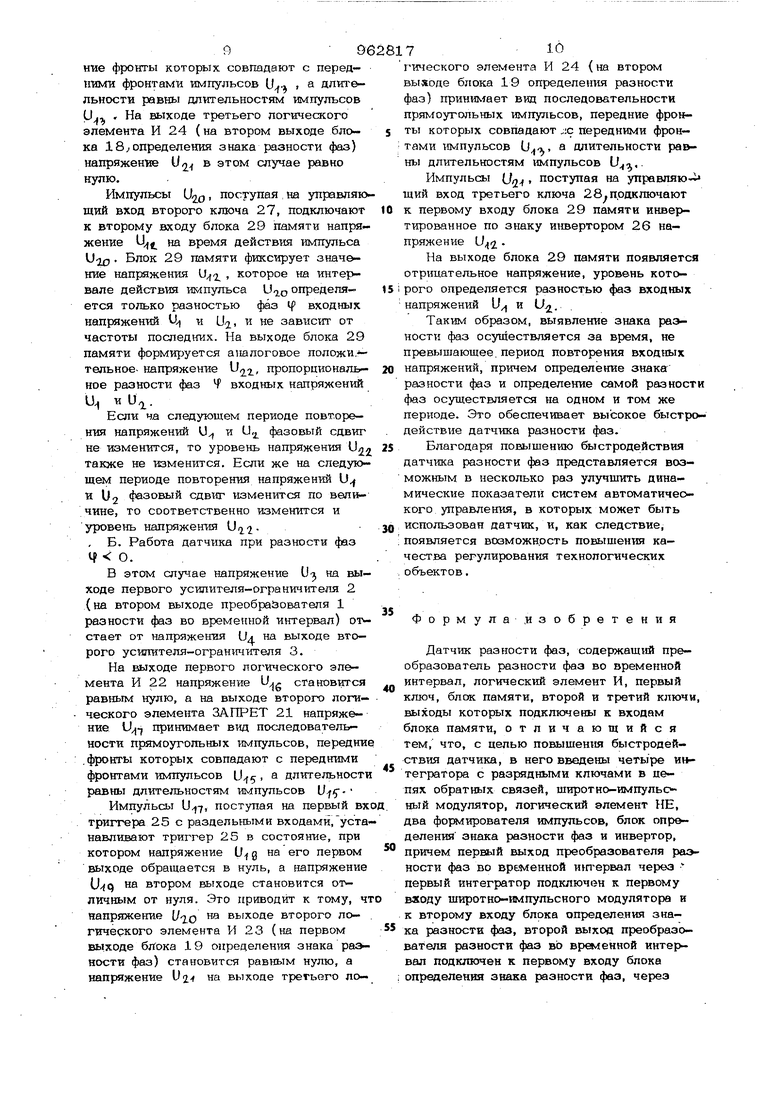

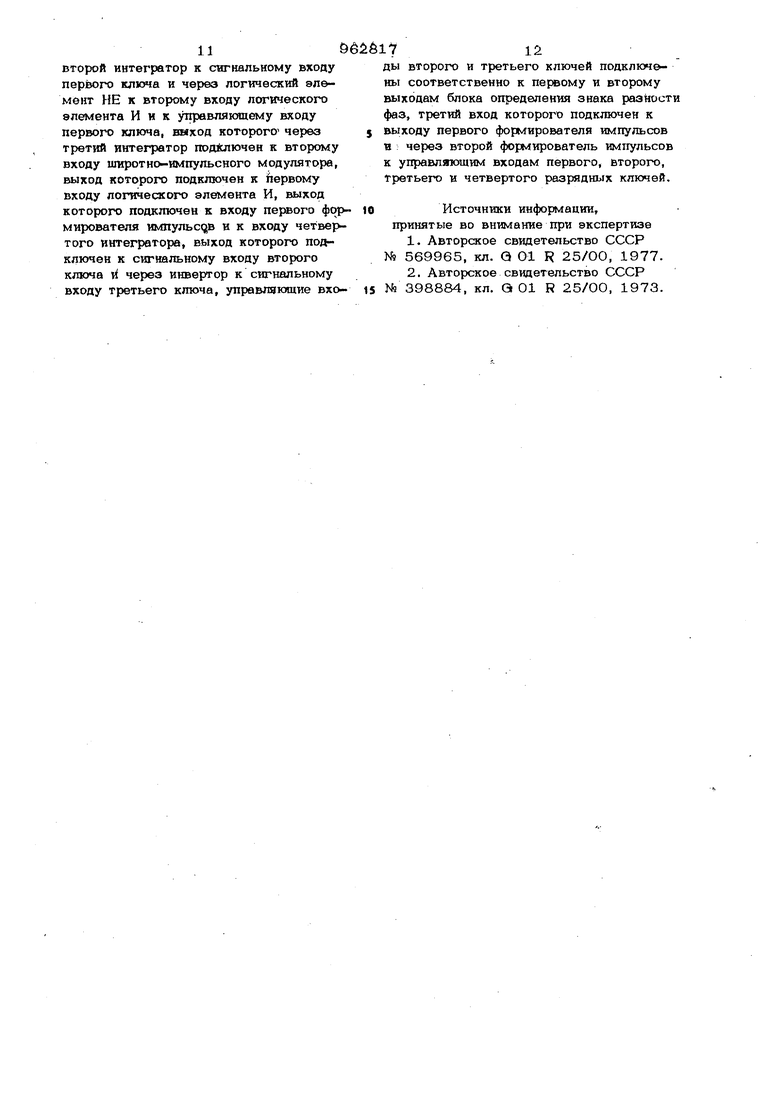

Известен также датчик разности фаз, содержащий преобразователь фаз: во временной интервал, выход которого через логический элемент соединен с родами ключей, подключенных к входам блоков памяти, загруженных на элемент ИЛИ, расщирисель импульсов, блок сирнал1хза1Ши, блок выделения среднего зна чешш и преобразователь опорного вапря жения в последовательность импульсов, вход которого соедиаен с входом устройства, а выход через блок выделения среднего значения подключен к зарядным резистором, которые подключены к входам зарядных ключей, входы расширителя импульсов подЕлккены к выходам разрядных ключей, а вход блока сигнализации подключен к выходу расширителя нмпул ссш . Известное устройство вырабатывает на выходе сигнал, пропорциональный разноств фаз двух вкодных сигналов, причем уровень этого сигнала определяется только разностью фаз и не зависит от часто ты входных сигналов 2}. Недостатком известного устройства является низкое быстродействие при формировании независящего от частоты сигнала, пропорционального разности фаз вход11Ых сигналов. Недостаток обусло&лен тем, что при формировании независящего от частоты сигнала, пропорционалького разности фаз, используется блок выделения среднего значения, содержащий выпрямитель со сглаживающим фильтрем. В таком устройстве формирование выходного сигнала, пропорционального среднему значению входного сигнала, , . осуществляется за время, равное несколь ким периодам входного сигнала; Низкое быстродействие ухудщает динамтиеские свойства датчика разности фаз, Цель изобретения повыщение быст родействия датчика. 1 Поставленная цель досткгается тем, что в датчик разности фаз, содержащий преобразователь разности фаз во временной интчервал, логический элемент И, первый ключ, блок памяти, второй и третий ключи, выходы которых подключены к входам блока памяти, введены четыре интегратора с разрядными ключами в цепях обратных связей, широтно-импульсный мо дулятор, логический элемент НЕ, два формирователя импульсов, блок определе ния знака разности фаз и инвертор, причем первый выход преобразователя-разно сти фаз во временной интервал через пер вый интегратор подключен к первому входу широтно-имлульсного модулятора и к второму вХоДу блока определения знака разности фаз, второй выход преобразователя разности фаз во временной интервал подключен к первому входу блока определения знака разности фаз, через второй интегратор ксигнальному входу первого ключа и через логический элемент НЕ к второму входу логического элемента И и к управляющему входу первого ключа, вЬ1ход которого дерев третий интегратор подключен к второму входу широтно-импульсного модулятора, выход которого подключен к первому входу логического элемента И, выход которого подктоочен к входу первого формирователя импульсов к входу четвертого интегратора, выход которого подключен к сигнальному входу второго ключа и через инвертор к сигнальному входу третьего ключа, управляющие входы второго и третьего ключе подключены соответствевйо к первому И второму выходам блока определения знака разности фаз, третий вход которого подключен к выходу первого формирователя импульсов и через втЬрой формирователь импульсов к управляющем входам первого, второго, третьего и четвертого разрядных ключей. На фиг, 1 приведена функциональная хема предлагаемого датчика i на фиг. 2 - эпюры напряжений, поясняющие его работу, Датчик разности фаз содержит преобразователь 1 разности фаз во временной интервалу состоящий из первого и второго усилителей-ограшиителей 2 и 3 и первого логического элемента ЗАПРЕТ 4, первый интегратор 5 с первым разрядным ключом 6 в цепи обратной связи, второй, третий и четвертый интеграторы 7-9 со вторым, третьим и.четвертым разрядными ключами 10-12 в цепях связей, логический элемент НЕ 1 3, первый ключ 14, широтно-импульсный модулятор 15, логический элемент И 16, первый формирователь 17 импульсов, второй формирователь 18 импульсов, блок 19 определения знака разности фаз, состоящий из третьего формирователя 20 импульсов, второго логического элемента ЗАПРЕЕТ 21, первого, второго и третьего логических элементов 22-24 и триггера 25 с раздельными входами, инвертор 26, второй ключ 27, третий ключ 28 и блок 29 памяти. На фиг, 2 обозначены напряжения: J первое входное, . - второе входное, U, на втором выходе преобразователя 1 разности фаз во временной интервал (на выходе первогч усилителя-ограничителя 2) Уд - ка выходе второго усилителя-ограничителя 3, 115- - на первсм выходе пр&образователя 1 разности фаз во временной интервал (на выходе первого логичеокого эл€мент а ЗАПРЕТ 4), Ug, - на выходе первого интегратора 5, U- - на выходе второго интегратора 7, Ug - на ходе логического элемента НЕ 13, U на выходе третьего интегратора 8, (J на выходе широтно-импульсного модулятора 15, Uif/( - на выходе логического элемента И 16, . выходе четвертого интегратора 9, , - на выходе первого формирователя 17 импульсов, Ци,на выходе второго формирователя 18 имдульсов, иа выходе третьего форм рователя 20 Импульсов, - на выходе nepBort) логического элемента И 22, Uj-, - на выходе второго логического элемента ЗАПРЕТ 21, Uxfg на первом вы ходе триггера 25 с раздельными входами - на втором выходе триггера 25 с р раздельными входами, ( - на первом выходе блока 19 определения знака разности фаз (на выходе второго логическог элемента И 22, U/j - на втором выходе блока 19 определения знака разности фаз (на выходе третьего логического элемента И 24 чч- на выходе блока 29 памяти. . Датчик разности фаз работает следующим образом. На входы преобразователя i разности фаз во временной интервал поступают п&риодические напряжения (J и U/2. одинаковой частоты (например, гармонические напряжения), разность фаз между которыми подлежит опреде;1ению, причем частота напряжений и и,2. может изменяться. Напряжение U-t и Uа Усилителямиограничителями 2 и 3 преобразуются в последовательности однополяршых импул сов U-ij и и , частота повторения которых равна частоте напряжешй U., и U/2 : длительность - половине периода их повто рения, а разность фаз - разности фаз меж ду напряженгшми U и } . Напряжение и поступает на первый вход первогю ло гического элемента ЗАПРЕТ 4, на второй (запрещающий) вход которого поступает напряжение (). . На выходе первого логического элемента ЗАПРЕТ 4 (на первом выходе лреобразователя 1 разности фаз во временной интервал) формируется напряжение (JK в виде последовательности прямоугольных импульсов, длительности которых равны сдвигу t (фиг. 2) между и, и и. импульсами -tr-4 /u;, где - разность фаз между входными напряжениями 0 и U ; 1 - круговая частота напряжений и и U/i . Напряжение U поступает на вход первого интегратора 5 с первым разряда ным ключом 6 в цепи обратной связи. На выходе первого интегратора 5 формирует ся напряжение Ug , уровень которого, до стигаемый к концу импульса U,. , равен ., и, следовательно, пропорционален разнооти фаз f и обратно пропорционален круговой частоте UJ Для исключетш влияния частоты (jj на измерение разности фаз и обеспечения высокого быстродействия датчикаразнооти фаз используются второй, третий и четвертый интеграторы 7-9 со вторым, третьим и четвертым разрядными к;Jючaми 10-12 в цепях обратных связей, логический элемент НЕ 13, первый ключ 14, широтно-импульсный модулятор 15, логический элемент И 16, первый и второй формирователи 17 и 18 импульсов. Напряжение 0. со второго выхода преобразователя 1 разности фаз во временной интервал (с выхода первого усилителя-ограничителя 2) поступает на вход второго интегратора 7 со вторым разрядным ключом 1О в цепи обратной связи и на вход элемента НЕ 13. На выходе второго интегратора 7 формируется напряжение U7 уровень которого, достигаемый к концу 1 импульса О равен Т/2 . и --уи аь--и 1, где Т - длительность периода, повторения напряжений U и Uj. На выходе логического элемента НЕ 13 формируется напряжение UQ в виде последовательности импульсов, длнтел1 ность которых равна половине периода повторения напряжений U и {), а передние (фронты совпадают с задними фронтами импульсов U- . Импульс U0 включает первый ключ 14, и напряжение О-, поступает на вход третьего интегратора 8 с третьим разрядным ключом 11 в цепи обратной связи, на выходе которого формируемся линейно нарастающее напряжение д UQ-- ,Ct- i)--U3|(t-),. наклон которого пропорционален периоду Т повторения напряжений U/j и U/j Напряжение Ua поступает на второй вход широтно-импульсного модулятора 15, на первый вход которого поступает напряжение Ug с в 1хода первого интегратора 5. На выходе щиротно-импутшсного модулятора 15 формируется напряже1гае ( в виде последовательйости прямоугольных импульсов, задние ( которых определяются моментами совпадений напряжений Ue и UQ из уравнения .(-1. откуда , где К постоянный коэффициент, Т.е. значения времени появления aaafrtix фронтов импульсов определяются раз {юстьго фаз входных напряжений (J -i Яап етжение U поступает на первый вход логического элемента И 16, на второй вход которого поступает надряжение Ug. На выходе логического элемента И 16 формируется напряжение U в вид последовательности прямоугольных импул сов, длительность Д. . которых равна , т,е. определяется только разностью фаз входных напряжений и U и не зависит от частоты последних. Напряжение U поступает на вход четвертого интегратора 9 с четвертым разрядным ключотл 12 в цепи обратной связи. На выходе четвертого интегратора 9 формируется напряжение U, уровень которого, достигаемый к концу импульса и , равен т/2а и,,-1 ц,аь-ц,д-и,,1с,: т.е. определяется только разностью ; и входных напряжений U.( и Ug и зависит от частоты последних. Напряжение U/) с выхода логическог элемента И 16 поступает на вход первого формирователя 17 импульсов, }ш выхо де которого формируется напряжение в ввде последовательности прямоугольны импульсов фиксированной длительности, передние фронты которых совпадают с за ними фронтами импульсов U . Напряже ние и.л поступает на вход второго формирователя 18 импульсов, на выходе ко торого формируется напряжение U виде последовательности прямоугольных 1мпульсов фиксированной длительности, передние фронты которых совпадают с задними фронтами импупьстов U . Импупьсы U / , поступая на управляющие входы разрядных ключей 6, 10-12, открывают их, что обеспечивает шунтирование интеграторов 5-9 и подготовку их к работе на следующем периоде. Таким образом, определение разности (})аз входных напряжений U и . осуществляется в датчике на каждом перио де их повторения чем обеспечивается высокое быстродействие датчика при вы явлении величины разности фаз независи мо от частоты входных сигналов U и Поскольку для нормального функциони рования датчика требуется также выявле ние знака разности фаз, для сохранения высокогмэ быстродействия датчика необходимо, чтобы определение знака разности фаз осуществлялось за время, не превышающее период повторения входных напряжений. А. Работа датчика при разности фаз О. В этом случае напряжение U, на выходе первого усилителя-ограничителя 2 (на вторсм выходе преобразователя 1 разности фаз во временной интервал) опережает напряжение А на выходе второго усилтгтеля-ограничителя 3. Напря- укение U-j, поступает на первый вход блока 19 определе гая знака разности фаз (на вход третьего формирователя 2О импульсов). На выходе третьего формирователя 20 импульсов формируется напряжение в ввде последовательности прямоугольных импульсов фиксированной длительности, передние фронты которых совпадают с передними фронтами импульсов UT, . Импупьсы и поступают на первые входы второго логического элемента ЗАПРЕТ 21 и первого логического элемента И 22. На второй (запрещающий) вход второго логического элемента ЗАПРЕТ 21 и второй вход первого логического элемента И 22 поступают импульсы и с первого выхода преобразователя 1 разности фаз во временной интервал. На выходе первого элемента И 22 формируется напряжение (J/jf, в виде последовательности импульсов прямоугольной формы, передние фронты которых совпа- дают с передними фронтами импульсов ., а длительности равны длительностям импульсов На выходе второго логического элемента ЗАПРЕТ 21 напря.жение в этом случае равно нулю. Импульсы . поступая на второй вход триггера 25 с раздельными входами, устанавливают на его первом выходе н фяжение ( , отличное от нуля, а на втором выходе напряжение U, равное нулю. Напряжение U g поступает на первый вход второго логического элемента И 23, а напряжение U, - на первый вход третьего логического элемента И 24, на вторые входы котормк поступают импульсы и,, с выхода первого форм№рователя 17 импульсов. На выходе второго логического элемента И 23 (на первом выходе блока 1 9 определения знака разности фаз) формируется напряженке и 2. о в виде последовательности импульсов прямоугольной формы, передние фронты которых совпадают с передними фронтами импульсов ( , а длт-ельности равны длительностям импульсов (J.- . На выходе третьего логического элемента И 24 (на втором выходе блока 18 определения знака разности фаз) напряжение в этом случае равно нулю. Импульсы , поступая . на управляю щий вход второго ключа 27, подключают к второму входу блока 29 памяти напряжение Ujj на время действия импульса (J2fj . Блок 29 памяти фиксирует знач&ние напряжения U, . которое на интернвале действия импульса определяется только разностью фаз if входных напряжений Ц и U/2., и не зависит от частоты последних. На выходе блока 29 памяти формируется аналоговое положи. тельное- напряжение i, пропорциональное разности фаз Ч входных напряжений Ц ии. Если ча следующем периоде повторения напряжений U и U. фазовый сдвиг не изменится, то уровень напряжения (/2. также не изменится. Если же на следующем периоде повторения напряжений U и U2 фазовый сдвиг изменится по величине, то соответственно изменится и уровень напряжения U,2.2Б. Работа датчика при разности фаз If О. В этом случае напряжение U-j на выходе первого усилителя-ограничителя 2 (на втором выходе преобразователя 1 разности фаз во временной интервал) от- стает от напряжения (.Ь на выходе второго усипителя-ограничителя 3. На выходе первого логического элемента И 22 напряжение становится равным нулю, а на выходе второго логического элемента ЗАПРЕТ 21 напряжение принимает вид последовательности прямоугольных импульсов, передни .фронты которых совпадают с передними фронтами импульсов длительности равны длительностям импульсов U fИмпульсы поступая на первый вх триггера 25 с раздельными входами,уста навливают триггер 25 в состояние, при котором напряжение (J g на его первом выходе обращается в нуль, а напряжение на втором выходе становится отличным от нуля. Это приводит к тому, ч напряжение L/io выходе второго логического элемента И 23 (на первом вьтходе блока 19 определения знака разности фаз) становится равным нулю, а напряжение Ui на выходе третьего логического элемента И 24 (на втором выходе блока 19 определения разности фаз) npHHWvraeT вид последовательности прямоугольных импульсов, передние фронты которых совпадают .;с передними фронтами импульсов и, а длительности равны длительностям импульсов U.a,. Импульсы (J,ji-f поступая на управляю- ший вход третьего ключа 28 подключают к первому входу блока 29 памяти инвер тированное по знаку инвертором 26 напряжениеНа выходе блока 29 памяти появляется отрицательное напряжение, уровень которого определяется разностью фаз входных напряжений U и (J. Таким образом, выявление знака разности фаз осуществляется за время, не превышающее, период повторения входных напряжений, причем определение знака разности фаз и определение самой разности фаз осуществляется на одном и том же периоде. Это обеспечивает высокое быстродействие датчика разности фаз. Благодаря повыщеншо быстродействия датчика разности фаз представляется возможным в несколько раз улучщить динамические показатели систем автоматического управления, в которых может быть использован датчик, и, как следствие, появляется возможность повыщения качества регулирования технологических объектов, Формулаизобретения Датчик разности фаз, содержащий преобразователь разности фаз во временной интервал, логический элемент И, первый ключ, блок памяти, второй и третий ключи, выходы которых подключены к входам блока памяти, отличающийся тем, что, с целью повыщения быстродействия датчика, в него введены четыре интегратора с разрядными ключами в цепях обратных связей, щиротно-импульоный модулятор, логический элемент НЕ, два формирователя импульсов, блок определения знака разности фаз и инвертор, причем первый выход преобразователя раэкости фаз во временной ишервал через первый интегратор подключен к первому вжоду щиротно-импульсного модулятора и к второму входу блока определения знака разности фаз, второй выхоа преобразователя разности фаз во временной интервал подключен к первому входу блока определения знака разности фаз, через

второй интегратор к сигнальному входу первого ключа и через логический элемент НЕ к второму входу логического элемента И и к управляющему входу первого ключа, внход которого через третий интегратор подйлючен к второму входу широтно-импульсного модулятора, выход которого подключен к первому входу логического элемента И, выход которого подключен к входу первого формирователя импульс9В и к входу четвертого интегратора, выход которого подключен к сигнальному входу второго ключа vi через инвертор к сигнальному входу третьего ключа, управляющие входы второго и третьего ключей подключ&ны соответственно к первому и второму выходам блока определения знака разности фаз, третий вход которого подключен к выходу первого формирователя импульсов и через второй формирователь импульсов к управляпощим входам первого, второго, третьего и четвертого разрядных ключей.

Источники информации, принятые во внимание при экспертизе

№ 569965, кл. Q 01 R 25/00, 1977.

hfc 398884, кл. Q 01 R 25/00, 1973.

1 J It t I i w. ) I Л- : .Il 1/.1 l I n I I3D i HI I П I i 1 y1 1X4 } Фаё. t&l 1П j II

Авторы

Даты

1982-09-30—Публикация

1980-06-11—Подача