(54) U-ТРИГГЕР

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выделения одиночного импульса | 1984 |

|

SU1182651A1 |

| Д-триггер | 1985 |

|

SU1264312A1 |

| Двоично-десятичный счетчик в коде 8-4-2-1 | 1985 |

|

SU1272504A1 |

| Д- @ триггер | 1982 |

|

SU1022299A1 |

| Устройство для задержки импульсов | 1980 |

|

SU921067A1 |

| Двоично-десятичный счетчик в коде 8-4-2-1 | 1986 |

|

SU1415439A1 |

| Двоично-десятичный счетчик вКОдЕ 8-4-2-1 | 1979 |

|

SU849498A1 |

| Дискретный уровнемер | 1986 |

|

SU1477046A1 |

| Устройство для выделения импульса | 1985 |

|

SU1272489A1 |

| Распределитель сигналов на десять каналов | 1986 |

|

SU1325683A1 |

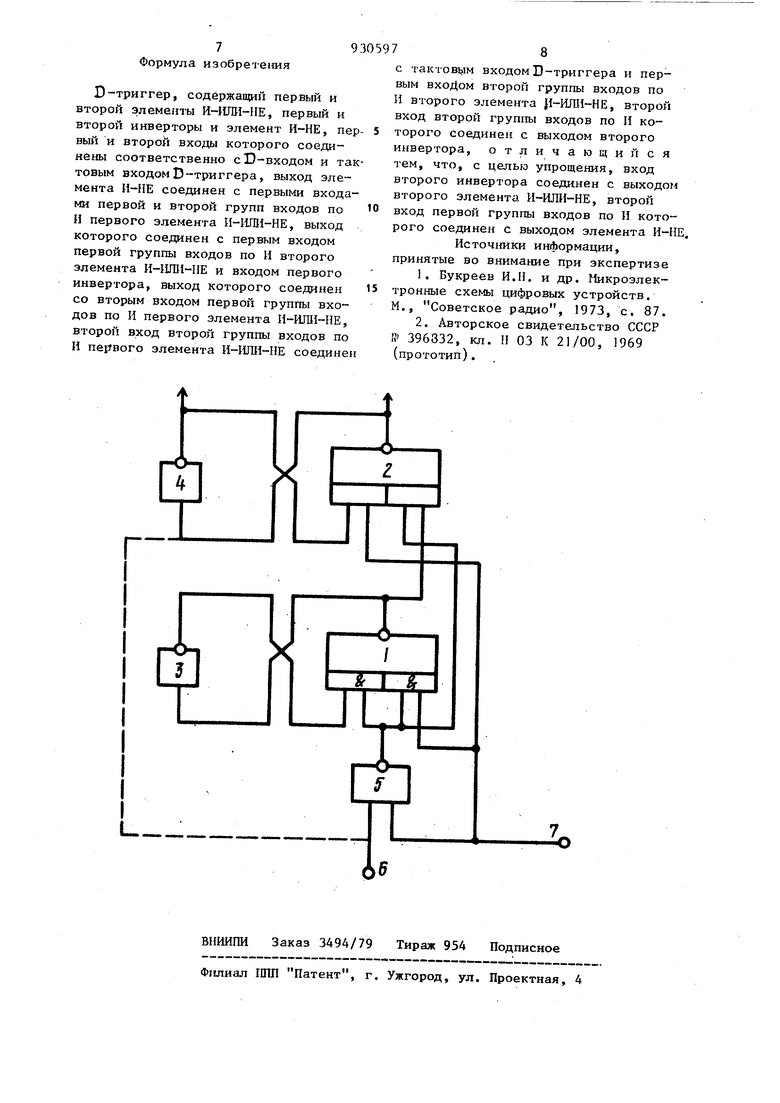

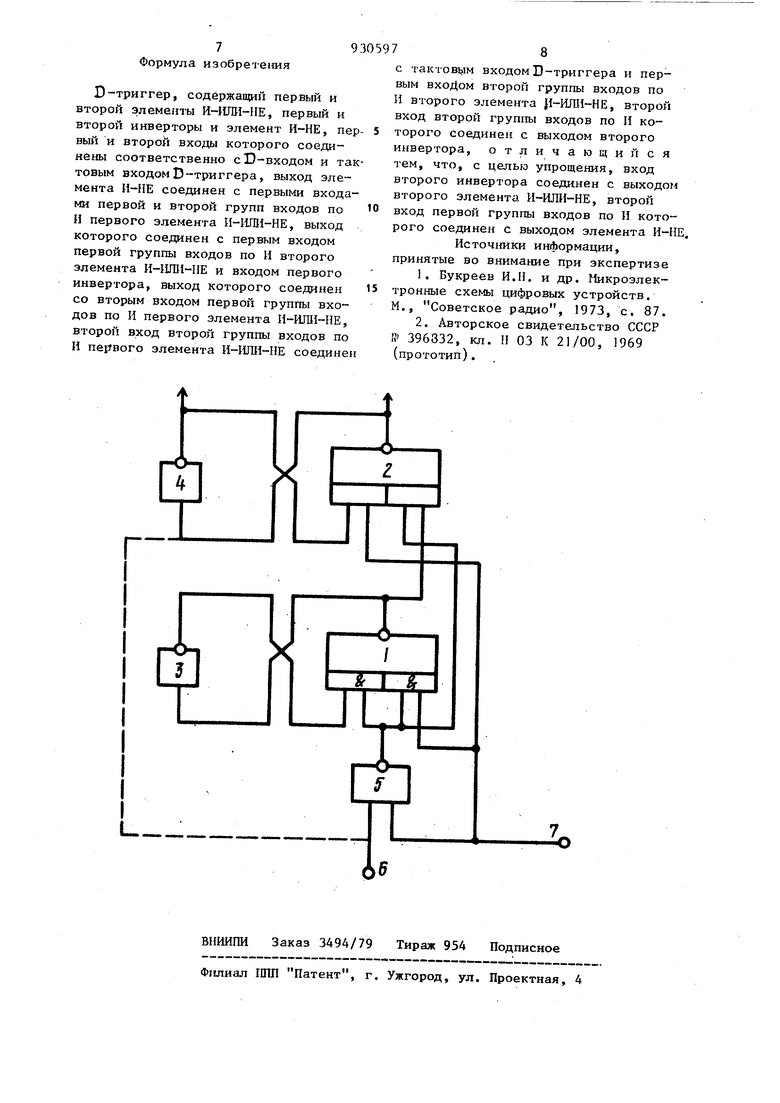

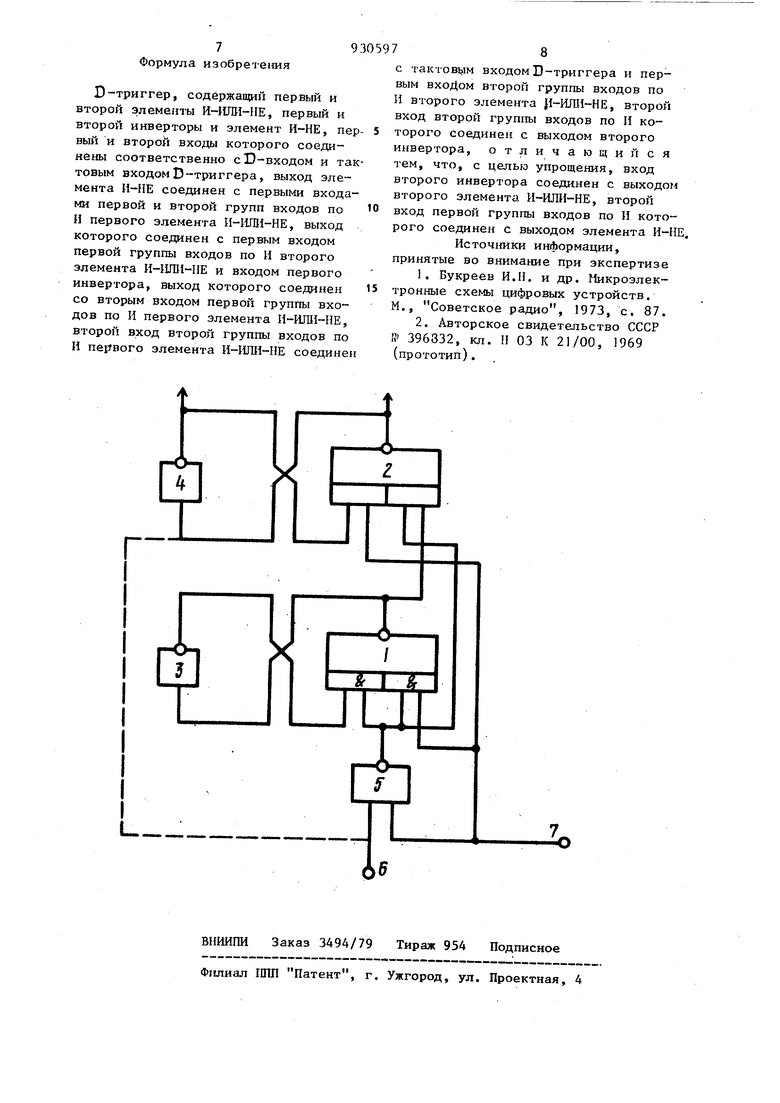

Изобретение относится к импульсной и вычислительной технике и может быть использовано при построении различных устройств дискретной обработки информации на схемах с иепосредственньПШ связями. Известен D-триггер, содержащий ос новной триггер на элементе 2И-2ШШ-Н и инверторе, через который выход эле мента 2И-2ИЛИ- 1Е основного триггера соединен с первым входом первого вхо да И элемента 2И-2ИЛИ-НЕ основного триггера, и вспомогательньв триггер на двух элементах И-ИЛИ-НЕ Ll Однако этот D-триггер имеет сложную схему и обладает узкими функциональными возможностями: информационный вход D подключается непосредственно к основному триггеру, что не дает возможности получения широкого класса входных логических функций, кроме того, при включении обратной связи с выхода вспомогательного триг гера на вход О, в D-триггере не обеспечивается устойчивого режима счета. Известен также О-триггер, содержащий первьпТс и второй элементы И-1ШИ-НЕ, первый и второй инверторы и элемент И-ПЕ, первьп и второй входы которого соединены соответственно с D-BXO- дом и тaктoвы входом D-триггера, выход элемента И-ИЕ соединен с первыми входами первой и второй групп входов по И первого элемента И-1ШИ-11Е, выход которого соединен с первым входом первой группы входов по И второго элемента И-ИЛИ-НЕ с входом первого инвертора, выход которого соединен со вторым входом первой группы входов по И первого элемента И-ИЛИ-НЕ, второй вход второй группы входов поИ первого элемента И-ИЛИ-НЕ соединен с такТовым входом D-триггера и первым входом второй группы входов по И второго элемента И-ИШ1-НЕ, второй вход второй группы входов по И ксГгорого соединен с выходом второго инвертора 2j. 3ч Недостатком этого О-трип ера najrH ется его относительно большая сложность. Целью изобретения является упроще ние О-трипера, Поставленная цель достигается тем что в D-триггере, содержащем первый и второй элементы И-11ПИ-11Е, первый и второй инверторы и элемент И-НЕ, первый и второй входы которого соеди нены соответственно с D-входом и так товым входом D-триггера, выход элемента Н-НЕ соединен с первыми входами первой и второй групп входов по Н первого элемента И-11ПИ-НЕ, выход которого- соединен с первым входом первой группы входов по И второго эл мента И-1ШИ-ИЕ и входом первого инвертора, выход которого соединен со вторым входом первой группы входов по И первого элемента НЧШИ-ИЕ, IJTOрой вход второй группы входов по И первого элемента И-ИЛИ-НЕ соединен с тактовым входом О-триггера и первым входом второй группы входов по И-второго элемента Н-ИЛИ-НЕ, второй вход второй группы входов по Н которого соединен с выходом второго инвертора, вход второго инвертора соединен с выходом второго элемента И-1ШН-11Е, второй вход первой группы входов по И которого соединен с выходом элемента Н-НЕ, На чертеже покаэана структурная схема D-триггера. D-триггер содержит первый 1 и вто рой 2 элементы ИЧ-ШИ-НЕ, первьШ 3 и второй 4 инверторы и элемент И-НЕ первый и второй входы которого соеди iteifbt соответственно с D-входом 6 и тактовым входом 7 D-триггера, выход элемента И-НЕ 5 соединен с первыми входами первой и второй групп ВНРДОВ по И первого элемента И-ИЛИ-НЕ I, выход которого соединен с первым вхо дом первой группы входов по И второго элемента И-ИЛИ-НЕ 2 и входом первого инвертора 3, выход которого сое динен со вторым входом первой группы входов по и первого элемента ИИЛИ-ПЕ 1, соединен с тактовым входом 7 D-триггера и первым входом вто рой группы входов по И второго элемента И-ИЛН-ИЕ 2, второй вход второй группы входов по И которого соединен с выходом второго инвертора 4, а вход второго инвертора 4 соединен с выходом второго элемента И-ШШ-НЕ второй вход первой группы входов по И которого соединен с выходом элемента И-ИЕ 5. D-триггер работает следующим образом. Предполохсим, что перед подачей тактового импульса на входе 6 присутствует низкий логический сигнал. Это вызовет высокий логический потенциал на выходе входного логического элемента 5, Допустим, что на выходе элемента И-ИЛИ-НЕ присутствует единичный (высокий) логический сигнал. Тогда на выходе инвертора 3 оказывается низкий логически сигнал, подтверждающий высокий логический выходной сигнал на элементе И-ИЛИ-НЕ I, В этом случае на обоих входах элемента И-ШШ-НЕ 2 оказываются единичные логические сигналы и на выходе этого элемента формируется низкий логический уровень, вызывающий появление высокого логического сигнала на выходе инвертора 4, Пусть в момент t начинается положительный тактовый импульс. При этом на обоих входах элемента И-ИЛИНЕ 1 оказываются высокие логические сигналы. Вследствие этого на его выходе формируется 1ШЗКИЙ логический сигнал, а потом - высокий логический сигнал на выходе инвертора 3, Поскольку на входе 6 присутствует нулевой логический сигнал, а на входах элемента И-ИЛИ-НЕ 2 присутствуют оба высоких логических сигнала, других изменений потенциалов на составных частях D-триггера в моме1 т t, не проис5содит. По окончании тактового импульса t, на входах элемента И-ИЛИ-НЕ 2 оказывается низкий логический сигнал. В результате этого на выходе элемента И-ИЛИ-НЕ 2 формируется единичный логический сигнал, после чего на выходе инвертора 4 появляется низкий логический сигнал. Поскольку на входе 6 присутствует нулевой логический потенциал, а на входах элемента И-ИЛИНЕ Г оба единичных логических сигнала, других изменений потенциалов на составных частях D-триггера в момент tj не происходит. Если к моменту tj начала следу1лцего тактового импульса логический сигнал на входе 6 останется нулевым, то тактовый импульс не мопет изменить выходные сигналы составных частей D-триггера. Действительно, высокий логический сигнал на выходе входного логического элемента 5 лоддёр хи вается низким логическим сигналом на входе 6; низкий логический сигнал на выходе элемента И-Ш1И-11Е 1 подцерот вается высокими логическими сигналами lia двух входах - с выхода входного логического элемента 5 и с выхода инвертора 3, высокий логический сигнал на.выходе инвертора 3 поддерживается низким сигналом на его входе - с выхода элемента И-11ГШ-ЯЕ 1. высокий логачеслсий сигнал на выходе элемента И-ИЛ11-ИЕ 2 поддер кивается вследствие того, что на одном из вхо дов присутствует нулевой логический сигнал - с выхода элемента И-НЛИ-НЕ и с выхода инвертора 4. Низкий логический сигнал на выходе инвертора 4 поддерживается высоким логическим потенциалом на его входе - с выхода элемента H-IUBI-IfE 2, Предполохшм, что после окончания тактового импульса . логический сиг нал на входе 6 изменяется с нулевого на единичный. Тогда при поступлении следующего тактового импульса t на обоих входах входного логического эл мента 5 оказываются высокие логические уровни, и его выходной логический сигнал становится нулевым. После этого на одном из входов элемента И-11Л11ИЕ I появляется нулевой логический сигнал, а на его выходе формируется еди1шчный логический сигнал, которьп устанавливается на выходе инвертора 3 низкий логический сигнал. Поскольку на обоих входах элемента И-11Ш1НЕ 2 присутствуют высокие логические сигналы, других измененш потенщгалов на составных частях О-триггера с задерж кой в момент 5 не происходит. По окончании тактового импульса t на выходе логического элемента 5 формируется высокий логический сигнал. После этого па обоих входах элемента П-ИЛИ-НЕ 2 оказываются высокие логические сигналы. Таким образом, на вы ходе этого элемента формируется низкий сигнал, который устанавливает высокий логический сигнал на выходе инвертора 4. Поскольку на одном из входов элемента Н-1ШИ-НЕ 1 присутствует низкий логический сигнал, других изменений.потенциалов на составных частях D-триггера не происходит. Если к моменту t начала следующего так1ового импульса логический сигнап на в:соде 6 останется единичladM, то нп обоих входах логического элемента 5 и элемента Н-1111Н-ИЕ 1 оказываются единичные логические сигналы. Вследствие этого на выходе элемента H-UFHi-HE 1 и на . выходе логического элемента 5 форьтруются низкие логические сигналы. Низкий логический сигнал с выхода элемента H-UJBi-HE 1 формирует высокий сигнал на выходе инвертора 3. Поскольку на элементе И-ИЛИ-НЕ 2 присутствуют два высоких логических сигнала (с выхода инвертора 4 и тактовый импульс) в момент t сигналы на выходах измениться не могут. Однако, по окончании(формирования низкого логического сигнала на выходе входного логического элемента 5 на одном из входов элемента И-1ШИ-НЕ I оказывается низкий логический сигнал. Таким образом, на выходеитого элемента вновь формируются высокие логические сигналы. Высокий логический сигнал с выхода элемента И-ЛЛИ-НЕ 2 устанавливает низкий логический сигнал на выходе инвертора 4. Поскольку на одном из входов элемента И-ИЛИНЕ 1 в момент tg присутствуют низкие логические сигналы (с выхода инвертора 3 и со входа тактовых импульсов 7), в момент trt сигналы на триггере не меняются. После формирования высокого логического сигнала на выходе логического элемента 5, на входах элемента И-ИЛИ-НЕ 2 оказываются высокие логические сигналы. Это вызывает появление на ее выходе низкого логического сигнала, который формирует высокий логичес1сий сигнал на выходе инвертора 4, т.е. на выходах триггера образуется кратковременный илброс. Таким образом, все режимы работы . D-триггера при приеме информации по входу D полностью рассмотрены: если в момент прихода следующего тактового импульса на входе D сохранится высокий логический сигнал, то работа 0-триггера будет повторять его ф|унк1щонирование в момент t, если же сигнал изменится на (тулевой, то работа D-триггера будет повторять его функционирование в момент t. Таким образом, D-триггер обеспечивает нормальное функционировавие при исцользовании более простых элементов, что позволяет сократить затраты оборудования на егл peajni aцию.

Авторы

Даты

1982-05-23—Публикация

1980-11-14—Подача