(54) УСТРОЙСТВО для ЗАДЕРЖКИ импульсов

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задержки импульсов | 1979 |

|

SU817992A1 |

| Двоично-десятичный счетчик вКОдЕ 8-4-2-1 | 1979 |

|

SU849498A1 |

| Устройство для задержки импульсов | 1978 |

|

SU739722A1 |

| Устройство синхронизации видеомагнитофона | 1981 |

|

SU965015A1 |

| Двоично-десятичный счетчик в коде 8-4-2-1 | 1987 |

|

SU1462474A1 |

| Двоично-десятичный счетчик в коде 8-4-2-1 | 1986 |

|

SU1415439A1 |

| Устройство для передачи измерительной информации | 1982 |

|

SU1062753A1 |

| Многоканальное устройство для измерения температуры | 1984 |

|

SU1229599A1 |

| Частотный манипулятор | 1982 |

|

SU1107322A2 |

| Устройство для синхронизации импульсных последовательностей | 1979 |

|

SU864521A1 |

1 « Изобретение относится к автомати ке и вычислительной технике и может быть применено ввычислительных устройствах различного назначения, где необходимо получение задержки послед вательностей импульсов, при высоких уровнях наводок и шумов. Известно устройство для задержки импульсов, содержащее входную шину, которая подключена ко входу первого элемента задержки и через инвертор ко входу второго элемента задержки, триггер на двух элементах И-НЕ, единичный вход триггера соединен с выходом второго элемента задержки через последовательно соединенную дифференцирующую цепочку и инвертор, а нулевой вход триггера соединен с вых дом первого элемента задержки через последовательно соединенные дифферен цирующуо цепочку и инвертор ClJ. Однако наличие в устройстве задеЬж ки дифференцирующих цепей приводит к низкой помехозащищенности, а также усложняет гибридно-пленочную технологию изготовления. Известно устройство для задержки импульсов, содержащее удвоитель частоты, элемент задержки, первый и второй инверторы, первый и вУорой элементы И-НЕ и RS-триггер, причем выход удвоителя частоты через элемент задержки подключен ко, входу первого инвертора, выход которого подключен к первым входам первого и второго элементов И-МЕ, второй вход первого элемента И-НЕ подключен к входной шине, ко входу удвоителя частоты и ко вхо- , ду второго инвертора, выход которого подключен ко второму входу второго элемента И-НЕ, выход которого подключен к R-входу RS-триггера, S-вход которого подключен к выходу первого элемента И-НЁ. Кроме того, указанное устройство для задержки импульсов содержит дополнительный RS-триггер на двух элементах И-ИЛИ-НЕ 2.

Однако известное устройство характеризуется недостаточно высокой надежностью функционирования при высоких уровнях наводок и шумов. Это обусловлено наличием дополнительного RS-триггера, который при воздействии наводок или шумов по цепям питания может переключаться в неправильное состояние.

Цель изобретения - повышение надежности,

, Поставленная цель достигается тем что в устройство для задержки импульсов, содержащее удвоитель частоты, элемент задержки, первый и второй ин верторы, первый и второй элементы Ии RS-триггер, причем выход удвоителя частоты через элемент задержки подключен ко входу первого инвертора, выход которого подключен к первым входам первогр и второго элементов И-НЕ, второй вход первого элемента И-НЕ подключен к входной шине, к входу удвоителя частоты и входу второго инвертора, выход которого подключен ко вторюму входу второго элемента И-Н выход которог9 подключен к R-входу RS-Tpkjrrepa, S-вход которого подключен к выходу первого элемента И-НЕ, введены третий и четвертый элементы И-НЕ, причем Q-выход RS-триггера подключен к первому входу третьего элемента И-НЕ, второй вход которого подключен к S-входу RS-триггера, R-вхрд которого подключен к первому .входу четвертого элемента И-НЕ, второй вход которого подключен к выходу третьего элемента И-НЕ, а выход четвертого элемента И-НЕ соединен с выходом устройства.

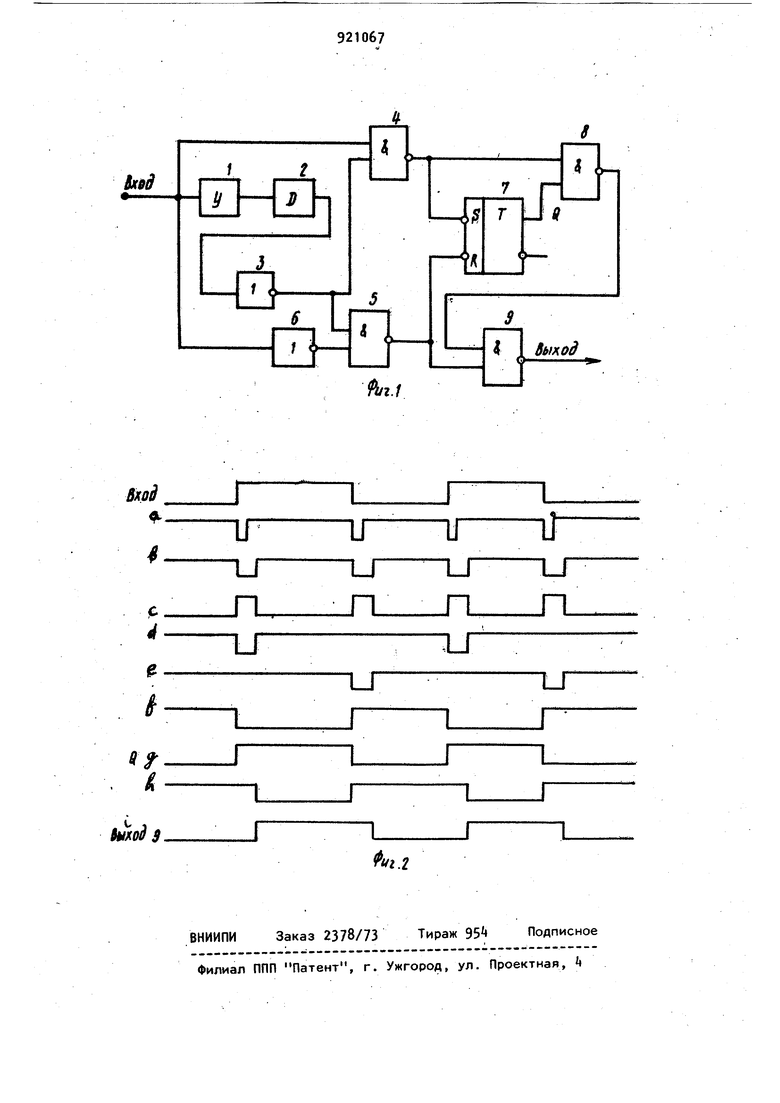

На фиг. 1 представлена электрическая принципиальная схема предлагаемого устройства для задержки импульсов; на фиг. 2 - временные диаграммы, поясняющие его работу.

Устройство для задержки импульсов содерммт удвоитель частоты 1, выход которого подключен ко входу элемента задержки 2, выход которого подключен к первому инвертору 3, выход которого подключен к первому входу первого элемента И-ИЕ i и к первому входу второгоЭлемента И-НЕ 5, второй вход которого подключен к выходу второго инвертора 6, выход первого элемента И-НЕ k подключен к S-входу RSтриггера 7 и к первому входу третьего элемента И-НЕ 8, выход которого

подключен к первому входу четвертого элемента И-НЕ 9. выход которого соединен с выходом устройства.

Работа устройства происходит следующим образом.

Перед подачей положительных импульсов на вход устройства на выходе удвоителя частоты 1 присутствует единичный высокий потенциал (см. диаграмму а на фиг, 2).

На выходе элемента задержки 2 присутствует высокий уровень напряжения, а на выходе первого инвертора 3 - низкий потенциал (см. диаграмму с фиг. 2). Низкий потенциал с выхода второго инвертора 3 приводит к образованию высоких потенциалов на выходах первого k и второго 5 элементов И-НЕ (см. диаграммы d и е на фиг. 2).

Допустим, что перед подачей импульсов RS-триггер 7 находится в состоянии 0. При этом на выходе Q RS-триггера 7 будет низкий сигнал (см. диаграмму .д на фиг. 2) , на выходе элемента И-НЕ 8 - высокий, а на .выходе четвертого элемента И-НЕ будет низкий сигнал, так как на обоих его входах присутствуют высокие сигналы (см. диаграмму i на фиг. 2).

В момент t4 начала первого входного импульса на выходе удвоителя частоты 1 формируется низкий сигнал, после чего формируется низкий уровен напряжения на выходе элемента задержки 2.

Этот сигнал образует высокий уровень напрях ения на выходе первого инвертора 3, после этого к обоим входам элемента И-НЕ приложены высоки уровни Напряжения, и на его выходе формируется низкий потенциал, который перебрасывает RS-триггер 7 в единичное состояние. На -выходе третьего элемента И-НЕ 8 будет высокий сигнал так как к его первому входу подключен низкий сигнал с выхода первого элемента И-НЕ . На выходе устройства остается низкий сигнал, так как к обоим входам четвертого элемента И-НЕ 9 приложены высокие сигналы. Других изменений выходных потенциалов элементов устройства в момент t не происходит.

По окончании периода задержки элемента задержки 2 (момент tj) на его выходе появляется высокий уровень напряжения. После этого ко второму

входу первого элемента И-НЕ j и к первому входу второго элемента И-НЕ приложены низкие потенциалы. Таким образом, на выходе первого и второго 5 элементов И-НЕ будут высокие по тенциалы. На выходе третьего элемента И-НЕ 8 будет низкий сигнал, так как к обоим его входам приложены выские сигналы. Других изменений выхрд; ных сигналов элементов устройства не происходит до момента tj окончания входного импульса.

В момент tj на выходе удвоителя частоты формируется низкий сигнал, на выходе элемента 2 задержки после этого формируется низкий сигнал. Это сигнал образует высокий сигнал на выходе инвертора 3- С момент tj на выходе второго инвертора 6 сформирован низкий сигнал, и на его выходе будет высокий сигнал (см. диаграмму фиг. 2).

Таким образом, к обоим входам второго элемента И-НЕ 5 приложены высокие сигналы, и на его выходе формируется низкий сигнал, который перебрасывает триггер 7 в нулевое состояние. На выходе Q триггера и элемента И-НЕ 8 будут низкие сигналы, однако на выходе четвертого элемента И-НЕ 9 останется высокий потенциал, так как ко второму входу четвертого элемента И-НЕ 9 приложен низкий сигнал с выхода элемента И-НЕ Других изменений выходных потенциаhoB элементов устройства в момент t не приходит.

По окончании периода задержки элемента задержки 2 (момент t,) на ее выходе появляется высокий сигнал. После этого ко входам элементов И-НЕ и 5 оказывается приложен низкий сигнал, таким образом, на выходе первого и второго 5 элементов И-НЕ появятся высокие потенциалы. На обоих , входах четвертого элемента И-НЕ 9 будут высокие сигналы, и на его выходе, являющемся выходом устройства, сформируется низкий сигнал.

В момент t все выходные сигналы элементов совпадают с их исходными состояниями. Поэтому, далее цикл работы устройства будет повторяться.

Использование данного технического решения позволяет повысить надежность функционирования устройства.

Формула изобретения

Устройство для задержки импульсов содержащее удвоитель частоты, элемент задержки, первый и второй инвертор, первый и второй элементы И-НЕ, RSтриггер, выход удвоителя частоты через элемент задержки подключен к. входу первого инвертора, выход которого подключен к первым входам первого и второго элементов И-НЕ, второй вход первого элемента И-НЕ подключен к входной шине, к входу удвоителя частоты и входу второго инвертора, выход которого подключен к второму входу второго элемента И-ИЕ, выход которого подключен к R входу RS -триггера, S-вход которого подключен к выходу первого элемента И-НЕ, отличающееся тем, что, с целью повьшения надежности, в него введены третий и четвертый элементы И-НЕ, причем Q-выход RS-триггера подключен к первому входу третьего элемента И-НЕ, второй вход которого подключен к S-входу RS-триггера., R-вход которого подключен к первому входу четвертого элемента , второй вход которого подключен к выходу третьего элемента И-НЕ, а выход четвертого элемента И-НЕ соединен с выходом устройства.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-04-15—Публикация

1980-07-17—Подача