(5) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ БИПОЛЯРНЫХ

1

Изобретение относится к области телеграфной и импульсной техники и может быть использовано в устройствах, предназначенных для формирования и передачи в линию связи двухполярных импульсов тока.

Известно устройство для передачи биполярных телеграфных сигналов, содержащее блок управления, первый выход которого подключен к первому входу первого коммутатора, первый выход которого соединен с первым входом второго коммутатора и с первым BtiBOfiotf резистора, второй вывод которого подключен к первому выводу диодного моста, второй вывод которого соединен со вторым выходом первого коммутатора и со вторым входом второго коммутатора, третий вход которого соединен со вторым выходом блока управления, третий выход которого соединен с положительным выводом источника питания и с первым выводом фотоприемника ТЕЛЕГРАФНЬ{Х СИГНАЛОВ

оптрона, анод светодиода которого соединен с третьим выводом диодного моста, четвертый вывод которого соединен с катодом светодиода оптрона, а также элементы задержки и элементы И, причем четвертый выход блока управления подключен к отрицательному выводу источника питания известном устройстве оперативный текущий контроль амплитуды и асимметрии биполярных телеграфных посылок затруднен, требует значительных трудозатрат и не обеспечивает необходимой достоверности.

Цель изобретения - повышение достоверности передачи.

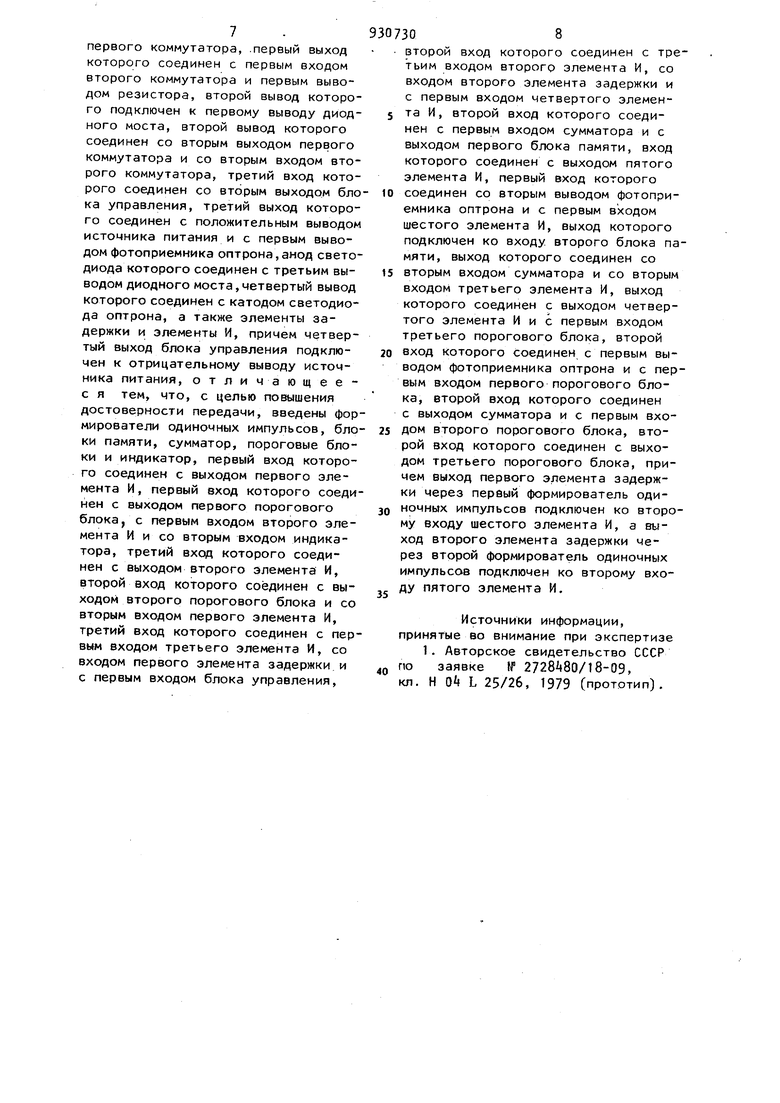

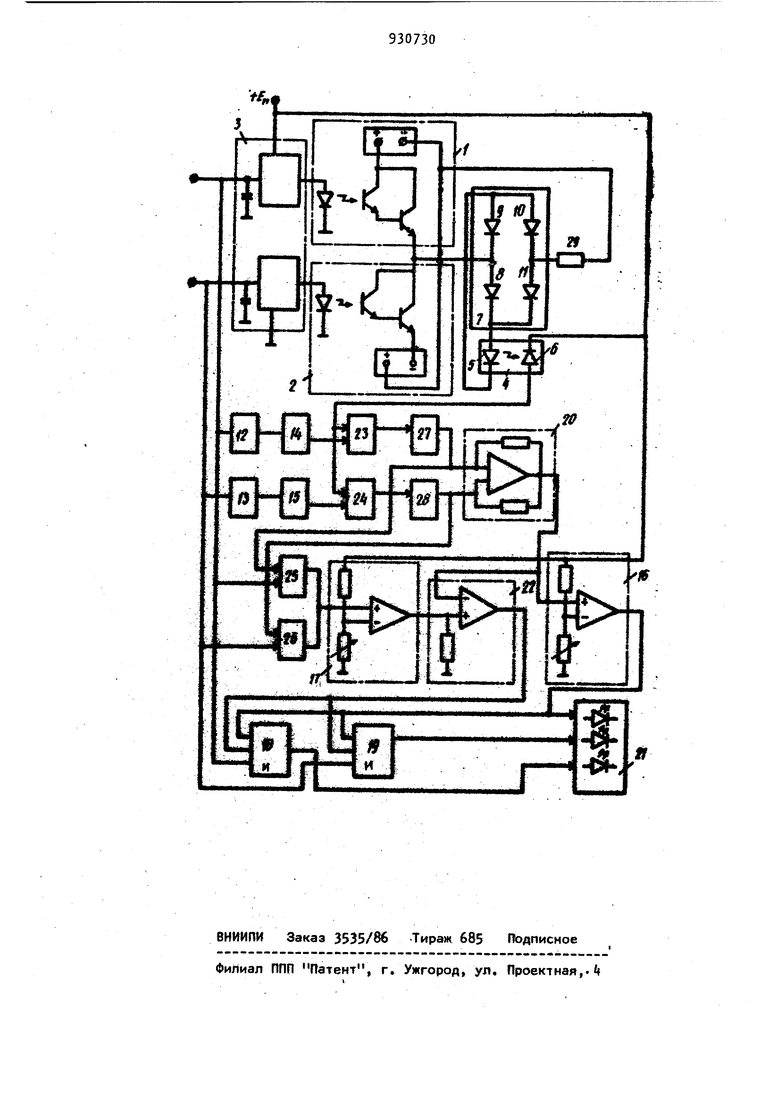

Поставленная цель достигается тем, что в устройство для передачи JQ биполярных телеграфных сигналов, содержащее блок управления, первый выход которого подключен к первому входу первого коммутатора, первый выход которого соединён с первым входом второго коммутатора и с первым выводом резистора, второй вывод которого подключен к первому выводу диодного моста, второй вывод которого соединен со вторым выходом первого коммутатора и со вторым входом второго коммутатора, третий вход которого соединен со вторым выходом блока управления, третий выход которого соединен с положительным выводом источника питания и с первым выводом фотоприемника оптрона, анод светодиода соединен с третьим выводом диодного моста, четвертый вывод которого соединен с катодом светодиода оптрона, а также элементы задержки и элементы И причем четвертый выход блока управления подключен к отрицательному выводу источника питания, введены формирователи одиночных импульсов, блоки памяти, сумматор, пороговые блоки и индикатор, первый вход которого соединен с выходом первого элемента И, первый вход которого соединен с выходом первого порогового блока, с первым входом второго элемента И и со вторым входом индикатора, третий вход которого соединен с выходом второго элемента И, второй вход которого соединен с выходом второго порогового блока и со вторым входом первого .элемента И, третий вход которого соединен с первым входом третьего элемента И, со входом первого элемента задержки с первым входом блока управления, вто рой вход которого соединен с третьим входом второго элемента И, со входом второго элемента задержки и с первым входом четвертого элемента И второй вход которого соединен с пер вым входом сумматора и с выходом пер вого блока памяти, вход которого соединен с выходом пятого элемента И, первый вход которого соединен со вторым выводом фотоприемника опт рона и с первым входом шестого элемента И, выход которого подключен ко входу второго блока памяти, выХОД которого соединен со вторым вхр дом сумматора и со вторым входом третьего элемента И, выход КОТОРОГО соединен с выходом четвертого элемента И и с первым входом третье го порогового блока, второй вход ко торого соединен с первым выводом фотоприемника оптрона и с первым вхо дом первого порогового блока, второй вход которого соединен с выходом сумматора и с первым входом второго порогового блока, второй вход которого соединен с выходом третьего порогового блока, причем выход первого элемента задержки через первый формирователь одиночных импульсов подключен ко второму входу шестого элементаИ, а выход второго элемента задержки через второй формирователь одиночных импульсов подключен ко второму входу пятого элемента И. На чертеже дана структурная электрическая схема предлагаемого устройства. Устройство содержит два коммутатора 1 и 2, блок 3 управления, оптрон t, содержащий светодиод 5 и фотоприемник 6, диодный мост 7, который содержит четыре диода 8-11, элементы 12 и 13 задержки, формирователи 14 и 15 одиночных импульсов, два пороговых блока 16 и 17, два a/teмента И 18 и 19. сумматор 20, индикатор 21, третий пороговый блок 22, элементы И 23 - 26, блоки 27 и 28 памяти и резистор 29Устройство работает следующим образом. В исходном состоянии, при отсутствии передачи информации, на входных клеммах присутствуют логические нули (О) При этом блок 3 исключает протекание тока через входные светодиоды коммутаторов 1 и 2, поэтому они закрыты. В результате этого ток в резисторе 29 и через светодиод 5 не протекает, в цепи фотоприемника 6 ток также отсутствует, поэтому на первых входах элементов И 23 и 2 сигнал отсутствует. Ввиду наличия на входных клеммах О, на вторых входах элементов И 23 - 26 и на первых входах элементов И 18 и 19 - также О. При этом элементы И 23 - 2б закрыты и на их выходах сигналы отсутствуют и на выходе сумматора 20 сигнал отсутствует с выходов блока 22 и порогового блока 16 поступают О, элемент индикатора 21, подключенный к выходу блока 16 выключен, что свидетельствует о том, что средняя амплитуда биполярных посылок ниже нормы (в данном случае свидетельствует об отсутствии амплитуды). Элементы индикатора 21 , подключенные к выходам элементов И 18 и 19 также выключены (нет необходимости контроля асим5метрии посылок биполярного сигнала, если средняя амплитуда биполярного сигнала равна нулю или ниже нормы). В процессе передачи информации на входные клеммы управляющие сигналы от передатчика поступают в противофазе. При поступлении на клемму логической единицы (1), а на клемму - О (передача стоповой посылки) включается коммутатор 1, что приводит к появлению тока положительного направления в резисторе 29- Этот ток протекает через светодиод 5 в результате чего в цепи фотоприемника 6 и на первых входах элементов И 23 и 2 появляется сигнал, пропорциональный амплитуде пол жительной посылки. Через время задержки, определяемое элементом 12, формирователь И вырабатывает одиночный импульс, поступающий на второй вход элемента И 23, а результате чего сигнал с первого входа элемента И 23 поступает в блок 27, где запоминается его амплитуда, т.е. элемент И 23 и блок 27 представляют собой схему выборки и запоминания (элемент 2k остается закрытым). (Элемент 12 и формирователь Н обеспечивают выборку для запоминания ам плитуды положительной посылки в моменты времени, когда амплитуда посылки уже установилась. Выборка осуществляется на временном интервале, менее подверженном влия нию помех (целесообразнее всего выборку осуществлять в средней части элементарной посылки в течение времени, значительно меньшем длительности элементарной посылки). После окончания выборки на выходе сумматора 20 устанавливается амплитуда напряжения, пропорциональная амплитуде положительной посылки. Порог включения порогового блока 16 выбирается соответствующим минимально допустимому среднему значению амплитуд положительной и отрицательной посылок, поэтому на выходе блока 16 сохраняется О, который бйокирует элементы И 18 и t9 и на их выходах сохраняется О, независимо от сигналов на других их выходах. Элементы индикатора 21 остаются в выключенном состоянии. При поступлении на одну входную клемму О и одновременном поступлении на вторую клемму 1 (передача стартовой посылки) коммута0тор 1 выключается, а коммутатор 2 включается, что приводит к появлению кода отрицательного направления в резисторе 29. Этот ток также протекает и через сведодиод 5, в результате чего в цепи фотоприемника 6 и на первых входах элементов И 23 и 2 появляется сигнал, пропорциональ ный амплитуде отрицательной посылки. Через время задержки, определяемое элементом 13, формирователь 15 вырабатывает одиночный импульс, поступающий на второй вход элемента И 2, в результате чего сигнал с первого входа элемента И 2k поступит в блок 28, где запоминается его амплитуда ( элемент И 23 остается закрытым). После окончания выборки на выходе блока 28 устанавливается амплитуда напряжения, пропорциональная амплитуде отрицательной посылки. Теперь на оба входа сумматора 20 воздействуют напряжения с блоков 27 и 28 и на его выходе устанавливается напряжение, пропорциональное сумме абсолютных значений амплитуд положительной и отрицательной посылок. Если среднее значение абсолютных значений амплитуд положительной и отрицательной посылок находится в допустимых пределах (превышает минимально допустимую величину, пороговый блок 16 включается и на его выходе появляется 1, что снимает блокировку с входов элементов И 18 и 19 и включает элемент индикатора 21, подключенный к выходу блока 16 (включенное состояние этого индикатора свидетельствует о том, что средняя амплитуда биполярных посылок находится а норме)t. Напряжение с выхода сумматора 20 поступает и на первый вход блока 22, тем самым определяя его порог срабатывания. В про- : цессе передачи информации на второй вход блок 22 через пороговый блок 17 поочередно поступают напряжения, прюпорциональные амплитудам положительной и отрицательной посылок (с выходов блоков 27 и 28 через соответствующие элементы И 25 и 26). Формула изобретения Устройство для передачи биполярных телеграфных сигналов, содержащее блок управления, первый выход которого подключен к первому входу

первого коммутатора, .первый выход которого соединен с первым входом второго коммутатора и первым выводом резистора, второй вывод которого подключен к первому выводу диодного моста, второй вывод которого соединен со вторым выходом первого коммутатора и со вторым входом второго коммутатора, третий вход которого соединен со вторым выходом блока управления, третий выход которого соединен с положительным выводом источника питания и с первым выводом фотоприемника оптрона,анод светодиода которого соединен с третьим выводом диодного моста, четвертый вывод которого соединен с катодом светодиода оптрона, а также элементы задержки и элементы И, причем четвертый выход блока управления подключен к отрицательному выводу источника питания, отличающеес я тем, что, с целью повышения достоверности передачи, введены формирователи одиночных импульсов, блоки памяти, сумматор, пороговые блоки и индикатор, первый вход которого соединен с выходом первого элемента И, первый вход которого соединен с выходом первого порогового блока, с первым входом второго элемента И и со вторым входом индикатора, третий вход которого соединен с выходом второго элемента И, второй вход которого соединен с выходом второго порогового блока и со вторым входом первого элемента И, третий вход которого соединен с первым входом третьего элемента И, со входом первого элемента задержки и с первым входом блока управления.

307308

второй вход которого соединен с третьим входом второго элемента И, со входом второго элемента задержки и с первым входом четвертого элемента И, второй вход которого соединен с первым входом сумматора и с выходом первого блока памяти, вход которого соединен с выходом пятого элемента И, первый вход которого

10 соединен со вторым выводом фотоприемника оптрона и с первым входом шестого элемента И, выход которого подключен ко входу второго блока памяти, выход которого соединен со

15 вторым входом сумматора и со вторым входом третьего элемента И, выход которого соединен с выходом четвертого элемента И и с первым входом третьего порогового блока, второй

20 вход которого соединен с первым выводом фотоприемника оптрона и с первым входом первого порогового блока, второй вход которого соединен с выходом сумматора и с первым входом второго порогового блока, второй вход которого соединен с выходом третьего порогового блока, причем выход первого элемента задержки через первый формирователь одиночных импульсов подключен ко второму входу шестого элемента И, а выход второго элемента задержки через второй формирователь одиночных импульсов подключен ко второму входу пятого элемента И.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР заявке № 2728 80/18-09,

по

кл. Н Of L 25/26, 1979 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи биполярных телеграфных сигналов | 1981 |

|

SU1003379A2 |

| Устройство для формирования двухполярных сигналов | 1985 |

|

SU1290553A1 |

| Устройство для передачи телеграфного сигнала | 1980 |

|

SU1202067A1 |

| Двухуровневый оптоэлектронный переключатель | 1982 |

|

SU1069166A2 |

| Устройство для регистрации телеграфных посылок | 1981 |

|

SU1053316A1 |

| Выходное телеграфное устройство | 1984 |

|

SU1172057A1 |

| Оптоэлектронное устройство для контроля линейного тракта электронного телеграфного аппарата | 1983 |

|

SU1128403A2 |

| Устройство для формирования биполярных телеграфных посылок | 1979 |

|

SU773949A1 |

| Устройство для двухпроводного дуплексного телеграфирования | 1980 |

|

SU966924A1 |

| Оптоэлектронное входное устройство | 1981 |

|

SU1030983A2 |

Авторы

Даты

1982-05-23—Публикация

1980-08-15—Подача