(5) УСТРОЙСТВО дш ттт Дйеш ЕТ«о« ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с каналом передачи данных | 1989 |

|

SU1647580A1 |

| Устройство для обмена информацией | 1987 |

|

SU1497619A1 |

| Многоканальное устройство для ввода информации | 1984 |

|

SU1265783A1 |

| УСТРОЙСТВО ВРЕМЕННОГО УПЛОТНЕНИЯ АСИНХРОННЫХ | 1973 |

|

SU385399A1 |

| СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ ПО РАДИОКАНАЛАМ ИМПУЛЬСНО-ФАЗОВОЙ РАДИОНАВИГАЦИОННОЙ СИСТЕМЫ | 1994 |

|

RU2079855C1 |

| Устройство для контроля ввода-вывода | 1980 |

|

SU896626A1 |

| Устройство для обнаружения ошибок в несистематическом сверточном коде | 1988 |

|

SU1662012A1 |

| СИСТЕМА ДУПЛЕКСНОЙ ВЫСОКОСКОРОСТНОЙ КОРОТКОВОЛНОВОЙ РАДИОСВЯЗИ | 2013 |

|

RU2553091C2 |

| Устройство групповой тактовой синхронизации (его варианты) | 1982 |

|

SU1096760A1 |

| Система ввода телевизионных изображений в ЭВМ | 1989 |

|

SU1665391A1 |

:. -... .

Изобретение относится к электро- связи и может исгюпьзоватьс в аппаратуре сеансной связи для п|Я1ема сообщений с ограниченным временем передачи по каналу свйзи. :

Известно устройство для гфиема дискретной информации содержшгее узел синхронизации по посыпкам, первый выход которого подключен к первому входу блока декодирований че- . рез регистрирующий узел а к второму - через блок синхронизации гю циклам, другой вход которого соединен с выходом регистрирующего узла П.

Недостаток известного устройства заключается в плохом использовании пропускной способности канала связи, что обусловлено большой долей синхронизирующей информации в сообщении. Например, для наиболее оптимальной системы синхронизации с переменным шагом с усредняющим устройством без блокировок для вхождения в синхрониэм Tfx iyeTCff около 60 посылок tr, с. П5-Ш|.

Цель иэ &ретейия - увеличение объеме прифт емой информации, а следовательно, и коэффициента испопь | эсдаанй протчскной способности канала сбяэ.

Лостёютннай цель достигается тем что в устройство для приема да1С4фетмо{| и«4ф таиии, содержащее уэея синх|х ниэации гю посылкам, первьй которого подкточен к первому вхсщу блока декод«4рования через регистрирующий узел, а к второ- му - через блок синхронизации по циклам, другс вход которого соединен с выходом регистрирующего узла, 8веде«ш переключатель, форкмрователь сигналов записи, элемент задержки, адресный регистр, формирователь сигналов считывания и последовательно соединенные входной элемент И и блок памяти, выход которого подключен к другом/ входу регистрирующего узла и к первому входу переключателя, второй вход которого соединен с выходом входного элемента И, а третий вход соединен с выходом блока декодирования, при этом выход переключателя подключен к входу узла синхронизации по посылкам, дополнительный выход которого соединен с другим входом входного элемента И и с входами формирователя сигналов записи и элемента задержки, выход которого подключен через адресный регистр к адресному входу блока памяти, а через формирователь сигналов считывания к считывающему входу блока памяти, записываккций вход которого соединен с вы-ходом формирователя сигналов записи.

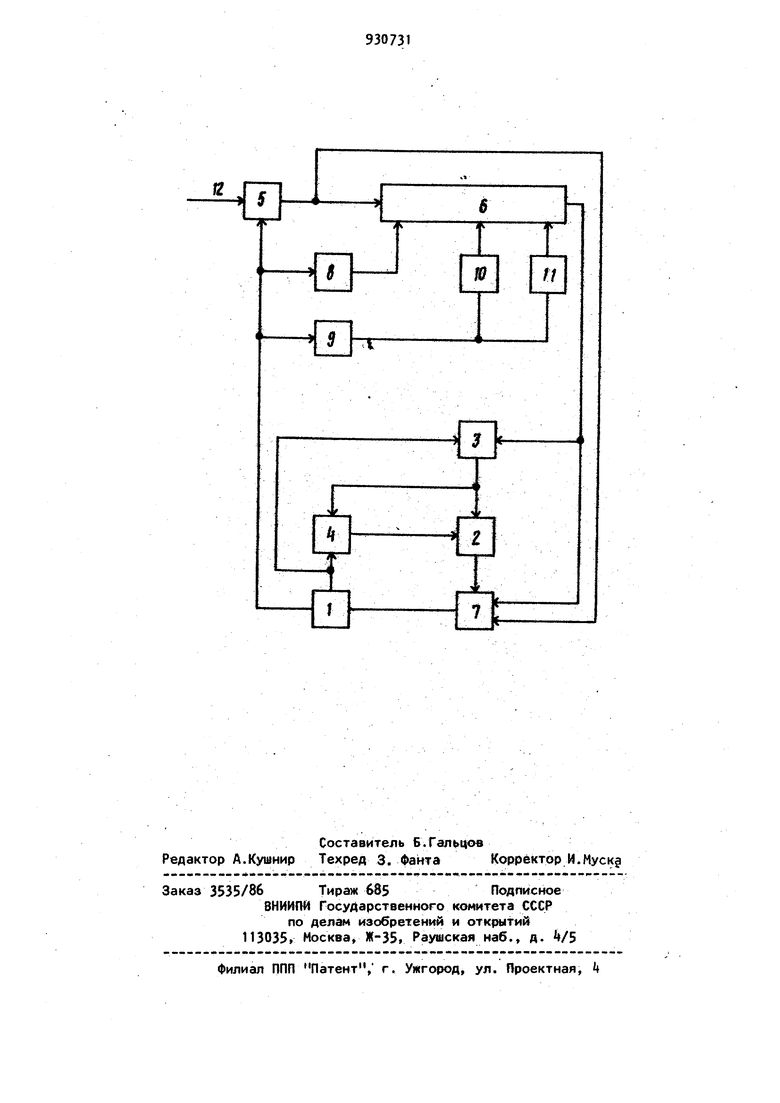

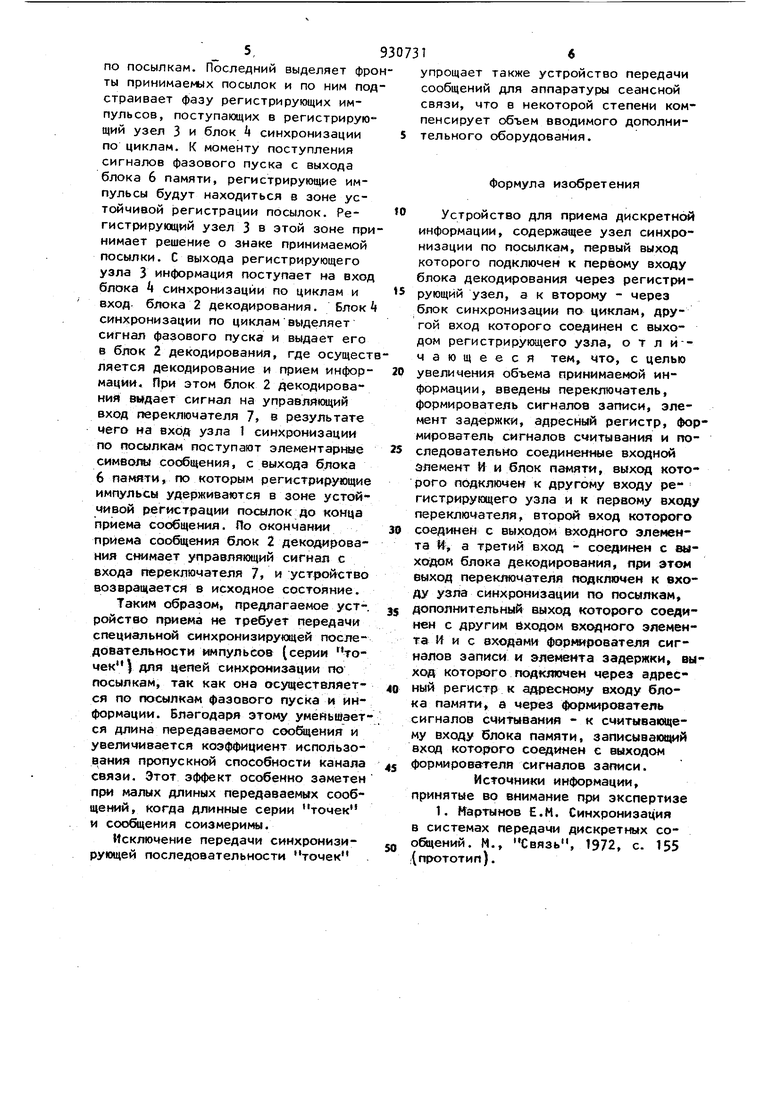

На чертеже дана структурная схема устройства.

Устройство содержит узел 1 синхронизации по посылкам, блок 2 декодирования, регистрирующий узел 3, блок k синхронизации по циклам, вхоной элемент W 5 6 памяти, переключатель 7, формирователь 8 сигналов записи, элемент 9 задержки, адресный регистр 10 и формирователь И си йалрв считывания.

Вход устройства t2 через последовательно соединенные входной элемент И 5 и блок 6 памяти подключен к ВХОДУ регис три руще го узла 3 и к первому входу оереклю ателя 7- Второй вход переключателя 7 соединен с выходом входного элемента И 5 третий вход с выходом бЛэкэ 2 декодирова+4ия,з выход переключателя 7 под г ключей к входу узла t синхронизации по посылкам, Первый выход узла 1 синхронизамии по посылкам подключен к первому входу блока 2 декодирования через регистрирующий узел 3, а к второму входу - через блок Ц , синхронизации по циклам другой вхо которого соединен с выхрдом регистрирующего узла 3. Дополнительный выход узла 1 синхронизации по посылкам соединен с другим входом входного элемента И 5 с входом формирователя 8 сигналов записи и с входом элемента 9 задержки, выходом подключенного через адресный регистр 10 к адресному входу блока памяти, а через формирователь 11 сигналов считывания - к считывающему входу блока б памяти, записывающий вход которого соединен с выходом формирователя 8. сигналов записи.

Устройство работает следующим образом.

Принимаемое сообщение, из состава которого исключены синхронизирующие импульсы, необходимые для синхронизации по посылкам (серии точек) поступает на вход устройства 12, На

входном элементе И 5 двоичные посылки сообщения стробируются частотой

1

F.

, поступающей с узла 1 синхб &г

5 ронизации по посылкам, где и. t - минимальная величина коррекции фазы регистрирующего импульса.

Пачки единиц и нулей (в дальнейшем именуемые элементарными символами}, соответствующие единичным и нулевым посылкам фазового пуска и информации с выхода входного эле(мента И 5 поступают на вход блока 6 памяти, в котором каждый элементарный символ запоминается по сигналу записи, формируемому с частотой формирователем 8 сигналов записи и по адресу, выдаваемому адресным регистром 10.

Импульсы тактовой частоты поступают также через элемент 9 задержки в адресный регистр 10, осуществляя смену адреса, а также в формирователь 1 1 сигналов считывания, осуществляя считывание информации из

блока 6 памяти по адресу, выдаваемому адресным регистром 10. Со следующим тактом частоты Fg происходит запись очередного элементарного символа в ту ячейку памяти блока 6, из которой предыдущим тактом частоты Гц был считан элементарный символ. Адреса записи и считывания, формируемые адресным регистром 10, периодически повторяются, при этом цикл

повторений равен объему памяти блока 6, например, если объем блока памяти равен 800 двоичных разрядов, то элементарный символ будет считан из блока 6 памяти через А800 тактов

0 частоты. Таким образом, блок 6 памяти по существу осуществляет задержку элементарных символов на необходимое время. Элементарные символы с выхода Входного элемента И 5 поступают также через переключатель 7 устанавливаемый в исходное состояние сигналом с блока 2 декодирования, на вход узла 1 синхронизации по посылкам. Последний выделяет фро ты принимаемых посылок и по ним под страивает фазу регистрирующих импульсов, поступающих в регистрирующий узел 3 и блок Ц синхронизации по циклам. К моменту поступления сигналов фазового пуска с выхода блока 6 памяти, регистрирующие импульсы будут находиться в зоне устойчивой регистрации посылок. Регистрирующий узел 3 в этой зоне при нимает решение о знаке принимаемой посылки. С выхода регистрирующего узла 3 информация поступает на вход блока k синхронизации по циклам и вход блока 2 декодирования. Блок синхрюнизации по циклам выделяет сигнал фазового пуска и его в блок 2 декодирования, где осущест ляется декодирование и прием информации При этом блок 2 декодирований выдает сигнал на управяя«яций вход переключателя 7 в результате чего на вход узла 1 синхронизации по посылкам поступают элементарные символы сообщения, с выхода блока 6 памяти, по которым регистрирующие импульсы удерживаются в зоне устой чивой регистрации посылок до конца приема сообщения. По окончании приема сообщения блок 2 декодирования снимает управляющий сигнал с входа переключателя 7, и устройство возвращается в исходное состояние. Таким образом, предлагаемое устройство приема не требует передачи специальной синхронизирующей последовательности импульсов (серии точек V А цепей синхронизации по посылкам, так как она осуществляется по посылкам фазового пуска и информации. Благодаря уменьшает ся длина передаваемого сооОдения и увеличивается коэффициент использования пропускной способности канала связи. Этот эффект особенно заметен при малых длиных передаваемых сообщений, когда длинные серии точек и сообщения соизмеримы. Исключение передачи синхронизирующей последовательности точек упрощает также устройство передачи сообщений для аппаратуры сеансной связи, что в некоторой степени компенсирует объем вводимого дополнительного оборудования. Формула изобретения Устройство для приема дискретной информации, содержащее узел синхронизации по посылкам, первый выход которого подключен к первому входу блока декодирования через регистрирующий узел, а к второму - через блок синхронизации по циклам, другой вход которого соединен с выходом регистрирующего узла, о т л й-чающееся тем, что, с целью увеличения объема принимаемой информации, введены переключатель, формирователь сигналов записи, элемент задержки, адресный регистр, формирователь сигналов считывания и последовательно соединенные входной элемент И и блок памяти, выход которого подключен к другому входу регистрирующего узла и к первому входу переключателя, второй вход которого соединен с выходом входного элемента И, а третий вход - соединен с выходом блока декодирования, при этом выход переключателя подключен к входу узла синхронизации по посылкам, дополнительный выход которого соединен с другим входом входного элемента W и с входами формирователя сигналов записи и элемента задержки, выход которого подключен через адресный регистр к адресному входу блока памяти, а через формирователь сигналов считывания - к считываюцему входу блока памяти, записываюоий вход KoTojjoro соединен с выходом формирователя сигналов записи. Источники информации, принятые во внимание при экспертизе 1. Картынов Е.М. Синхронизация в системах передачи дискретных сообцений. М., Связь, 1972, с. 155 ,( прототип).

12

(Iif

n

Авторы

Даты

1982-05-23—Публикация

1980-10-10—Подача