(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ВВОДА-ВЫВОДА

1

Изобретение относится к вычислительной технике,и может быть исполь-, зовано для контроля кадов вводимой и выводимой информации в цифровых вычислительных и -управляющих машинах.

Известно устройство для контроля хранения информации в буферном ЗУ, в котором используются схемы контроля символа считанной информации по нечету. Контроль по нечету осуществляется при помощи регистра считанного символа 1.

Недостатком данного устройства является то, что при контроле вводимой информации до момента записи в ЗУ не проверяется правильность функционирования аппаратуры, осуществляющей запись в ЗУ. Организация же контроля информации в ЗУ требует затрат времени не только на считывание , но также на ее восстановление в ЗУ. Кроме того, в указанных устройствах при выявлении блоком контроля сбойной информации невозможна организация разветвлений в программах. ..

Наиболее близким к предлагаемому по технической сущности является устройство, содержащее блок памяти, регистр адреса (РА), блок синхронизации, дешифратор адреса, регистр числа (РЧ), блок контроля четности и блок ввода, причем входы регистра адреса соединены с адресной магистралью , а выходы - со входами дешифратора адреса, Выходы дешифратора адреса соединены с адресными входами блока памяти, разрядные входы которого соединены с выходами РЧ, а вы10ходы - с числовой магистралью, к числовой магистрали подключены также входы регистра числа, входа блока контроля четности и выход блока ввода, на входы блока ввода поступает

ts код числа, принимаемый -в внешнего устройства, а также сигнал Разрешение ввода , выходы чтения и записи блока синхронизации соединены с блоком памяти, выходы блока синхрони20зации соединены со входами РА и РЧ, выход чтения блока синхронизации соединены со входом блока контроля четности 2 .

Контроль информации, поступаквдий с числовой магистрали на вход блока контроля четности, осуществляется путем проверки на четность (или на нечетность) числа единиц в слове. При появлении на числовой магистрали

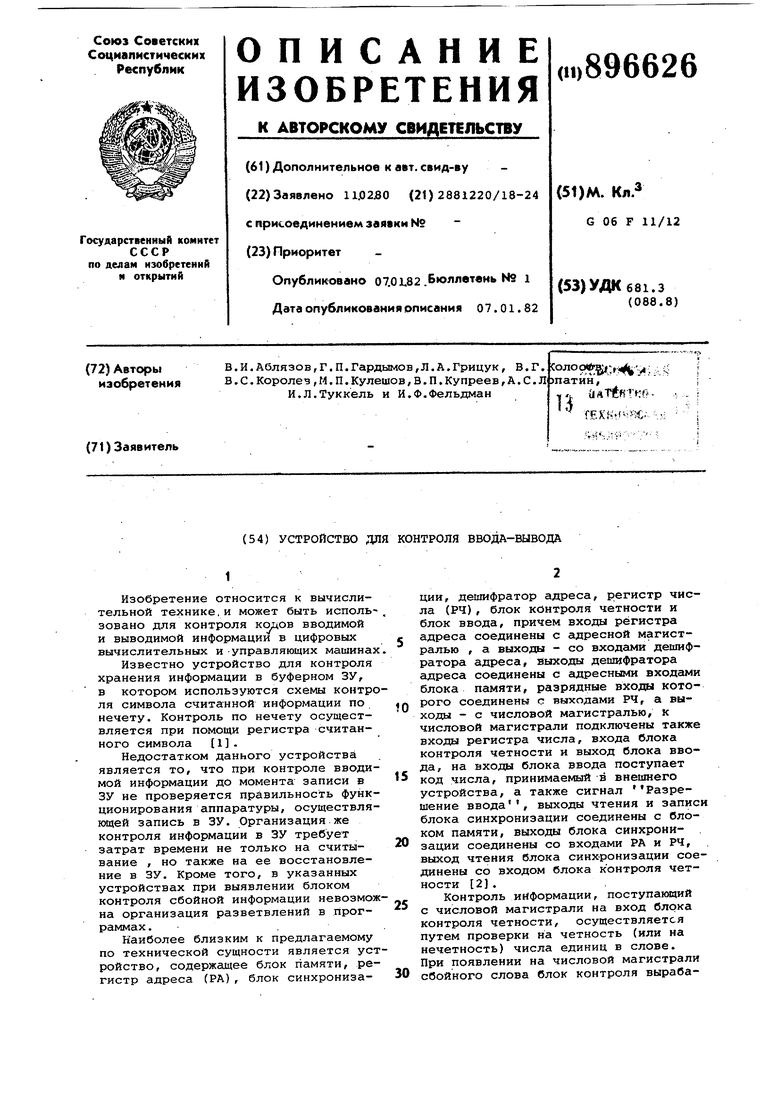

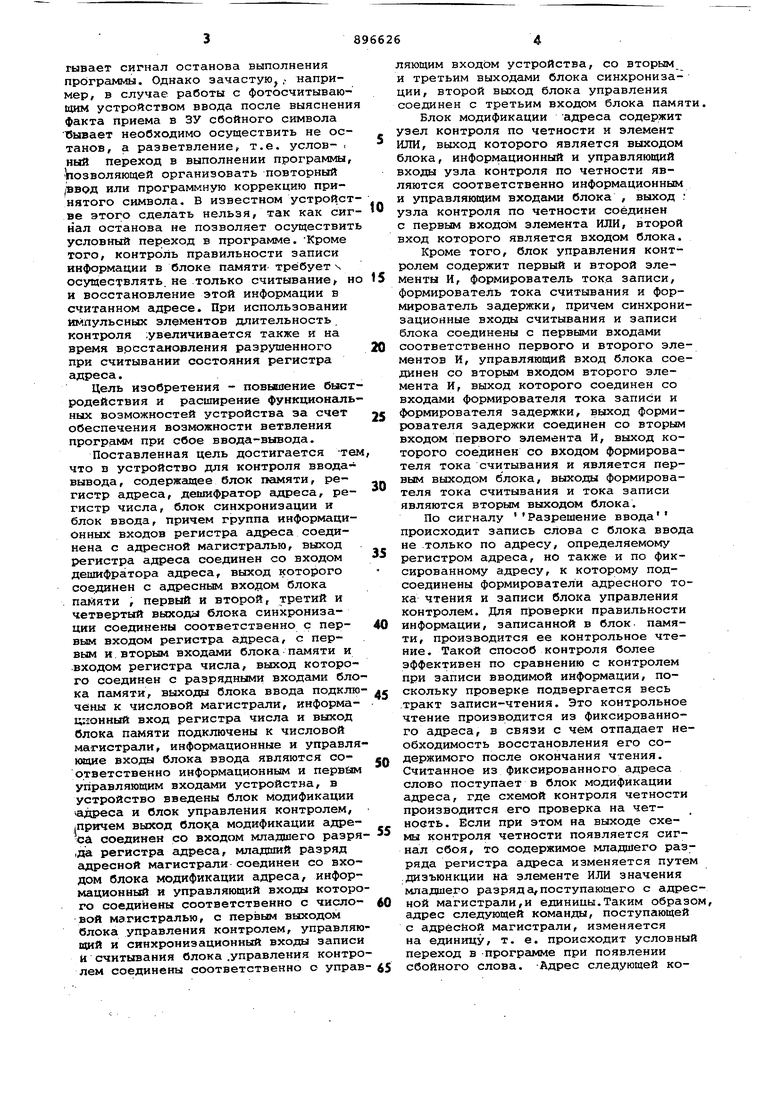

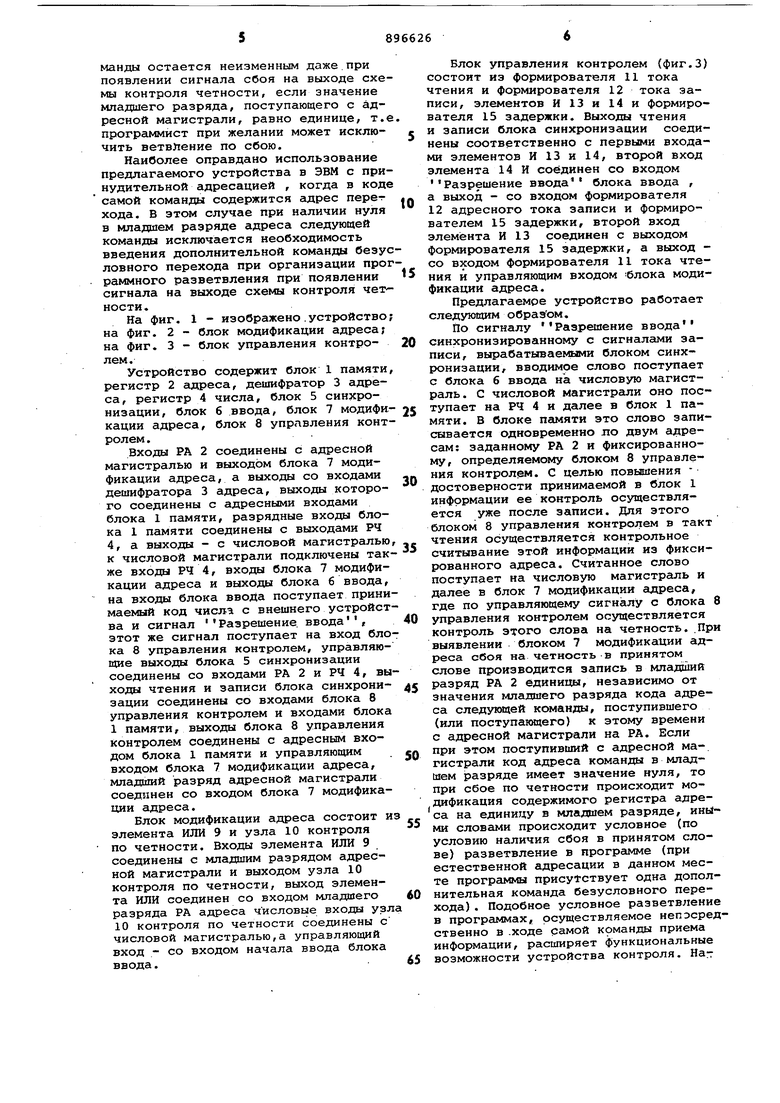

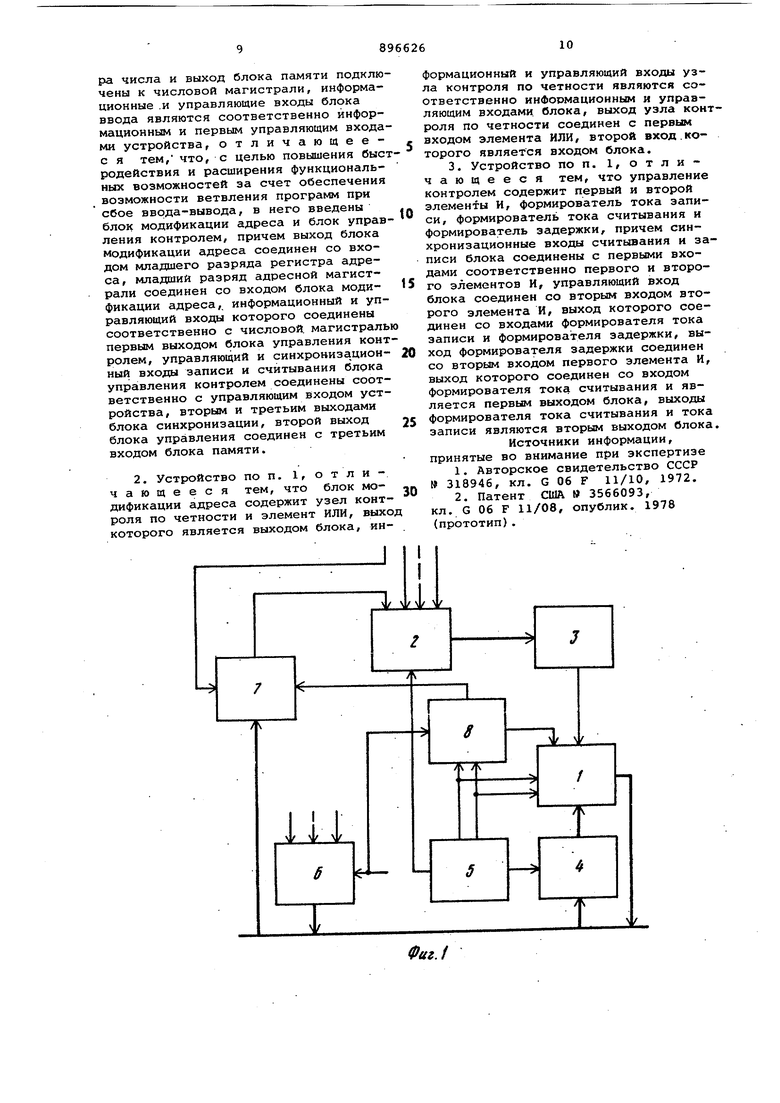

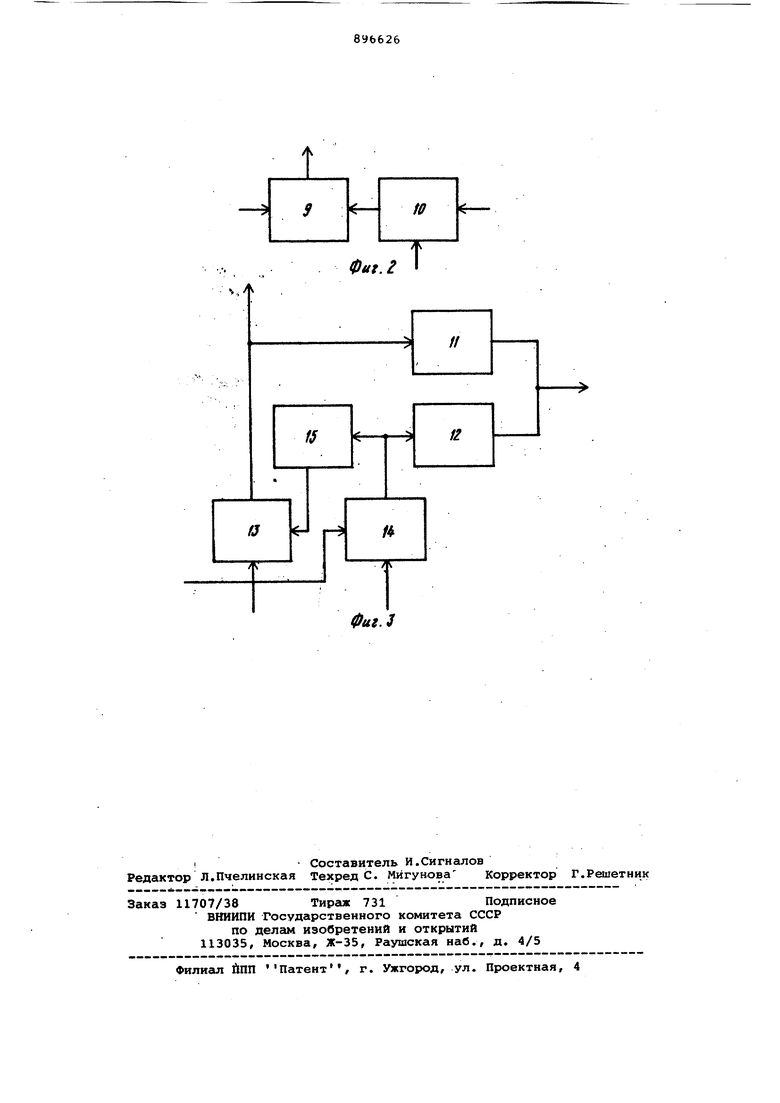

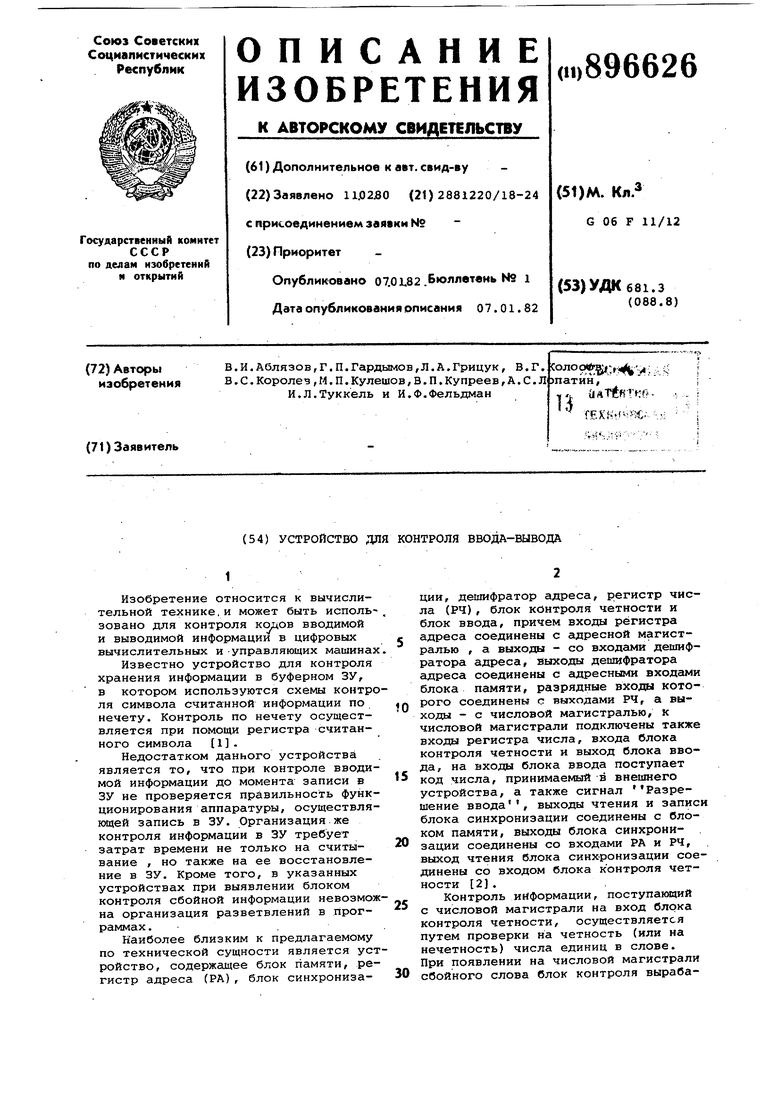

30 сбойного слова блок контроля вырабагывает сигнал останова выполнения программы. Однако зачастую, ,- например, в случае работы с фотосчитывающим устройством ввода после выяснени факта приема в ЗУ сбойного символа Т5ывает необходимо осуществить не останов, а разветвление, т.е. услов- . ный переход в выполнении программы, позволяющей организовать повторный /ввод или программную коррекцию принятого символа. В известном устройст ве этого сделать нельзя, так как сиг нал останова не позволяет осуществит условный переход в программе. Кроме того, контроль правильности записи информации в блоке памяти требует ч осуществлять, не только считывание, н и восстановление этой информации в считанном адресе. При использовании импульсных элементов длительность контроля увеличивается также и на время врсстаиовления раэр тденного при считывании состояния регистра адреса. Цель изобретения - повышение бьют родействия и расширение функциональ ных возможностей устройства эа счет обеспечения возможности ветвления программ при сбое ввода-вывода. Поставленная цель достигается -те что в устройство для контроля вводавывода, содержаицее блок памяти, регистр адреса, дешифратор адреса, регистр числа, блок синхронизации и блок ввода, причем группа информационных входов регистра адреса соединена с адресной магистралью, выход регистра адреса соединен со входом дешифратора адреса, выход которого соединен с адресным входом блока пайяти , первый и второй, третий и четвертый выхода блока синхронизации соединены соответственно с первым входом регистра адреса, с первым и.вторым входами блока памяти и входом регистра числа, выход которого соединен с разрядными входами бло ка памяти, выходы блока ввода подклю чены к числовой магистрали, информа1;:-1ОНный вход регистра числа и выход блока памяти подключены к числовой магистрали, информационные и управля ющие входы блока ввода являются соответственно информационным и первйм управляющим входами устройства, в устройство введены блок модификации iaflpeca и блок управления контролем, .причем выход блоца модификации адреса соединен со входом младшего разря да регистра адреса, младший разряд адресной магистрали-соединен со входом блока модификации адреса, информационный и управляющий входы которо го соединены соответственно с числовой ма гистралью, с первым выходом блока управления контролем, управляю щий и синхронизационный входы записи И считывания блока .управления контро лем соединены соответственно о управ ляющим входом устройства, со вторым и третьим выходами блока синхронизации, второй выход блока управления соединен с третьим входом блока памяти. Блок модификации адреса содержит узел контроля по четности и элемент ШШ, выход которого является выходом блока, информационный и управляющий входы узла контроля по четности являются соответственно информационным и управляющим входами блока , выход : узла контроля по четности соединен с первым входом элемента ИЛИ, второй вход которого является входом блока. Кроме того, блок управления контролем содержит первый и второй элементы И, формирователь тока записи, формирователь тока считывания и формирователь задержки, причем синхронизационные входы считывания и записи блока соединены с первыми входами соответственно первого и второго элементов И, управляющий вход блока соединен со вторым входом второго элемента И, выход которого соединен со входами формирователя тока записи и формирователя задержки, выход формирователя задержки соединен со вторым входом первого элемента И, выход которого соединен со входом формирователя тока считывания и является первым выходом блока, выходы формирователя тока считывания и тока записи являются вторым выходом блока. По сигналу Разрешение ввода происходит запись слова с блока ввода не только по адресу, определяемому регистром адреса, но также и по фиксированному адресу, к которому подсоединены формирователи адресного тока чтения и записи блока управления контролем. Для проверки правильности информации, записанной в блок, памяти, производится ее контрольное чтение. Такой способ контроля более эффективен по сравнению с контролем при записи вводимой информации, поскольку проверке подвергается весь тракт записи-чтения. Это контрольное чтение производится из фиксированного адреса, в связи с чём отпадает необходимость восстановления его содержимого после окончания чтения. Считанное из фиксированного адреса слово поступает в блок модификации адреса, где схемой контроля четности производится его проверка на четнооть. Если при этом на выходе схемы контроля четности появляется сигнал сбоя, то содержимое младшего разряда регистра адреса изменяется путем .дизъюнкции на элементе ИЛИ значения младшего разряд а, поступающего с адресной магистрали,и единицы.Таким образом, адрес следующей команды, поступающей с адресной магистрали, изменяется на единицу, т. е. происходит условный переход в -программе при появлении сбойного слова. -Адрес следующей команды остается неизменным даже.при появлении сигнала сбоя на выходе схе мы контроля четности, если значение младшего разряда, поступающего с адресной магистрали, равно единице, т. программист при желании может исключить ветвление по сбою. Наиболее оправдано использование предлагаемого устройства в ЭВМ с при нудительной адресацией , когда в код самой команды содержится адрес пере-г хода. В этом случае при наличии нуля в младшем разряде адреса следующей команды исключается необходимость введения дополнительной команды безу ловного перехода при организации про раммного разветвления при появлении сигнала на выходе схемы контроля чет ности. На фиг. 1 - изображено.устройство на фиг. 2 - блок модификации адреса; на фиг. 3 - блок управления контролем. Устройство содержит блок 1 памяти регистр 2 ёщреса, дешифратор 3 адреса, регистр 4 числа, блок 5 синхронизации, блок 6 ввода, блок 7 модифи кации адреса, блок 8 управления конт ролем. Входы РА 2 соединены с адресной магистралью и выходом блока 7 модификации адреса, а выходы со входами дешифратора 3 адреса, выходы которого соединены с адресными входами блока 1 памяти, разрядные входы блока 1 памяти соединены с выходами РЧ 4, а выходы - с числовой магистралью к числовой магистрали подключены так же входы РЧ 4, входы блока 7 модификации адреса и выходы блока 6 ввода, на входы блока ввода поступает прини маемый код числи с внешнего устройст ва и сигнал Разрешение, ввода , этот же сигнал поступает на вход бло ка 8 управления контролем, управляющие выходы блока 5 синхронизации соединены со входами РА 2 и РЧ 4, вы ходал чтения и записи блока синхроиизации соединены со входами блока 8 управления контролем и входами блока 1 памяти, выходы блока 8 управления контролем соединены с адресным входом блока 1 памяти и управляющим . входом блока 7 модификации адреса, младший разряд адресной магистрали соединен со входом блока 7 модификации адреса. Блок модификации адреса состоит и элемента ИЛИ 9 и узла 10 контроля по четности. Входы элемента ИЛИ 9 соединены с младшим разрядом адресной магистрали и выходом узла 10 контроля по четности, выход элемента ИЛИ соединен со входом младшего разряда РА адреса числовые входы узл 10 контроля по четности соединены с числовой магистралью,а управляющий вход - со входом начала ввода блока ввода. Блок управления контролем (фиг.З) состоит из формирователя 11 тока чтения и формирователя 12 тока записи, элементов И 13 и 14 и формирователя 15 задержки. Выходы чтения и записи блока синхронизации соединены соответственно с первыми входами элементов И 13 и 14, второй вход элемента 14 И соединен со входом Разрешение ввода блока ввода , а выход - со входом формирователя 12 адресного тока записи и формирователем 15 задержки, второй вход элемента И 13 соединен с выходом формирователя 15 задержки, а выход со входом формирователя 11 тока чтения и управляющим входом блока модификации адреса. Предлагаемое устройство работает следующим обраэом. По сигналу Разрешение ввода синхронизированному с сигналами записи, вырабатываеколми блоком синхронизации, вводимое слово поступает с блока 6 ввода на числовую магистраль. С числовой магистрёши оно поступает на РЧ 4 и далее в блок 1 памяти. В блоке памяти это слово записывается одновременно ло двум с1Дресам; заданному РА 2 и фиксированному, определяемому блоком 8 управле ния контролем. С целью повышения достоверности принимаемой в блок 1 информации ее контроль осуществляется уже после записи. Для этого блоком 8 управления контролем в такт чтения осуществляется контрольное считывание этой информации из фиксированного адреса. Считанное слово поступает на числовую магистраль и далее в блок 7 модификации гшреса, где по управляющему сигналу с блока 8 управления контролем осуществляется контроль этого слова на четность..При выявлении блоком 7 модификации адреса сбоя на четность-в принятом слове производится запись в младашй разряд РА 2 единицы, независимо от значения младшего разряда кода адреса следующей команды, поступившего (или поступающего) к этому времени с адресной магистрали на РА. Если при этом поступивший с адресной магистрали код адреса команды в младшем разряде имеет значение нуля, то при сбое по четности происходит модификация содержимого регистра адреса на единицу в младшем разряде, иными словами происходит условное (по условию наличия сбоя в принятом слове) разветвление в программе (при естественной адресации в данном месте программы присутствует одна дополнительная команда безусловного перехода) . Подобное условное разветвление в программах, осуществляемое непосредственно в .ходе самой команды приема информации, расширяет функциональные возможности устройства контроля. Наг: пример, уже на программном уровне можно осуществить повторный ввод ран нее принятого сглова. В случае работы с фотосчитывающим устройством это осуществляется путем поиска на перфоленте начала вводимого блока информации и последующего повторного ввода. Указанный режим характерен, в частности, для систем числового программного управления станками, осущест вляющих покадровый прием информации с перфоленты в процессе обработки детали. Эффект повышения быстродействия в предлагаемом устройстве обеспечивается следующими факторами.Во-первых, запись принимаемой информации сразу по двум адресам (определяемому регист ром адреса и фиксированному, определяемому блоком управления контролем) позволяет производить контроль принятой информации путем ее считывания из фиксированного адреса. При этом отпадает необходимость в последующем восстановлении этой информации. Во-вторых, программное разветвление, осуществляемое непосредственно в ходе команды приема, позволяет исключить из программ дополнительные команды условных переходов по результатам анализа принятого слова. Работа блока 7 модификации адреса происходит следующим образом. По сигналу начало контроля, поступающего с блока 8 управления контролем узел 10 контроля по четности про изводит контроль слова,принятого с чи ловой магистрали.В случае сбоя сигнал выхода схемы контроля четности поступает на первый вход элемента ИЛИ 9, на второй вход элемента ИЛИ 9 пос тупает с адресной магистрали младший разряд адреса. Сигналом с выхода элемента ИЛИ 9 производится запись в младший разряд РА. Если младший разряд кода адреса на втором вхо де элемента ИЛИ равен нулю, то появи шийся с выхода узла 10 контроля четности сигнал сбоя осуществляет модификацию адреса следующей команды, т.е. происходит условное разветвление в программе. Задавая в младшем разряде кода значение единицы, а не нуля, удается исключить модификацию даже в том случае, если имеется сбой в принятом слове. В качестве узла 10 контроля четности можно, например, использовать серийно выпускаемую интегральную микросхему контроля четности и нечетности КМ155ИП2. Блок 8 управления контролем работает следующим образом. При разрешающем сигнале Разрешение ввода , поступающем с блока 6 ввода, сигнал записи с выхода блока 5 синхрюнизации осуществляет возбуждение формирователя 12 адресного ток записи. При этом одновременно с записьго слова в адрес, определяемый регистром адреса, происходит запись этого же слова в фиксированный адрес. Фиксированность адреса обеспечивается за счет подключения Формирователя адресного тока ко вполне определенному адресу блока 1 памяти. С выхода элемента И 14 сигнал поступает на вход формирователя 15 задержки, который обеспечивает прохождение приходящего за данным тактом записи сигнала чтения через элемент И 13. С выхода элемента И 13 сигнал поступает на возбуждение формирователя 11 тока чтения, обеспечивая считывание информации из фиксированного адреса. Одновременно с этим сигнал с выхода элемента И 13 поступает в блок 7 модификации адреса, обеспечивая тем начало работы узла контроля по четности. Контроль, реализованный в предлагаемом устройстве, позволяет выявить не только те ошибки, которые имеют место в информации, поступающей из блока 6 ввода, но также и сбои, которые появляются в этой информации после прохождения тракта записирчитывания. Это становится особо актуальным в производственных условиях, для которых характерен большой уровень различных помех. Положительный эффект, создаваемый предлагаемым устройством, обусловлен тем, что контроль вводимой информации осуществляется после ее записи в блок памяти, а также возможностью организации условных переходов в программах в случае появления сбойных символов. Предлагаемое устройство входит в состав внедряемой в серийное производство системы ЧПУ металлорежущими станками, ввод информации в которую осуществляется при помощи восьмидорожечного фотосчитывающего устройства. Формула изобретения Устройство для контроля ввода-вывода , содержащее блок.памяти, регистр адреса, дешифратор адреса, регистр числа, блок синхронизации и блок ввода, причем группа информационных входов регистра адреса соединена с адресной магистралью, выход регистра адреса соединен со входом дешифратора адреса, выход которого соединен с адресным входом блока памяти, первый и второй, третий и четвёртый выходы блока синхронизации соединены соответственно с первым входом регистра адреса, первым и вторым входами блока памяти и входом регистра числа, выход которого соединен с разрядными входами блока памяти, выходы блока ввода, подключены к числовой магистрали, информационный вход регистpa числа и выход блока памяти подклю чены к числовой магистрали, информационные .и управляющие входы блока ввода являются соответственно информационным и первым управляющим входа ми устройства,отличающеес я тем/ что, с целью повышения быс родействия и расширения функциональных возможностей за счет обеспечения возможности ветвления программ при сбое ввода-вывода, в него введены блок модификации адреса и блок управ ления контролем, причем выход блока модификации адреса соединен со входом младшего разряда регистра адреса, младший разряд адресной магистрали соединен со входом блока модификации адреса,, информационный и управляющий входы которого соединены соответственно с числовой, магистраль первым выходом е5лока управления конт ролем, управляющий и синхронизационный входы записи и считывания блока управления контролем соединены соответственно с управляющим входом устройства, вторым и третьим выходами блока синхронизации, второй выход блока управления соединен с третьим входом блока памяти. 2. Устройство по п. 1, отличающееся тем, что блок модификации адреса содержит узел конт роля по четности и элемент ИЛИ, выхо которого является выходом блока, информационный и управляющий входы узла контроля по четности являются соответственно информационным и управляющим входами блока, выход узла контроля по четности соединен с первым входом элемента ИЛИ, второй вход.ко торого является входом блока. 3. Устройство по п. 1, отличающееся тем, что управление контролем содержит первый и второй элементы И, формирователь тока записи, формирователь тока считывания и формирователь задержки, причем синхронизационные входы считывания и записи блока соединены с первыми входами соответственно первого и второго элементов И, управляющий вход блока соединен со вторым входом второго элемента И, выход которого соединен со входами формирователя тока записи и формирователя задержки, выход формирователя задержки соединен со вторым входом первого элемента И, выход которого соединен со входом формирователя тока считывания и является первым выходом блока, выходы формирователя тока считывания и тока записи являются вторым выходом блока. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 318Э46, кл. G 06 F 11/10, 1972. 2.Патент США 3566093, кл. G 06 F 11/08, опублик. 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1987 |

|

SU1495849A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1310904A1 |

| Двухуровневое оперативное запоминающее устройство | 1982 |

|

SU1043742A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1985 |

|

SU1288709A1 |

| Устройство для обмена информацией | 1979 |

|

SU849193A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Запоминающее устройство для телевизионного изображения | 1985 |

|

SU1265785A1 |

| Буферное запоминающее устройство на полупроводниковых динамических элементах памяти | 1987 |

|

SU1525744A1 |

| Устройство для обмена данными между ЭВМ и периферийным устройством | 1987 |

|

SU1605240A1 |

fe./

15

..r

фиг

//

-I-

фиг.З

Авторы

Даты

1982-01-07—Публикация

1980-02-11—Подача