(54) УСТРОЙСГВО ДЛЯ УСТАНОВКИ ТРИГГЕРНЫХ СХЕМ В ИСХОДНОЕ СОСТОЯНИЕ

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СРЕДНЕКВАДРАТИЧЕСКОГО ЗНАЧЕНИЯ НАПРЯЖЕНИЯ | 1987 |

|

SU1438439A1 |

| Устройство формирования установочного импульса | 1982 |

|

SU1129725A1 |

| Преобразователь постоянного напряжения | 1983 |

|

SU1169108A1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ ПОНИЖАЮЩЕГО ТИПА | 1991 |

|

RU2006062C1 |

| Формирователь импульсов | 1985 |

|

SU1325674A1 |

| Одновибратор | 1982 |

|

SU1083348A1 |

| УСТРОЙСТВО ОХРАННОЙ СИГНАЛИЗАЦИИ | 1991 |

|

RU2031445C1 |

| Источник питания электроразрядных импульсных лазеров | 1983 |

|

SU1277358A1 |

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ЧАСТОТЫ | 2014 |

|

RU2565504C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2000 |

|

RU2178617C2 |

1

Изобретение относится к вычислительной технике и автоматике и может быть использовано при создании вычислительных устройств, работающих при сбоях питания.

Известны устройства для установки триггерных схем с использованием вспомогательных источников напряжения l .

Недостатком этих устройств является ограничение области применения вследствие необходимости дополнительного источника питаЕшя.

Известно также устройство для установки триггерных схем в исходное состояние, в котором используются интегрирующие цепи и делители на. резисторах, включенные по мостовой схеме С2.

Однако надежность работы этого устройства зависит от балансировки диагоналей мостовой схемы, а длительность импульса установки зависит от глубины провала питающего напряжения, вследствие чего известные устройства не реагируют.на кратковременные провалы питающего напряжения. А так как триггерные схемы уст- ройства автоматики и вычислительной техники могут произвольно переключиться, даже при кратковременных провалах питающего напряжения, то указанные недостатки могут привести к неправильному их функционированию

to и снижению надежности их работы.

Цель изобретения - повышение надежности работы устройства при кратковременных пропаданиях питающего напряжения.

IS

ПоставленнсШ цель достигается тем, что в устройство для установки триггерных схем в исходное состояние, содержащее два делителя на резисторах, где интегрирующие цепи,

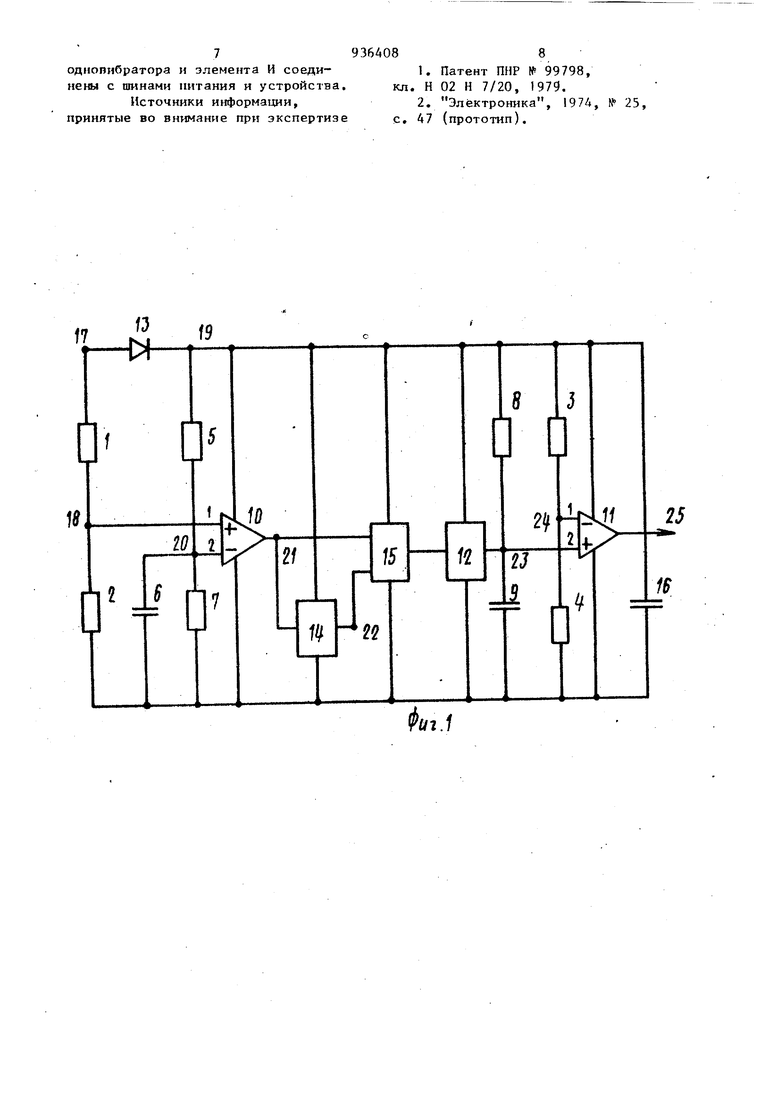

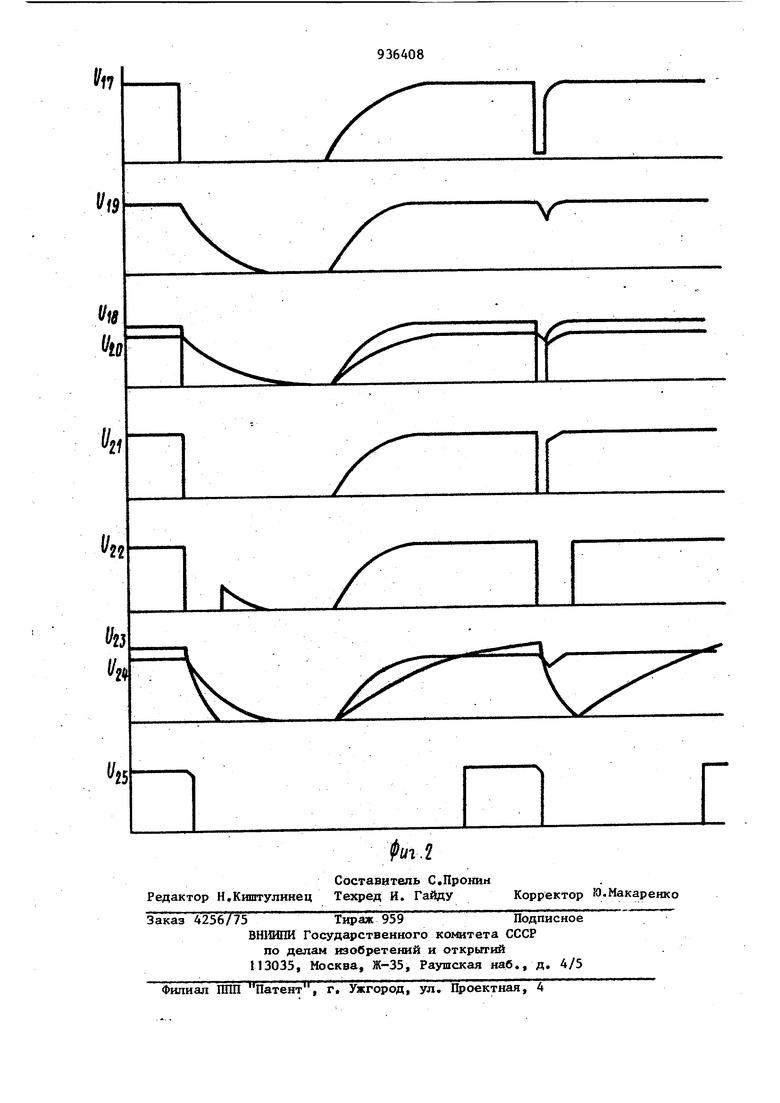

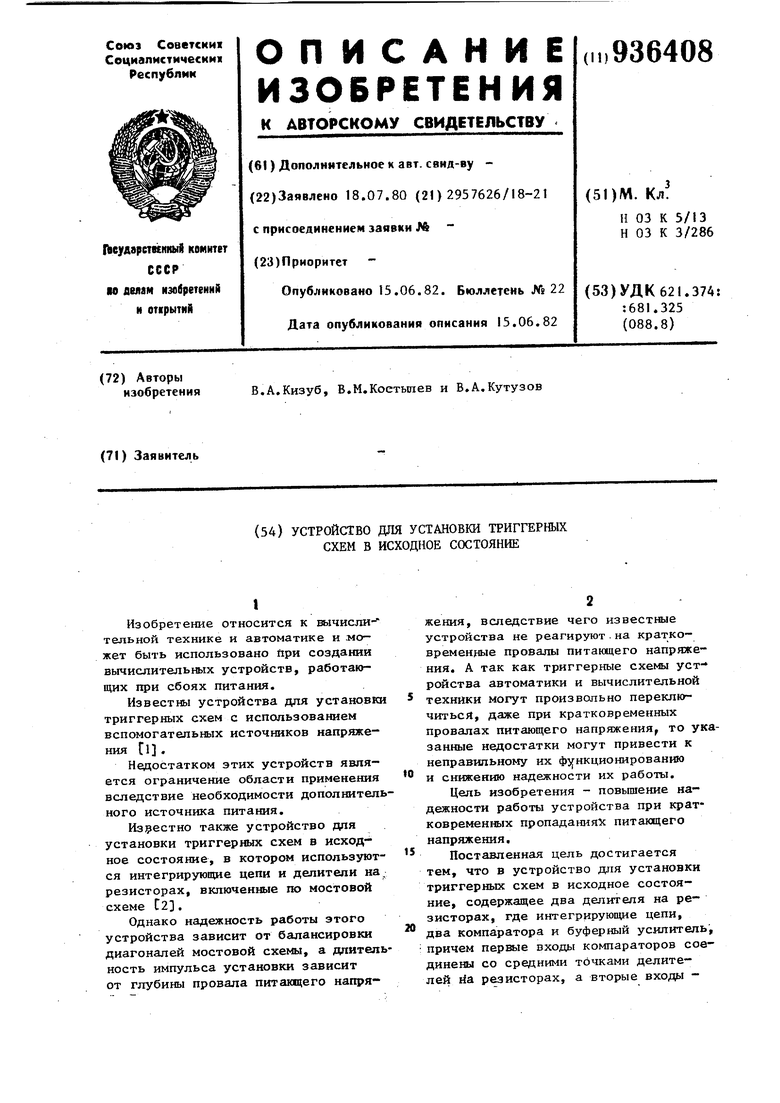

20 два компаратора и буферный усилитель, причем первые входы компараторов соединены со средними точками делителей резисторах, а вторые входы СО средней точкой интегрирующих цепей, выход буферного усилителя соединен со средней точкой второй интегрирующей цепи, шина питания компараторов и буферного усилителя соединена с резисторами интегрирумяцих цепей и первым резистором второго де лителя, а общая шина - с вторыми резисторами делителей, ковдеисатором второй интегрирующей цепи и с конде сатором зашунтированной резистором первой интегрирующей цепи, ваепены диод, одновибратор, элемент И и дополнительн 1й ковденсатор, при этом анод диода соединен с первым резистором первого делителя, а катод - с резистором первой интегрирующей цепи, вход одибвибратора и вхо элемента И, соединены с выходом первого компаратора, а выход одновибратора соединен с вторым входом элемента И, выход которого соединен с входом буферного усилителя, обкладка дополнительного конденсатора, шины питания одновибратора и элемента И соединены с шинами питаганя и устройства, . Ни фиг. I представле на схема устройства дли установки триггерных сх в исходное состояние; на фиг. 2 диаграммы, поясняющие работу устройства. . Устройство содержит резисторы I, 2, 3, 4 и 5, конденсатор 6, резистор 7 и 8, ковденсатор 9, компараторы 10 и П, буферный усилитель 12, диод 13, одновибратор 14, элемент 15, конденсатор 16. Позициями 17-25 обозначены точки схем, для которых приведены времен ные диаграммы, поясняющие работу устройства (фиг. 2). Первый вход компаратора 10 соеди нен с резисторами 1 и 2, второй вывод реЪистора I соединен с анодом диода 13. Второй вход компаратора 10 соединен с резисторами 5 и 7 и первой обкладкой конденсатора 6, второй вывод резистора 5 соединен с катодом диода 13, с первой шиной питания компараторов 10 и 11, одновибратора 14, элемента 15 И и буфер ного усилителя 12, второй вывод резистора 7 соединен со второй ойилад кой конденсатора 6, со вторым выводом резистора 2 и второй шиной пита ния компараторов 10 и 11 одновибратора 14, буферного усилителя 12 и элемента 15 И. Выход компаратора 10 соединен с первым входом элемента 15 И и входом одновибратора 14, выход которого соединен с вторым входом элемента 15 И. Выход элемента 15 И соединен с входом буферного усилителя 12, выход которого соединен с вторым входом компаратора II, резистором 8 и первой обкладкой конденсатора 9, Второй вывод резистора 8 соединен с первой шиной питания, а вторая обкладка конденсатора 9 - с второй шиной питания. Первый вход компаратора 11 соединен с резисторами 3 и 4, вторые BbiBOjCQd которых соединены соответственно с первой и второй шинами питания. Обкладка конденсатора 16 соединены с шинами питания. Устройство работает следующим образом. При нормальном питающем напряжении первый вход (плюс) компаратора 10 (фиг. 1) находится под высоким потенциалом относительно второго ( минус ) и на его выходе присутствуют высокий уровень напряжения, который поступает на первый вход элемента 15 И, на второй вход которого также поступает высокий уровень напряжения. В результате на выходе элемента 15 И присутствует высокий логический уровень, который подается на буферный усилитель 12. При этом выходной транзистор усилителя 12 заперт, а конденсатор 9 заряжен почти до напряжения питания, поэтому второй вход (плюс) компаратора 11 находится под высоким потенциалом относительно первого хода (минус) и на его выходе присутствует высокий логический уровень. Если цепь от источника питания, подключаемого к точке 17, прерывается, потенциал первого входа (плюс) компаратора 10 скачком понижается почти до нулевого уровня и становится ниже потенциала на втором входе (минус),Удерживаемого на высоком уровне конденсатором. В результате изменения злака разности м&жру входшдми напряжениями на выходе компаратора 10 происходит переключение сигнала с высокого на низкий уровень. При этом запускается одновибратор 14, вырабатывающий импульс низкого логического уровня длительностью, равной длительности полного разряда конденсатора 9 через открытый транзистор буферного усилителя 12. Присутствие низкого логического уровня на любом из выходов элемента 15 И открывает выходной транзистор буфер ного усилителя 12, Позтому при переключении сигнала на выходе компаратора 10 с высокого на низкий логический уровень происходит полный разряд коцценсатора 9 через открытый транзистор буферного усилителя 12. При восстановлении напряжения питания в точке 17 (в какой-бы момент времени оно не произошло) потенциал на первом плюс) входе компаратора 10.становится выше потенци ала на втором входе минус ) компаратора 10, и на его выходе появля ется высокий логический уровень, поступающий на первый вход злемента 15 И. Если при этом формирование им пульса низкого уровня формирователе 14окончено, то на выходе элемента 15И появляется высокий логический уровень. Выходной транзистор буферного усилителя 12 закрывается, и начинается заряд полностью разряжен ного конденсатора 9 через резистор Если, восстановление напряжения п тания в точке 17 происходит раньше, чем закончится разряд конденсатора 9, то импульс низкого уровня однови ратора 14 задержит переключение сиг- нала на выходе элемента 15 И на время, необходимое для полного разряда конденсатора 9. Импульс предварительной установки вырабатывается на выходе компаратора 1I во время зарядки конденсатора 9 через резистор 8. При восстановлении питания напряжение на делит ле, состоящем из резисторов 3 и- 4, возрастает быстрее, чем на конденсаторе 9, т.е. на первом входе (минус.) компаратора 11 во время заряда конденсатора 9 потенциал выше, чем на втором входе (плюс ) компаратора, поэтому на его выходе присутствует низкий логический уровень. После того, как конденсатор 9 зарядит-г ся, потенциал второго входа ( плюс ) компаратора 11 становится выше поте циала первого: входа, и на выходе компаратора I 1 устанавливается высокий логический уровень. Таким образом, сигнал на выходе компаратора 11 можно использовать в качестве сигнала первоначальной установки триггерных схем. Введение в устройство диода, одновибратора, элемента И и коцценсатора с соответствующими связями меяаду собой и известными .элемента ми cxeNej позволяют увеличить надежность работы устройства при кратковременных пропаданиях питающего напряжения . Устройство обеспечивает стабильный по длительности импульс установки независимо от глубины .провала и длительности пропадания питанщего напряжения. Использование предлагаемого устройства позволяет исключить возможность произвольного переключения триггерных схем, вследствие пропада1шя напряжения питания, т.е. увеличить достоверность, и надежность работы устройства автоматики и вычислительной техники. Формула изобретения Устройство для установки триггер- ных схем в исходное состояние, содержащее два делителя на резисторах, две интегрирукнцие цепи, два компаратора и буфермлй усилитель, причем первые входы компараторов соединены со средними точками делителей на резисторах, а вторые входы - со средней точкой интегрирую 191х цепей, выход буферного усилителя соединей со средней точкой второй интегрирующей цепи, шина питания компараторов и буферного усилителя соединена с резисторами интегрирующих цепей и первым резистором второго делителя, а общая шина - с вторыми резисторами делителей, конденсатором второй ИНТегрирукнцей цепи и с конденсатором зашунтированной резистором перой интегрирующей цепи, отличающееся тщ, что, с целью повьшсения надежности работы устройства, в него введены диод, одновибратор, элемент И и дополнительный конденсатор, при этом анод диода соединен с первым резистором первого делителя, а катод - с резистором первой интегрирующей цепи, вход одновибратора и первый вход элемента И соединены с выходом первого компаратора, а выход одновибратора соединен с вторым входом злемента И, выход которого соединен с входом буферного усилителя, обкладки дополнительного конденсатора, шины питания

79364088

одиопнбратора и элемента И соеди- 1. Патент ПНР № 99798, йены с шинами питания и устройства. кл. Н 02 Н 7/20 1979

Источники информации,2. Электроника, 1974, № 25

принятые во внимание при экспертизе с. 47 (прототип).

f7 Р, f9

25

Фиг.1

Vn

II,

2f

l.

n

936408

CM (/

Авторы

Даты

1982-06-15—Публикация

1980-07-18—Подача